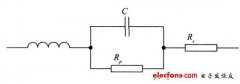

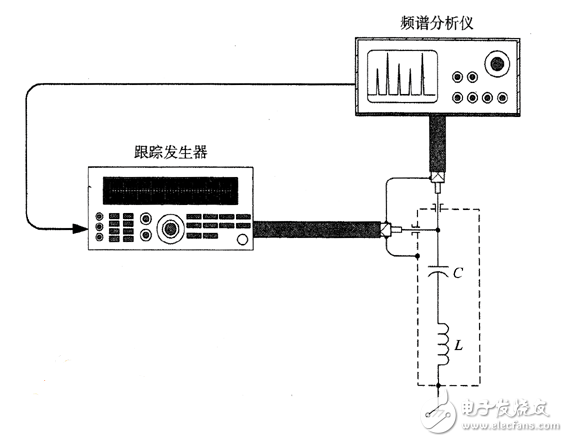

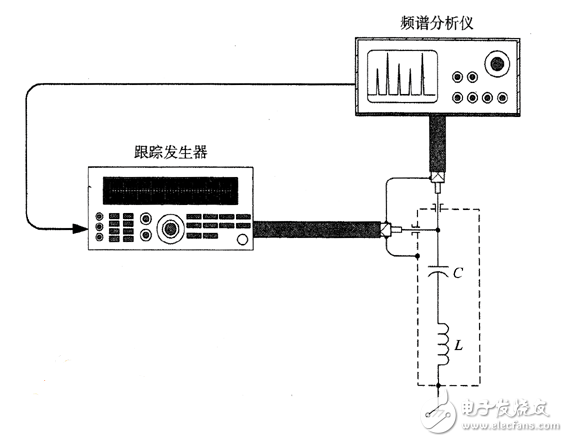

本文介紹了一種利用LC 諧振原理測量電容自身 寄生電感 的方法。利用直接數字合成器產生可編程的掃頻信號激勵含有寄生電感的電容,同時采用對數檢波器對經過待測網絡后的信號進

2011-10-24 11:49:07 2536

2536

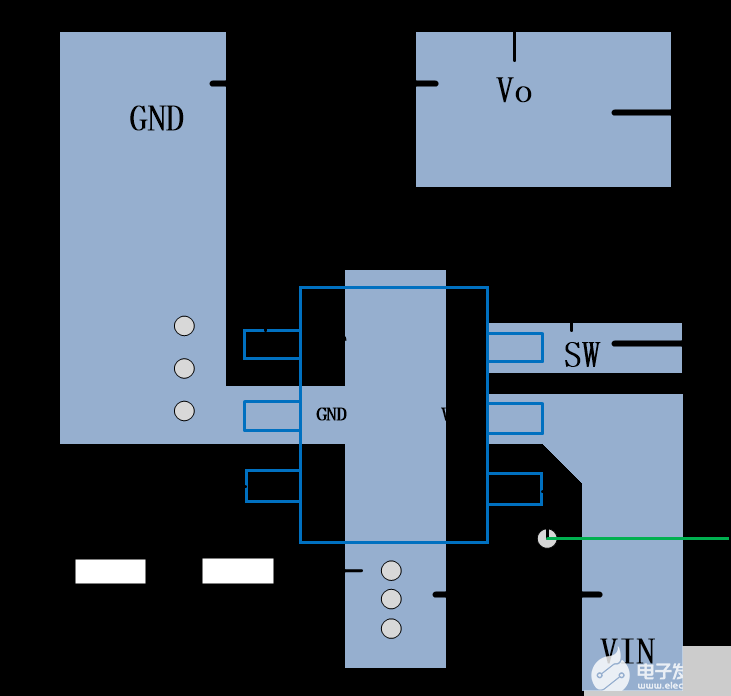

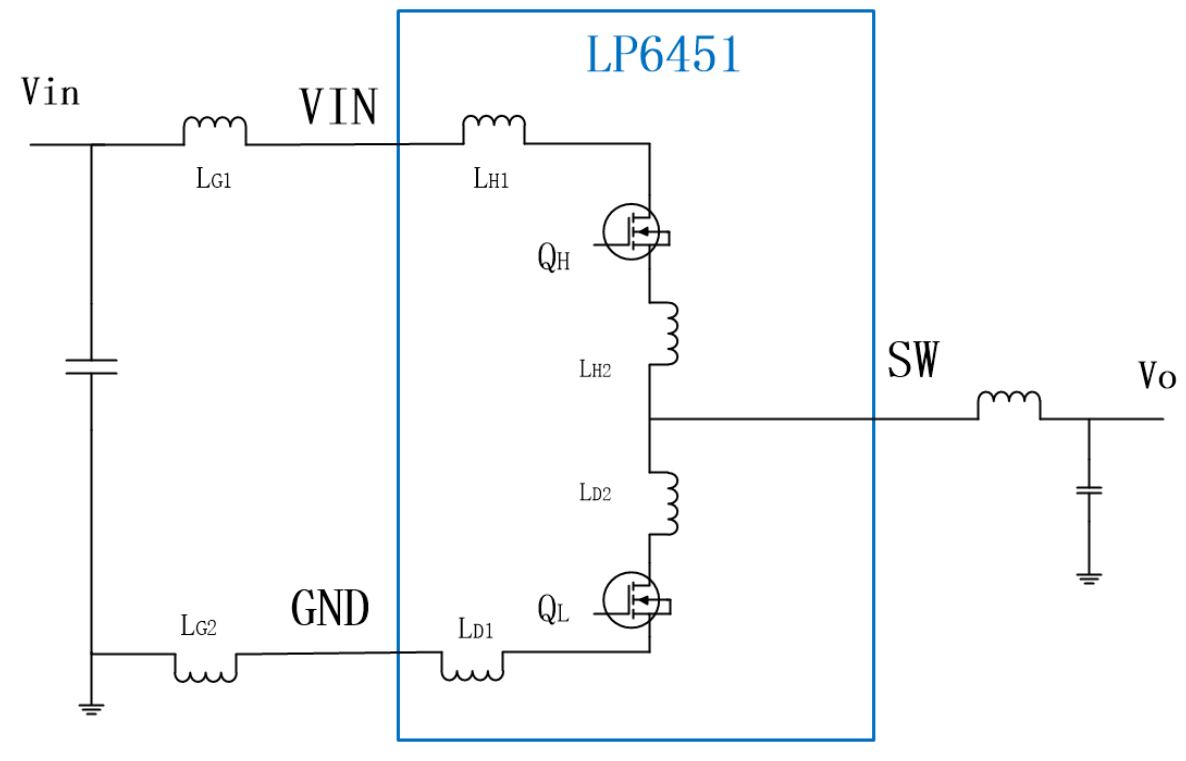

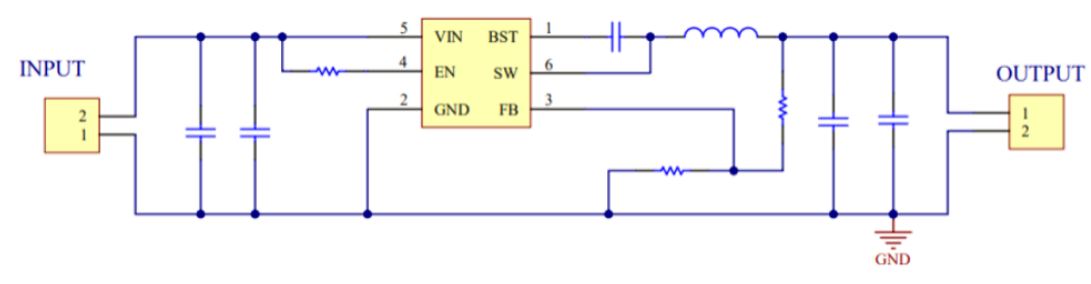

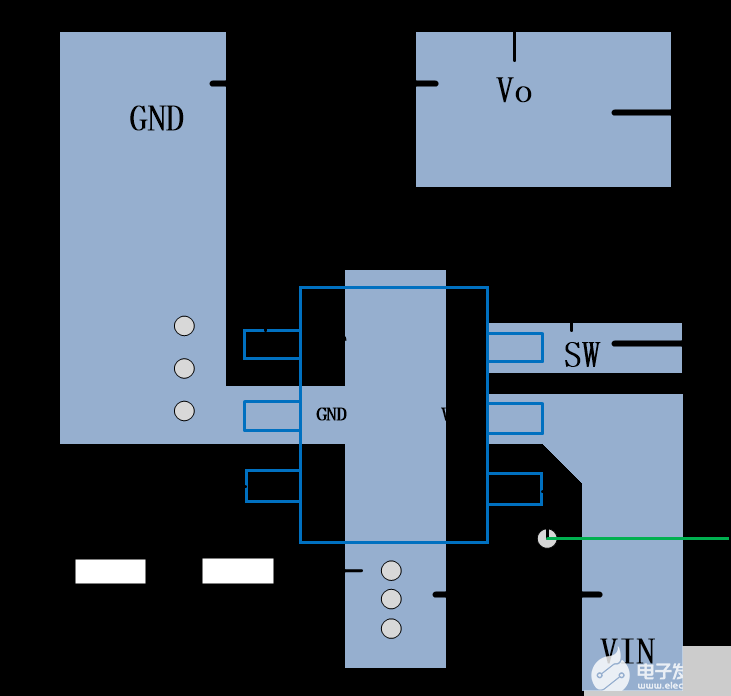

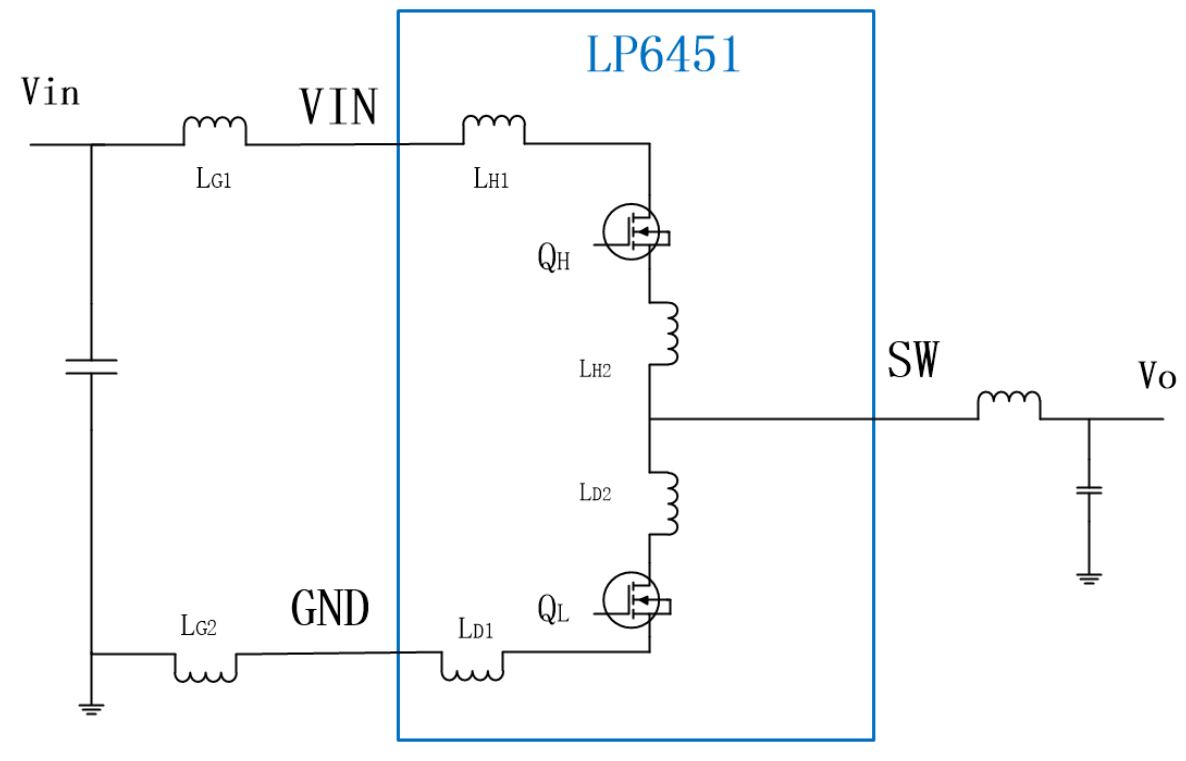

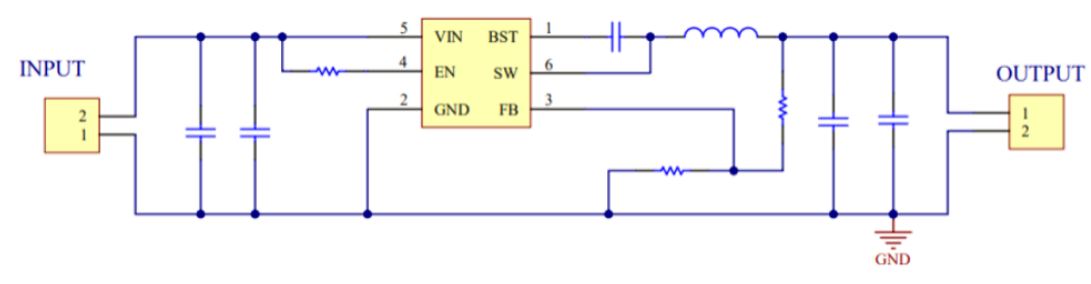

上期我們介紹了寄生電感對Buck電路中開關管的影響,本期,我們聊一下如何優化寄生電感對電路的影響。

2022-11-22 09:07:35 764

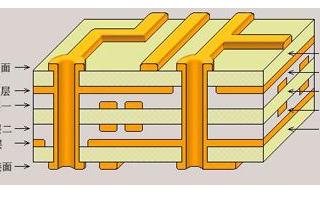

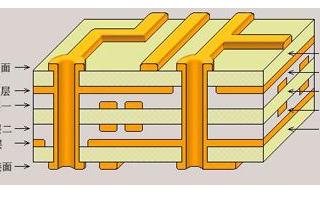

764 在PCB(PrintedCircuitBoard,印刷電路板)設計中,過孔寄生電感是一個重要的考慮因素。當電流通過PCB的過孔時,由于過孔的幾何形狀和布局,會產生一定的寄生電感。這種寄生電感可能會

2024-03-15 08:19:53 675

675

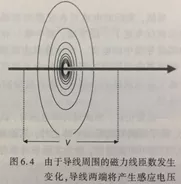

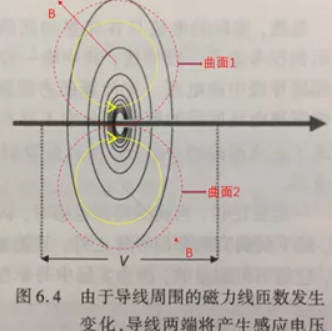

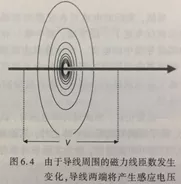

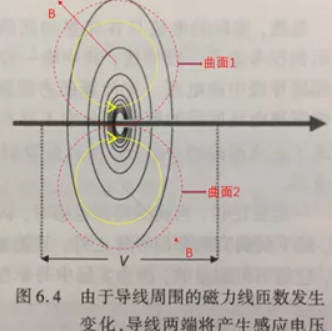

最近在整理電感的內容,忽然就有個問題不明白了:寄生電感怎么來的呢?一段直直的導線怎么也會存在電感,不是只有線圈才能成為電感嗎?想到以前看的書,這個寄生電感的存在大家都默認是有的,貌似也沒有人懷疑這個

2021-01-28 07:00:38

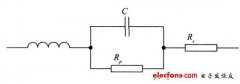

低頻下,所有三種電容器均未表現出寄生分量,因為阻抗明顯只與電容相關。但是,鋁電解電容器阻抗停止減小,并在相對低頻時開始表現出電阻特性。這種電阻特性不斷增加,直到達到某個相對高頻為止(電容器出現電感)。鋁聚合物電容器為與理想狀況不符的另一種電容器。

2019-08-15 06:33:32

:波形隨連續反激或者降壓輸出電流而變化總之,輸出電容器的阻抗有助于提高紋波和瞬態性能。隨著電源頻率升高,寄生問題的影響更大、更不應忽視。在20kHz附近,鋁電解電容器的ESR大到足以主導電容阻抗。在100kHz時,一些鋁聚合物電容表現出電感。電源進入兆赫茲開關頻率時,請注意所有三種電容器的ESL。

2018-09-29 09:22:17

寄生電容一般是指電感,電阻,芯片引腳等在高頻情況下表現出來的電容特性。實際上,一個電阻等效于一個電容,一個電感,和一個電阻的串聯,在低頻情況下表現不是很明顯,而在高頻情況下,等效值會增大,不能忽略。

2019-09-29 10:20:26

寄生電容的影響是什么?焊接對無源器件性能的影響是什么?

2021-06-08 06:05:47

射頻VMMK器件是怎么提高性能的?通過降低寄生電感和電容嗎?

2019-08-01 08:23:35

射頻電路中為什么電容都是pF,電感都是nH ?為什么100pF就相當通路?電感越大,感抗就越大?電感盡量取小嗎,電容呢。

2019-02-20 14:21:09

%的磁通泄漏,有效的提升EMI性能射頻設計難題「電源退耦篇」電源供電需要通過退耦電容濾除電源的噪聲,如圖,避免噪聲在不同設備(IC)之間流轉,同時電源噪聲會增加頻率合成器的相位噪聲,降低接收機的接收

2022-11-07 20:48:45

電容器的雜散電感和寄生電感的區別是什么?

2023-04-11 16:59:39

的輸出電容及電容本身的寄生串聯電阻會影響到穩壓器的輸出電路的性能以及當負載突變時穩壓器的瞬態響應能力。通常,輸出電容應首選: 一,有較小等效串聯電阻(ESR)的電容, 以便降低交流損耗和輸出紋波; 二

2017-09-02 01:49:18

器件越遠。在RF頻率下,電路板背面的電容器會產生通孔串連接地路徑的寄生電感,損失大量噪聲衰減優勢。總結通過電路板布局評測,我們可發現可能發射或接收雜散RF音調的結構。要跟蹤每一條線路,有意識地明確其回流

2017-01-20 15:50:55

如何實現高性能的射頻測量系統? 高性能射頻測量系統該怎么正確選用阻抗匹配元件?在設計PCB裝配式開關模塊時需要考慮什么?

2021-04-14 06:46:36

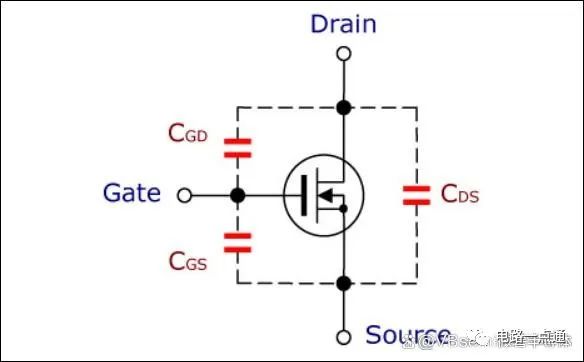

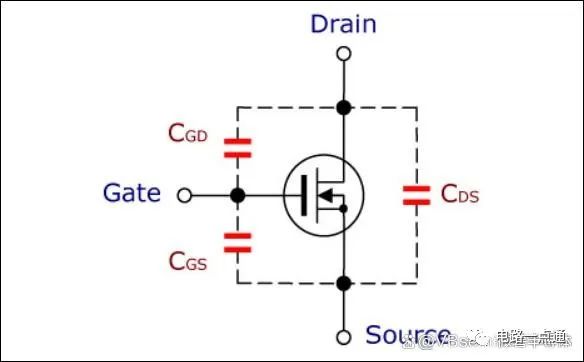

MOSFET的工作波形。由于感性負載下,電流相位上會超前電壓,因此保證了MOSFET運行的ZVS。要保證MOSFET運行在感性區,諧振電感上的諧振電流必須足夠大,以確保MOSFET源漏間等效的寄生電容上存儲

2018-11-21 15:52:43

,需要更長的LLC諧振周期和釋放時間。因此選擇合適的MOSFET(足夠小的等效寄生電容),對于ZVS的實現至關重要,尤其是當Vds接近于0的時候,等效輸出電容要足夠小,這樣還可以進一步降低死區時間并提高

2018-07-13 09:48:50

布局和互連線帶來)等寄生效應的半橋電路。共源電感(CSI)傾向于降低控制FET(高邊FET)的導通和關斷速度。如果與柵極驅動串聯,通過CSI的電壓加至柵極驅動上,可使FET處于導通狀態(條件:V

2019-05-13 14:11:31

寄生效應方面,例如無芯片封裝電阻(DFPR)和封裝電阻,它們會導致功率損耗并在電流額定值和開關速度方面限制器件的性能。 封裝接合線和引線框上不必要的電感使得柵極上會維持一定的電壓,從而阻止柵極驅動器

2018-09-12 15:14:20

的寄生信號也會阻礙產品的發布。寬帶器件支持軟件定義無線電(SDR)的這一當前趨勢將進一步強調降低寄生信號的重要性。由于可部署統一信號平臺設計來滿足多種頻帶需求,因此插入式RF模塊可替代其中較多信號可能會

2019-06-21 06:06:13

導讀:近日,TT electronics 宣布推出新一代模壓電感 器件--HM72E/A72E.該兩款器件具有高性能和高成本效益,最大限度地減少了氧化。 該兩款器件是專為需要降壓、升壓或

2018-09-26 15:44:31

寄生電容是指電感,電阻,芯片引腳等在高頻情況下表現出來的電容特性。實際上,一個電阻等效于一個電容,一個電感,一個電阻的串聯,低頻情況下表現不明顯,而高頻情況下,等效值會增大。在計算中我們要考慮

2021-01-11 15:23:51

相同,電感的高頻特性同樣與理想電感的預期特性不同,如下圖所示:首先,當頻率接近諧振點時,高頻電感的阻抗迅速提高;第二,當頻率繼續提高時,寄生電容C的影響成為主要的,線圈阻抗逐漸降低。電感阻抗絕對值與頻率

2018-07-17 23:01:07

之一。圖3:波形隨連續反激或者降壓輸出電流而變化 總之,輸出電容器的阻抗有助于提高紋波和瞬態性能。隨著電源頻率升高,寄生問題的影響更大、更不應忽視。在20kHz附近,鋁電解電容器的ESR大到足以主導電容阻抗

2022-04-30 21:37:23

器件的柵極、源極,LD為漏極的封裝電感,LS為源極的封裝電感,LG為柵極的封裝電感,RG為內部的柵極電阻總和。 圖1:功率MOSFET的寄生參數模型 電感中流過變化的電流時,其產生的感應電

2020-12-08 15:35:56

`從零學運放—09電阻電容電感被動器件前面我們講了運放的相關知識,實際當中運放變化也就這么都。通常我們把運放加上一些外圍器件組成電路,之后再做成PCB制板調試出來,整個過程中會碰到很多困難。比如

2017-05-03 09:26:54

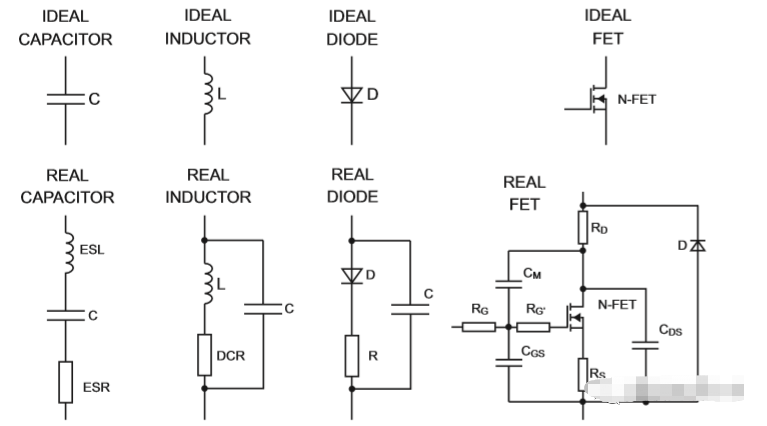

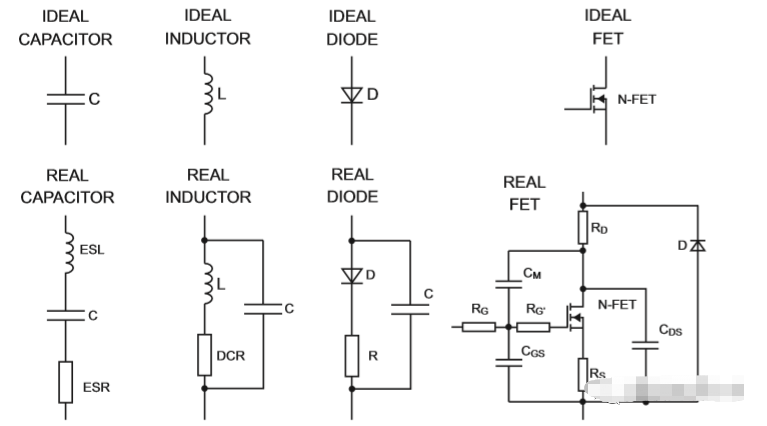

在理想電感器中,阻抗隨著頻率的提高而呈線性增加,但在實際的電感器中,如等效電路所示,并聯存在寄生電容EPC,因而會產生自諧振現象。

2019-08-13 06:24:35

相同,電感的高頻特性同樣與理想電感的預期特性不同,如下圖所示:首先,當頻率接近諧振點時,高頻電感的阻抗迅速提高;第二,當頻率繼續提高時,寄生電容C的影響成為主要的,線圈阻抗逐漸降低。電感阻抗絕對值與頻率

2018-07-19 16:49:21

相同,電感的高頻特性同樣與理想電感的預期特性不同,如下圖所示:首先,當頻率接近諧振點時,高頻電感的阻抗迅速提高;第二,當頻率繼續提高時,寄生電容C的影響成為主要的,線圈阻抗逐漸降低。電感阻抗絕對值與頻率

2018-07-26 11:19:59

我上murata官網看了半天電容的datasheet,他就說自己是低寄生電感,具體多低,也沒說清楚。是我自己沒找到還是datasheet里原本就沒?如果沒有的話,寄生電感的數值只能瞎猜嗎?

2019-12-28 16:39:18

:波形隨連續反激或者降壓輸出電流而變化總之,輸出電容器的阻抗有助于提高紋波和瞬態性能。隨著電源頻率升高,寄生問題的影響更大、更不應忽視。在20kHz附近,鋁電解電容器的ESR大到足以主導電容阻抗。在100kHz時,一些鋁聚合物電容表現出電感。電源進入兆赫茲開關頻率時,請注意所有三種電容器的ESL.

2018-09-10 08:16:02

可滿足高性能數字接收機動態性能要求的ADC和射頻器件有哪些?

2021-05-28 06:45:13

/200010060034_1235.HTML。減小矩形芯片電感的一個有效方式就是改進芯片縱長方向端頭的設計。所選0603B152K500NT電容器的阻抗曲線如圖4所示。注意通過改變縱橫比,寄生電感減小了大約50

2011-06-15 17:01:00

如何提高VMMK器件的性能?

2021-05-21 06:35:39

元器件的合理布局提高敏感器件的抗干擾性能

2021-02-19 07:05:29

通過FPGA來構建一個低成本、高性能、開放架構的數據平面引擎可以為網絡安全設備提供性能提高的動力。隨著互聯網技術的飛速發展,性能成為制約網絡處理的一大瓶頸問題。FPGA作為一種高速可編程器件,為網絡安全流量處理提供了一條低成本、高性能的解決之道。

2019-08-12 08:13:53

如何去設計一款高性能的PHS射頻收發器芯片?

2021-06-01 06:50:52

對于各種不同的數據中心工作負載,FPGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2019-10-10 07:46:05

如何實現高性能的射頻測試解決方案NI軟硬件的關鍵作用是什么

2021-05-06 07:24:55

,一個原因是電容引線電感造成電容諧振,對高頻信號呈現較大的阻抗,削弱了對高頻信號的旁路作用;另一個原因是導線之間的寄生電容使高頻信號發生耦合,降低了濾波效果。穿心電容之所以能有效地濾除高頻噪聲,是因為

2016-09-01 14:02:38

I.引言 高效率已成為開關電源(SMPS)設計的必需要求。為了達成這一要求,越來越多許多功率半導體研究人員開發了快速開關器件,舉例來說,降低器件的寄生電容,并實現低導通電阻,以降低開關損耗和導

2018-10-08 15:19:33

射頻/微波器件的封裝設計非常重要,封裝可以保護器件,同時也會影響器件的性能。因此封裝一定要能提供優異的電學性能、器件的保護功能和屏蔽作用等等。高性能射頻微波器件通常采用陶瓷封裝材料,陶瓷材料的介電

2019-08-19 07:41:15

用高性能的FPGA器件設計符合自己需要的DDS電路有什么好的解決辦法嗎?

2021-04-08 06:23:09

怎樣去設計射頻電路?提高射頻電路性能的措施有哪些?如何對射頻電路性能進行測試?

2021-05-12 07:12:22

數據的高速傳輸成為必然。而怎樣才能在保護接口安全的同時保證數據的高速傳輸,已然成為高頻數據接口面對的難題。高速數據傳輸接口電路保護的主要困難是,保護器件的過大寄生電容會造成一定程度的信號衰減,從而降低顯示質量

2020-11-11 11:28:01

有什么方法可以降低微波/射頻器件的成本嗎?

2021-05-25 06:49:40

`磁芯對電感寄生電容的影響`

2012-08-13 15:11:07

`磁芯對電感寄生電容的影響`

2012-08-14 09:49:47

;Verdana">磁芯對電感寄生電容的影響分析</font></strong&

2009-12-23 16:07:01

如何用一種能夠遠程或者通過一個大寄生電容降低光電二極管帶寬和噪聲影響的電路?

2021-04-06 07:39:35

噪聲的傳導回路面積較大,進一步推動輻射發射的產生。在第 3 部分中,我將全面介紹降壓穩壓器電路中影響 EMI 性能和開關損耗的感性和容性寄生元素。通過了解相關電路寄生效應的影響程度,可以采取適當的措施將

2020-11-03 07:54:52

,由于附加的功能模塊產生的電容太大,似乎也無能為力。通用附件功能接入法,正反向接入法,可降低寄生電容。正向接入和反向接入只能是單方向的,不能解決所有情況,也就是說只能針對特殊的功能模塊。如要雙方向,則正反向接入法結合就起到作用。飛捷士對二極管頗有研究,針對性能,品質方面得到認可。

2020-12-15 15:48:52

,而2.2uF的電容則會過一段時間才響應,即便小電容離IC遠一些,只要它的寄生電感(包括引線和悍盤電感)比大電容小,那么它依然是瞬間電流的主要提供者。所以,高速設計中的關鍵就是高頻小電容的處理,要盡

2020-12-16 16:55:37

高速信號PCB布線中降低寄生電感的具體措施

2021-03-08 08:49:46

鐵氧體電感器在較高頻率時可等效為“電阻、電感”的串聯支路與一寄生電容的并聯,該電容的存在對電感器的高頻性能有重要影響。本文建立了鐵氧體環形電感器2D平行平面場和3D

2009-04-08 15:45:17 66

66 利用PCB 線圈消除濾波電容器的寄生電感

摘要:電源系統中,EMI 濾波器是抑制電磁干擾的重要部件,但是其高頻性能受限于元器件的寄生效應。本文針對差模

2009-11-16 11:38:37 32

32 電源系統中,EMI 濾波器是抑制電磁干擾的重要部件,但是其高頻性能受限于元器件的寄生效應。本文針對差模濾波電容,設計一種PCB 耦合線圈消除其寄生電感,以此改善電容器濾波

2010-02-18 13:08:03 37

37

數字接收機中高性能ADC和射頻器件的動態性能要求

今天的基站系統不得不

2006-05-07 13:41:54 1369

1369 如何應對電路板寄生組件對電路性能的干擾

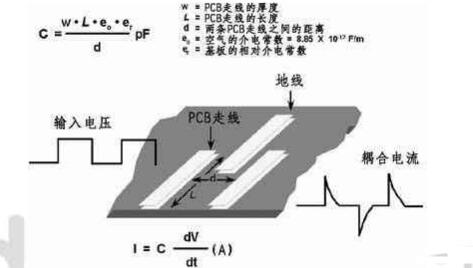

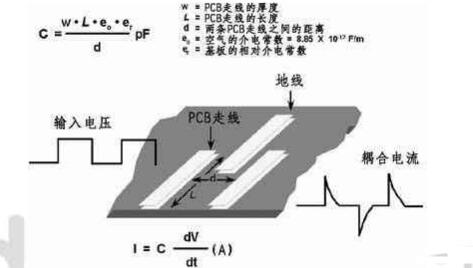

電路板布線所產生主要寄生組件分別是電阻、電容以及電感。從電路圖轉成實際電

2009-11-17 13:59:00 638

638 寄生電容,寄生電容是什么意思

寄生的含義 寄身的含義就是本來沒有在那個地方設計電容,但由于布線構之間總是有互容,互

2010-03-23 09:33:55 2557

2557 VMMK器件晶圓等級和芯片封裝工藝 如圖1所示,VMMK器件由于安華高特有的晶圓空腔工藝降低了損耗和常見的射頻表貼封裝帶來的寄生電路參數。通過消除焊接和封裝引腳之間的寄生電感和電容,在芯片和封裝

2017-11-09 11:05:38 0

0 1. 概述 RSM高性能射頻開關矩陣是基于高穩定性、高可靠性、高性能指標的射頻開關研制而成,工作頻率高達9GHz,可以廣泛應用于矢量網絡分析儀、手機終端綜測 儀的端口擴展,實現多端口器件的自動化測試

2017-11-09 10:56:06 7

7 寄生電容一般是指電感,電阻,芯片引腳等在高頻情況下表現出來的電容特性。實際上,一個電阻等效于一個電容,一個電感,和一個電阻的串連,在低頻情況下表現不是很明顯,而在高頻情況下,等效值會增大,不能忽略。

2018-01-31 10:57:56 26011

26011 電容的寄生電感和寄生電阻主要是指它的引線和極板形成的電感和電阻,尤其是容量較大的電容更為明顯。如果你解剖過電容器,會看到它的極板是用長達1米的金屬薄膜卷曲而成的,其層狀就像一個幾十、甚至上百圈的線圈

2018-01-31 13:44:55 37300

37300

如圖1所示,VMMK器件由于安華高特有的晶圓空腔工藝降低了損耗和常見的射頻表貼封裝帶來的寄生電路參數。通過消除焊接和封裝引腳之間的寄生電感和電容,在芯片和封裝間形成了一個低損耗和低阻抗的信號通道。

2018-05-07 14:59:00 2074

2074

本文開始闡述了寄生電感的概念和和寄生元件危害,其次闡述了寄生電感測量儀的設計和寄生電感產生原因或產生方式,最后介紹了PCB過孔的寄生電容和電感的計算以及使用。

2018-03-28 14:50:42 39049

39049

與傳統FPGA架構相比,UltraScale架構引入了許多創新,可提高性能并降低功耗。

在本視頻中,我們將重點介紹路由,邏輯和實現軟件的增強功能......

2018-11-22 06:45:00 3056

3056 減小電感寄生電容的方法

如果磁芯是導體,首先:

用介電常數低的材料增加繞組導體與磁芯之間的距離

2019-07-18 08:00:00 1

1 您可以估算具有固態電源和接地層的多層電路板中旁路電容的寄生串聯電感。由于芯片布局,使用電感 L 1 的近似值(圖1,綠色)陰影區域)。然后,假設您已將芯片和旁路電容直接連接到平面,請使用電感的近似值

2019-08-08 10:28:47 2391

2391

寄生電感一半是在PCB過孔設計所要考慮的。在高速數字電路的設計中,過孔的寄生電感帶來的危害往往大于寄生電容的影響。它的寄生串聯電感會削弱旁路電容的貢獻,減弱整個電源系統的濾波效用。我們可以用下面的公式來簡單地計算一個過孔近似的寄生電感。

2019-10-11 10:36:33 19063

19063 如圖1所示,VMMK器件由于安華高特有的晶圓空腔工藝降低了損耗和常見的射頻表貼封裝帶來的寄生電路參數。通過消除焊接和封裝引腳之間的寄生電感和電容,在芯片和封裝間形成了一個低損耗和低阻抗的信號通道。在元件之上的空腔具有低介電常數因此能夠在高頻進行工作,此外空腔能夠在器件應用中提供機械保護。

2020-08-21 18:50:00 0

0 寄生的含義就是本來沒有在那個地方設計電容,但由于布線之間總是有互容,互容就好像是寄生在布線之間的一樣,所以叫寄生電容,又稱雜散電容。

2020-09-17 11:56:11 27667

27667 最近在整理電感的內容,忽然就有個問題不明白了:寄生電感怎么來的呢?一段直直的導線怎么也會存在電感,不是只有線圈才能成為電感嗎?

2022-02-12 09:22:59 3476

3476

本來沒有在那個地方設計電容,但由于布線之間總是有互容,互容就好像是寄生在布線之間的一樣,所以叫寄生電容 寄生電容: 本質上還是電容,滿足i=c*du/dt。 電容是用來衡量儲存電荷能力的物理量。根據

2022-07-27 14:23:55 15291

15291

降低 TSPD 器件電容的選項

2022-11-15 19:17:05 0

0 在實際電路中,寄生電感最主要的來源是PCB上的走線以及過孔,PCB板上的走線長度越長,過孔的深度越大,寄生電感就越大。

2022-12-28 18:05:49 2008

2008

在電路設計中每個器件都有其寄生參數。例如,一個電感中還存在容性和阻性分量,電容中還存在感性和阻性分量。

2023-04-08 11:43:27 831

831

理想的電感,其電抗為jwL,即會隨著頻率的升高而升高,但是實際的電感,由于寄生電容的影響,這個寄生電容會與電感諧振,從而在某個頻率處產生一個很高的阻抗。

2023-06-09 14:29:31 1703

1703

電子發燒友網站提供《Avago射頻VMMK設備提高性能通過減少寄生電感和電容.pdf》資料免費下載

2023-07-20 10:15:06 0

0 如何減少導線的寄生電感?? 引言: 隨著電子設備的廣泛應用,對于高速數據傳輸和高頻信號的傳輸要求也越來越高。然而電學特性的限制使得對導線的寄生電感逐漸成為制約高頻電路性能的瓶頸之一。降低寄生電感

2023-09-05 17:29:31 3211

3211 如何減輕米勒電容所引起的寄生導通效應?? 米勒電容是指由電路中存在的電感所形成的電容。它可以導致電路中的寄生導通效應,從而影響電路的性能。常見的一種解決方法是使用補償電容,但這么做也會帶來其他

2023-09-05 17:29:39 977

977 寄生電容對MOS管快速關斷的影響 MOS(Metal Oxide Semiconductor)管是一種晶體管,它以其高性能和可靠性而廣泛應用于許多電子設備,如功率放大器和開關電源。盡管MOS管具有

2023-09-17 10:46:58 1242

1242 寄生電感的影響

2023-11-29 16:32:26 328

328

寄生電感的介紹

2023-11-29 16:41:12 815

815

射頻電容和電感值通常以皮法(picofarad,簡寫為pf)和納亨(nanohenry,簡寫為nh)為單位,這是因為射頻電路中的頻率相當高,因此需要使用這樣的單位來表示電容和電感的特性。在這

2023-12-29 10:44:47 385

385 寄生電容和寄生電感是指在電路中存在的非意圖的電容和電感元件。 它們通常是由于電路布局、線路長度、器件之間的物理距離等因素引起的。

2024-02-21 09:45:35 245

245

從式中可以看出:過孔的直徑對寄生電感的影響較小,而長度才是影響寄生電感的關鍵因素。所以,在設計電路板時,要盡量減小過孔的長度,以提高電路的性能。

2024-02-27 14:28:57 160

160

電子發燒友App

電子發燒友App

評論