性能浮點處理一直與高性能CPU相關聯。在過去幾年中,GPU也成為功能強大的浮點處理平臺,超越了圖形,稱為GP-GPU(通用圖形處理單元)。

2015-07-31 09:45:20 1696

1696

高性能浮點處理一直與高性能CPU相關聯。在過去幾年中,GPU也成為功能強大的浮點處理平臺,超越了圖形,稱為GP-GPU(通用圖形處理單元)。新創新是在苛刻的應用中實現基于FPGA的浮點處理。本文

2018-01-16 08:53:11 5988

5988

基于FPGA實現各種設計的首要前提是理解并掌握數字的表示方法,計算機中的數字表示方法有兩種:定點數表示法和浮點數表示方法。

2022-10-10 10:30:16 1120

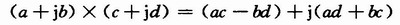

1120 ; 12.3e81230000000.03. 復數(Complex)復數由實數部分和虛數部分構成,可以用a + bj,或者 complex(a,b) 表示,復數的實部a和虛部b都是浮點型。關于復數,不做科學計算或其它特殊需要,通常很難

2022-02-17 18:09:09

FPGA 如何進行浮點運算

2015-09-26 09:31:37

FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現

2012-08-11 18:10:11

最近出現的 FPGA設計工具和 IP有效減少了計算占用的資源,大大簡化了浮點數據通路的實現。而且,與數字信號處理器不同, FPGA能夠支持浮點和定點混合工作的 DSP數據通路,實現的性能超過

2019-08-13 06:42:48

當我嘗試在FPGA編輯器中打開設計時,該過程將被浮點異常終止。當我第一次打開fpga編輯器然后使用打開文件對話框打開.ncd文件并從ISE啟動FPGA編輯器時,就會發生這種情況。我在i686

2018-10-09 15:33:17

了一系列優化算法,但是用戶仍有必要遵循一定的編碼風格去引導 綜合工具在特定 FPGA 架構上達到最優結果。 設計規劃用于指導用戶把設計更好地適配到所選用的 FPGA上并合理地 平衡面積和速度的要求,目的

2022-09-29 06:12:02

FPGA設計之浮點DSP算法實現,DSP算法是很多工程師在設計過程中都會遇到的問題,本文將從FPGA設計的角度來講解浮點DSP算法的實現。FPGA設計之浮點DSP算法實現是賽靈思工程師最新力作,資料不可多得,大家珍惜啊1FPGA設計之浮點DSP算法實現[hide][/hide]

2012-03-01 15:23:56

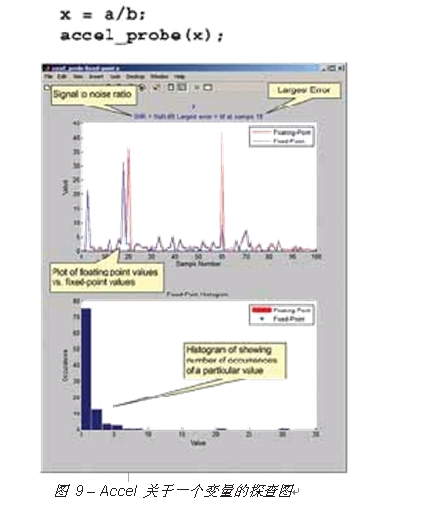

因使用HDL仿真器耗大量時 間。系統級設計和驗證工具(如MATLAB和Simulink)通過在FPGA上快速建立算法原型,可以幫助工程師實現這些優勢。本文將介紹使用MATLAB和Simulink創建

2020-05-04 07:00:00

1、在FPGA中實現串口協議的設計在FPGA中實現串口協議,通過Anlogic_FPGA開發板上的“UART2USB”口接收從計算機發來的數據。實驗設計思路UART串口是一種類似于USB、VGA

2022-07-19 11:09:48

復數浮點FFT說明資料,第30章 STM32F407復數浮點FFT(支持單精度和雙精度)本章主要講解復數浮點FTT,支持單精度和雙精度。目錄30.1 初學者重要提示30.2 復數浮點FFT說明

2021-08-10 06:37:09

那樣實現,因為浮點處理必須總是在沒有FPU的PIC上的軟件中進行……所以最好知道這一點,因為這個新板將要與之交談的另一個板也會發送一些浮點,而帶有IAR編譯器的68HC11確實使浮點大端點。(在將

2019-11-06 13:22:20

STM32F429復數浮點FFT(支持單精度和雙精度),第30章 STM32F429復數浮點FFT(支持單精度和雙精度)本章主要講解復數浮點FTT,支持單精度和雙精度。目錄30.1 初學者重要提示

2021-08-10 08:05:38

是否可以在arm系統中進行系統優化呢?個人經驗是可以進行優化,只是有限制。先說說自己的經驗,公司有一款測試gps的設備,本來是使用fpga分析空間點。不過老板認為我們公司自己的四核芯片也很強大,想把

2015-12-30 14:33:38

每一個元素都是復數,類似這樣的-59.4184087630243-2.62712122987465i。 小弟想實現這個Levinsondurbin的功能仿真,首先把向量實部虛部給導入,該怎么操作這樣的浮點數變成有符號的二進制表示呢。

2020-07-21 16:10:48

:{real[0], imag[0], real[1], imag[1],………………} ,在使用中切記不要搞錯。30.1.2浮點浮點復數FFT使用了一個混合基數算法,通過多個基8與單個基2或基4算法實現

2015-07-03 14:27:56

第32章實數FFT的實現 本章主要講解實數的浮點和定點Q31,Q15的實現。關于這部分的知識點和函數的計算結果上,官方的文檔有一些小錯誤,在章節中會跟大家詳細講述,還有一個要注意的問題,調用實數

2015-07-06 11:29:10

處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號

2019-07-05 06:21:42

本文闡述了Spartan-3 FPGA針對DSP而優化的特性,并通過實現示例分析了它們在性能和成本上的優勢。

2019-10-18 07:11:35

方案如圖4所示。這是一個功能正確的應用實現方案,但沒有進行任何性能優化或為充分利用FPGA架構的功能進行考慮。因此該代碼在SDAccel中編譯完成后,在Alpha Data卡上運行得到的最大吞吐量僅為

2019-06-19 07:27:40

您好,我是一個使用您的產品CyKIT-050開發工具包的客戶。我想在這種芯片上做一些浮點運算。我可以運行你的演示項目,如ADCYDAC,液晶顯示器等。然而,當實現Y=log(x)的程序時,編譯器顯示

2019-05-16 14:12:48

處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號

2019-08-15 08:00:45

高性能浮點處理一直與高性能CPU相關聯。在過去幾年中,GPU也成為功能強大的浮點處理平臺,超越了圖形,稱為GP-GPU(通用圖形處理單元)。新創新是在苛刻的應用中實現基于FPGA的浮點處理。

2019-10-21 08:15:23

想用FPGA來實現PID控制,計算部分用浮點數計算,感覺好麻煩啊求大牛指點思路!

2013-06-26 16:37:10

,延時節拍由方框中的數字表示。各級轉接器和延時單元起到對序列進行碼位抽取并將數據拉齊的作用。每級延時在FPGA內部用FIFO實現,不需要對序列進行尋址即可實現延時功能。數據串行輸入,經過3級流水處理后

2019-06-17 09:01:35

我打算在FPGA上實現許多計算機視覺算法。 Digilent Atlys是這類應用的良好平臺嗎?我是初學者,不能自己解決這個問題。Digilent Atlys:http

2019-10-28 07:10:38

定點C6455DSP,在計算浮點數時,如何進行定標,因為程序里面大量的浮點數計算,因而想定標,這樣可以提高計算速度,求如何修改才可以實現定點的計算,我不知道該如何定標,如何用C語言實現啊?求給些意見或者資料

2020-05-27 12:21:41

TDSDM642是TI公司推出的定點DSP芯片,具有性價比高、運算速度快的優點,但是定點DSP對于浮點運算比較困難,因此在系統實現時需要對算法進行浮點到定點的移植。同時,為了使DSP上的代碼獲得

2012-04-18 10:54:27

以避免對FPGA邏輯資源的浪費,實現最優設計。但對浮點數的獲取卻關注很少。在浮點運算中,單精度浮點以其極強的通用性得到了最廣泛的應用。

2019-08-29 06:50:37

(用到了三角函數)都比較消耗電機主控芯片的計算能力。在考慮算法實現的時候,都需要針對主控芯片的實際性能進行一定優化,才能確保算法能夠順利運行。這里我總結下電機控制中對程序算法優化的辦法。數據的概念浮點

2021-08-27 06:37:05

擴充浮點運算集的時候,是否需要自己在FPGA板子上設置一個定點數轉為浮點數的部分?

2023-08-11 09:13:34

大家好我是剛剛來這的實習生(拱手)。最近在看 基于FPGA的H264運動估計算法優化與實現 方面的東西,他提出了一個概念:運動矢量。這是如何得到的?如何理解?有什么用?附錄原文中的一些東西:基于塊

2015-04-28 11:51:04

介紹一種在FPGA上實現的單精度浮點加法運算器,運算器算法的實現考慮了FPGA器件本身的特點,算法處理流程的拆分和模塊的拆分,便于流水設計的實現。

2021-04-29 06:27:09

本文介紹了一種基于FPGA的復數浮點協方差矩陣實現方案。

2021-04-29 06:01:31

求助大神,在FPGA上實現retinex算法 。。。

2013-05-08 23:29:41

仿真或者專用軟邏輯 FPU 在 PowerPC 上自如地實現浮點運算。圖 1 顯示了通過 FCB 將 PowerPC 440 處理器連接至 Virtex-5 APU-FPU 的典型實施方案。圖 1

2018-08-03 11:15:23

Altera20nmArria10FPGA和SoC中,以及14nmStratix10FPGA和SoC中。該新功能支持設計人員以相同的定點性能和效率在浮點中實現其算法,且不會對功耗、面積或者密度產生任何影響,也不會損失定點特性或

2019-07-03 07:56:05

:{real[0], imag[0], real[1], imag[1],………………} ,在使用中切記不要搞錯。30.1.2 浮點 浮點復數FFT使用了一個混合基數算法,通過多個基8與單個基2或基4算法實現

2016-09-28 08:13:10

復數FFT的逆變換實現 本小節主要講解復數FFT的逆變換實現,通過函數arm_cfft_f32實現浮點數的逆變換。31.1.1 arm_cfft_f32逆變換函數定義如下: void

2016-09-28 08:41:51

轉dsp系列教程本章主要講解實數的浮點和定點Q31,Q15的實現。關于這部分的知識點和函數的計算結果上,官方的文檔有一些小錯誤,在章節中會跟大家詳細講述,還有一個要注意的問題,調用實數FFT函數一定

2016-09-28 09:53:16

想了解下, CH573F的架構目前的浮點計算, 是軟浮點計算還是硬件浮點計算實現的呢?

2022-08-04 07:42:12

想要評估一下1024點浮點復數FFT在F7上面需要多少時間,但是CubeMX沒有庫支持,不知誰做過測試,謝謝!

2018-12-11 08:54:13

請問一下高速流水線浮點加法器的FPGA怎么實現?

2021-05-07 06:44:26

(如圖 2 和圖 3 所示)?這是MCU真正的計算速度嗎?我知道在 TI C2000 DSP 中,我們可以包含標量因子優化器庫標頭來加速浮點計算 (SFO_V8.h)。STM32 DSP 是否有類似的接頭?謝謝。

2023-02-01 06:35:42

如題,我用的DSP開發板是TMSC5535,需要用到Hibert濾波,需要用匯編語言實現,但是濾波器的系數是復數,請問匯編語言要怎么實現?(匯編語言實數濾波我已經會了),謝謝!

2018-07-31 07:24:29

我使用SIMULINK中的系統生成器設計了我的PID控制器浮點。我們可以使用生成的代碼在Zynq 7020 FPGA上實現設計嗎?或者我們需要在處理單元(ARM Cortex)上實現它?換句話說,我可以在FPGA上實現浮點而不是PS(處理器)嗎?謝謝。丹尼爾·穆罕

2019-09-03 10:14:00

并提高具有高動態范圍要求的實際設計的速度,這與普遍認為定點總是更有效率的觀點相反到浮點。本機浮點實現:在引擎蓋下HDL Coder通過模擬FPGA或ASIC資源上的基礎數學運算來實現單精度算術(圖1

2018-09-11 21:59:16

,時鐘區域,實現數學函數,浮點單元,復位電路,仿真,綜合優化,布圖,靜態時序分析等。. 本書把多年推廣到諸多公司和工程師團隊的經驗以及由白皮書和應用要點匯集的許多知識進行濃縮,可以幫助讀者成為高級

2012-03-01 14:59:23

高級FPGA設計、結構、實現與優化(Advanced FPGA Design Architecture, Implementation,and Optimization)

2013-12-10 14:16:25

介紹了用VHDL 語言在硬件芯片上實現浮點加/ 減法、浮點乘法運算的方法,并以Altera

公司的FLEX10K系列產品為硬件平臺,以Maxplus II 為軟件工具,實現了6 點實序列浮點加/ 減法

2009-07-28 14:06:13 85

85 針對在工業中越來越多的使用到的FFT,本文設計出了一種利用CORDIC 算法在FPGA 上實現快速FFT 的方法。CORDIC 實現復數乘法比普通的計算器有結構上的優勢,并且采用了循環結構

2009-08-24 09:31:10 9

9 本文詳細討論了利用新版本FPGA 輔助設計軟件QuartusII6.0 中提供的浮點運算功能模塊實現IIR 濾波器的方法,與采用FPGA 的乘法模塊的同類設計相比,此濾波器設計結構簡單,容易擴

2009-12-19 15:44:27 38

38 針對在工業中越來越多的使用到的FFT,本文設計出了一種利用CORDIC算法在FPGA上實現快速FFT的方法。CORDIC實現復數乘法比普通的計算器有結構上的優勢,并且采用了循環結構的CORDIC算

2010-08-09 15:39:20 55

55 如何以合理的硬件代價來實現高精度浮點超越函數計算,成為了微處理器設計過程當中的一個非常重要的問題。本論文提出了一種新的輸入輸出浮點處理單元硬件架構,它能將數據

2010-09-28 10:47:06 0

0 如何以合理的硬件代價來實現高精度浮點超越函數計算,成為了微處理器設計過程當中的一個非常重要的問題。反正切函數的計算在數字信號處理、導航通訊等諸多領域都有著有重

2010-11-02 15:31:55 35

35 高速流水線浮點加法器的FPGA實現

0 引言現代信號處理技術通常都需要進行大量高速浮點運算。由于浮點數系統操作比較復雜,需要專用硬件來完成相關的操

2010-02-04 10:50:23 2042

2042

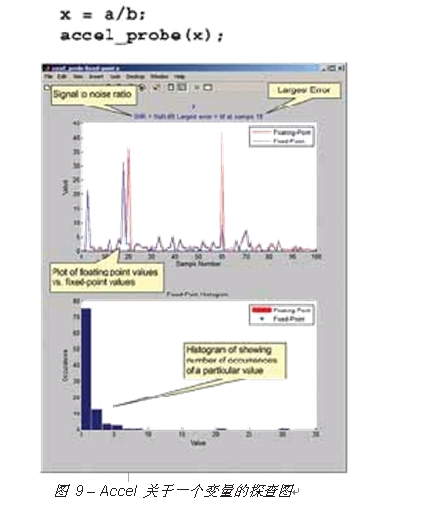

AccelChip 公司(最近已被賽靈思公司收購)最近所做的一次調查顯示,53% 的回答者認為浮點定點轉換是在 FPGA 上實現算法時最困難的地方(圖 1)。

2010-07-16 09:43:45 1348

1348

O 引言

協方差矩陣的計算是信號處理領域的典型運算,是實現多級嵌套維納濾波器、空間譜估

2010-10-08 17:41:14 2434

2434

Altera公司日前演示了使用FPGA的浮點DSP新設計流程,這是業界第一款基于模型的浮點設計工具,支持在FPGA中實現復數浮點DSP算法。伯克萊設計技術公司 (Berkeley Design Technology, Inc, BDTI) 進行

2011-09-15 08:48:58 898

898 Altera公司日前演示了使用FPGA的浮點DSP新設計流程,這是業界第一款基于模型的浮點設計工具,支持在FPGA中實現復數浮點DSP算法。

2011-09-15 09:07:10 613

613 高級FPGA設計結構、實現和優化 作者:(美)克里茲著,孟憲元譯;出版社:機械工程出版社 學FPGA不一定需要開發板,自己學會modelsim仿真、寫testbench,用PC機仿真就能有不少長進。這

2012-11-28 14:03:22 0

0 基于FPGA的SM3算法優化設計與實現的論文

2015-10-29 17:16:51 4

4 利用不同的科學計算器計算復數運算的步驟,幫你輕松解決復數運算的煩惱

2016-03-22 11:26:09 0

0 SVPWM算法優化及其FPGA_CPLD實現

2016-04-13 15:42:35 18

18 高級FPGA設計 結構、實現和優化,適合于FPGA的進階學習。

2016-05-11 16:40:55 15

15 高級FPGA設計 結構、實現和優化,適合于學習FPGA的進階學習。

2016-05-11 16:40:55 14

14 計算器上面復數轉換

2017-01-22 13:20:25 4

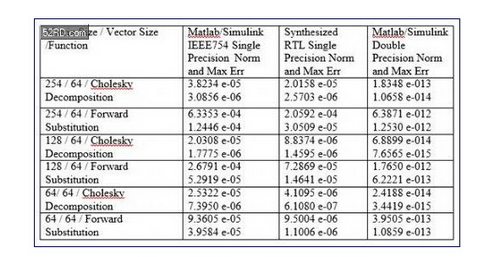

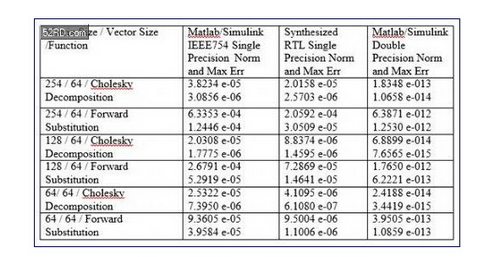

4 浮點具有更大的數據動態范圍,從而在很多算法中只需要一種數據類型的優勢。本文介紹如何使用Vivado HLS實現浮點復數矩陣分解。使用HLS可以快速,高效地實現各種矩陣分解算法,極大地提高生產效率, 降低開發者的算法FPGA實現難度。

2017-11-18 12:00:11 852

852

浮點算法不遵循整數算法規則,但利用 FPGA 或者基于 FPGA 的嵌入式處理器不難設計出精確的浮點系統。工程人員一看到浮點運算就會頭疼,因為浮點運算用軟件實現速度慢,用硬件實現則占用資源多。理解

2017-11-22 16:51:08 1350

1350 各種處理平臺的GFLOP指標在不斷提高,現在,TFLOP/s這一術語已經使用的非常廣泛了。但是,在某些平臺上,峰值GFLOP/s,即,TFLOP/s表示的器件性能信息有限。它只表示了每秒能夠完成的理論浮點加法或者乘法總數。分析表明,FPGA單精度浮點處理能夠超過1 TFLOP/s。

2018-02-19 03:53:00 4064

4064 2014年4月23號,北京Altera公司 (Nasdaq: ALTR) 今天宣布在FPGA浮點DSP性能方面實現了變革。Altera是第一家在FPGA中集成硬核IEEE 754兼容浮點運算功能

2018-02-11 13:34:00 6954

6954 浮點加法是數字信號處理中的一種非常頻繁且非常重要的操作,在現代數字信號處理應用中,浮點加法運算幾乎占到全部浮點操作的一半以上。浮點乘法器是高性能DSP(數字信號處理器)的重要部件,是實時處理的核心

2018-04-10 10:47:21 8

8 浮點運算是計算機運算的重要方式,較之定點運算有著計數范圍寬有效精度高的特點。在各種工程計算和科學計算中有著廣泛應用。目前浮點運算大多采用DSP芯片實現,具有算法簡單,精度高的優點。但同時由于浮點運算

2018-04-10 14:25:53 17

17 高性能浮點處理一直與高性能 CPU 相關聯。在過去幾年中,GPU 也成為功能強大的浮點處理平臺,超越了圖形,稱為 GPGPU(通用圖形處理單元)。新創新是在苛刻的應用中實現基于 FPGA 的浮點處理

2020-12-22 13:33:00 14

14 本文檔的主要內容詳細介紹的是如何使用Xilinx的FPGA對高速PCB信號實現優化設計。

2021-01-13 17:00:59 25

25 有些FPGA中是不能直接對浮點數進行操作的,只能采用定點數進行數值運算。對于FPGA而言,參與數學運算的書就是16位的整型數,但如果數學運算中出現小數怎么辦呢?要知道,FPGA對小數是無能為力

2021-08-12 09:53:39 4502

4502 使用插值算法實現圖像縮放是數字圖像處理算法中經常遇到的問題。我們經常會將某種尺寸的圖像轉換為其他尺寸的圖像,如放大或者縮小圖像。由于在縮放的過程中會遇到浮點數,如何在FPGA中正確的處理浮點數運算是在FPGA中實現圖像縮放的關鍵。

2022-03-18 11:03:41 4056

4056 隨著 機器學習 (Machine Learning)領域越來越多地使用現場可 編程 門陣列( FPGA )來進行推理(inference)加速,而傳統FPGA只支持定點運算的瓶頸越發凸顯

2023-03-11 13:05:07 351

351 本文是本系列的第五篇,本文主要介紹FPGA常用運算模塊-復數乘法器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:23:28 1204

1204

嗨!我試著寫點關于浮點數的東西,我發現自己對這個 64 位浮點數的計算方法很好奇: ? ? >>> 0.1 + 0.2 0.30000000000000004 我意識到我并沒有完全理解它是如何計算

2023-05-26 15:26:22 636

636 基于FPGA的浮點處理。本文的重點是FPGA及其浮點性能和設計流程,以及OpenCL的使用,這是高性能浮點計算前沿的編程語言。 各種處理平臺的GFLOP指標在不斷提高,現在,TFLOP/s這一術語已經使用的非常廣泛了。但是,在某些平臺上,峰值GFLOP/s,即,TFLOP/s表示的器件

2023-06-10 10:15:01 373

373

,浮點加法器是現代信號處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。 但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號處理等方

2023-09-22 10:40:03 394

394

最近出現的 FPGA設計工具和 IP有效減少了計算占用的資源,大大簡化了浮點數據通路的實現。而且,與數字信號處理器不同

2023-09-25 14:42:14 375

375

運算的運算步驟遠比定點運算繁瑣,運算速度慢且所需硬件資源大大增加,因此基于浮點運算的LMS算法的硬件實現一直以來是學者們研究的難點和熱點。 本文正是基于這種高效結構的多輸入FPA,在FPGA上成功實現了基于浮點運算的LMS算法。測試

2023-12-21 16:40:01 228

228

電子發燒友App

電子發燒友App

評論