交錯式ADC具有十分廣闊的應用空間。在通信基礎設施中,存在著一種推動因素,使ADC的采樣速率不斷提高,以便在諸如DPD(數字預失真)等線性化技術中支持多頻段、多載波無線電,同時滿足更寬的帶寬要求。

2014-04-17 17:54:17 2578

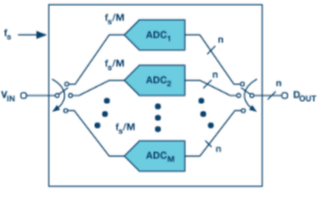

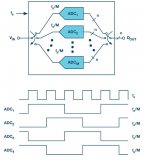

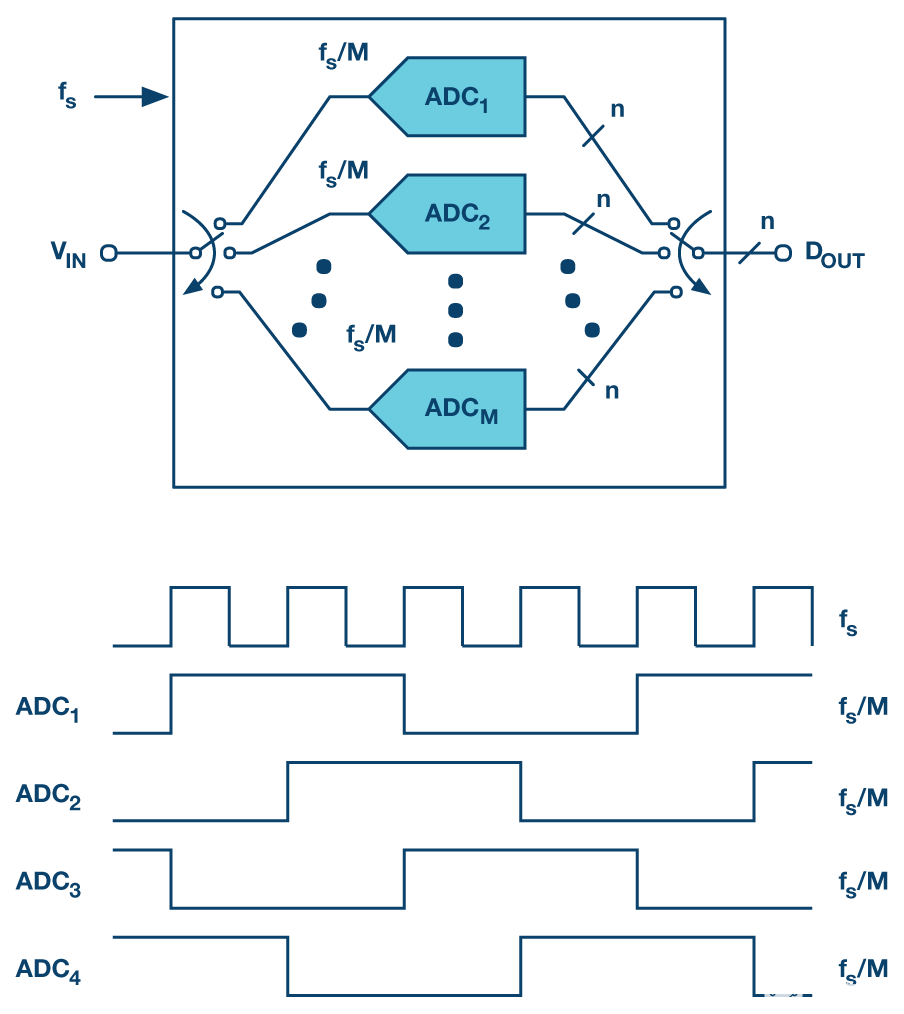

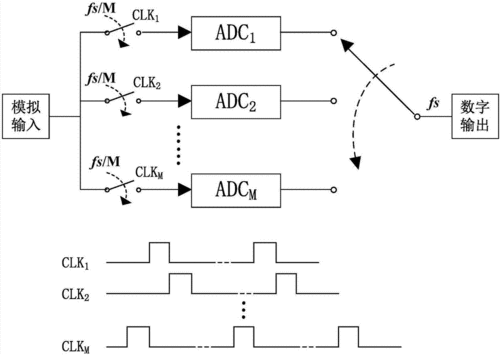

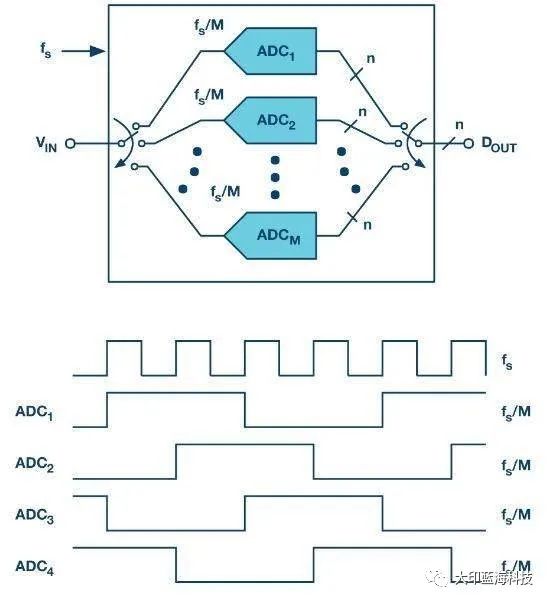

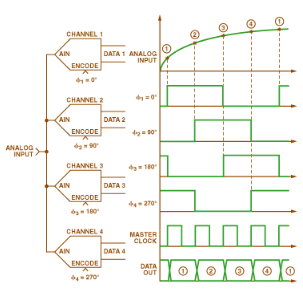

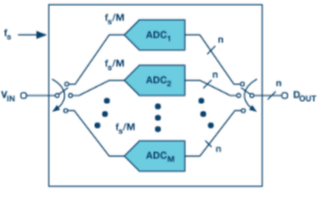

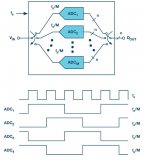

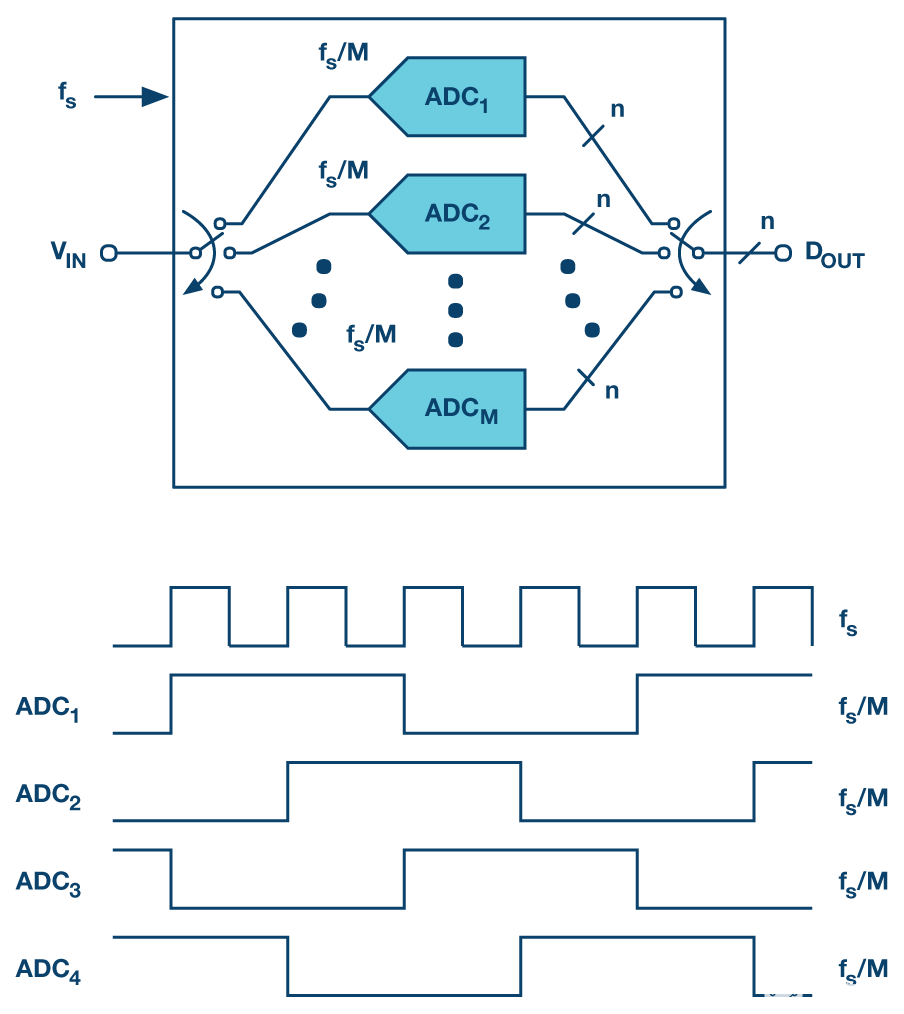

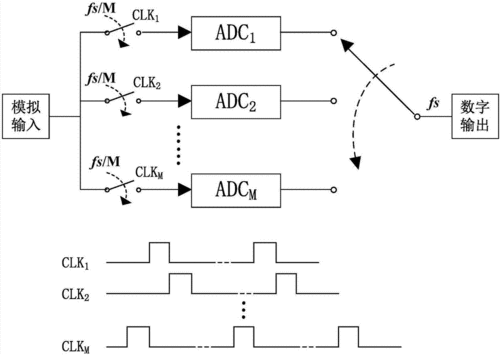

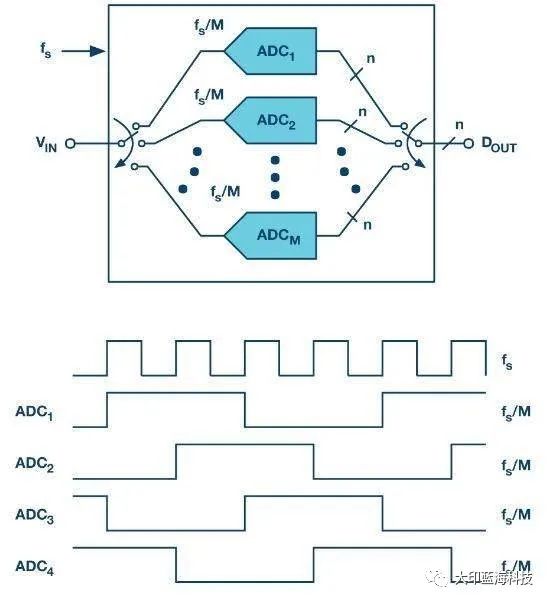

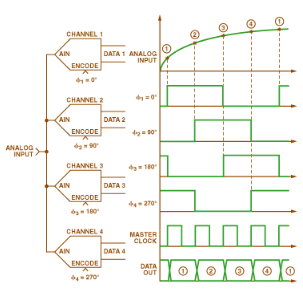

2578 圖1. M次交錯的n位ADC陣列每一個ADC的采樣速率為fs/M,得到的時間交錯ADC采樣速率為fs。M = 4的時鐘方案示例在該圖下半部分顯示。

2020-09-09 10:38:38 845

845

跨越當今市場的許多領域,交織的模擬-數字轉換器( ADC的)有幾個優點在許多應用。在通信基礎設施中,除了數字預失真( DPD )等線性化技術對帶寬的要求更高之外,一直在不斷尋求更高采樣率的ADC

2021-02-13 10:41:00 3424

3424

在本文中,我們描述了在 M 通道時間交錯模數轉換器 (TI-ADC) 的一般情況下,時序和增益失配對采樣信號的影響,并提出了一種適用于雙通道 TI- ADC 案例。 時序和增益失配的數字校正 作者

2021-06-14 03:45:00 3352

3352

今天我們將圍繞交錯式 ADC 轉換器展開。當 ADC 轉換器交錯時,兩個或多個具有定義的時鐘關系的 ADC 轉換器用于同時對輸入信號進行采樣并產生組合輸出信號,從而導致采樣帶寬為多個單獨的 ADC 轉換器。

2023-04-28 09:49:40 428

428

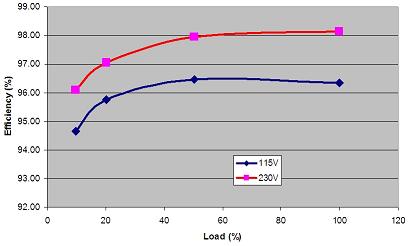

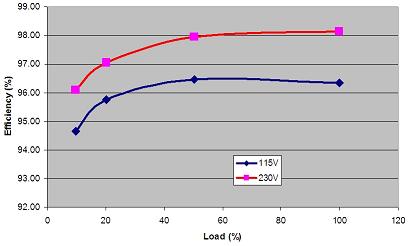

輸出端模擬調光。請參閱基于 UCC28060 交錯式交流直流單級反激的 LED 驅動器,了解設計指南主要特色隔離式準諧振反激 PFC 拓撲自然交錯模式可減少輸入和輸出紋波94% 的峰值效率模擬調光此參考設計已構建完成并通過測試,且內含測試報告

2018-12-07 14:09:20

ADP1829是一款多功能,雙輸出,交錯式同步PWM降壓控制器,可在3.0 V至18 V的輸入電壓范圍內產生兩路獨立輸出。每個通道均可配置為提供0.6V至85%輸入電壓的輸出電壓。兩個通道的相位相差180°,可減小輸入電容上的電流應力,并允許使用更小,更低成本的輸入電容

2020-06-09 17:25:38

適用于高帶寬,高采樣率應用程序的新型DESCLKI??Q模式與ADC10D1x00,ADC12D1x00引腳兼容用于多芯片同步的自動同步功能內部端接,緩沖差分模擬輸入交錯定時自動和手動偏斜調整用于系統調試

2021-01-08 09:15:08

適用于高帶寬,高采樣率應用程序的新型DESCLKI??Q模式與ADC10D1x00,ADC12D1x00引腳兼容用于多芯片同步的自動同步功能內部端接,緩沖差分模擬輸入交錯定時自動和手動偏斜調整用于系統調試

2021-01-08 09:15:08

交錯ADC得到了越來越多的工程師的廣泛關注。目前仍有諸多問題聚焦于ADC失配的校準方法。 在深入探討任何可能的校準方法之前,工程師需要了解都有哪些不匹配。 對于失調不匹配,沒有必要施加一個輸入信號

2019-07-25 06:58:19

交錯結構的優勢是什么交錯ADC的時鐘要求

2021-04-06 09:00:31

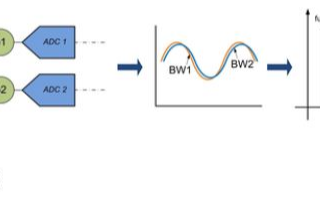

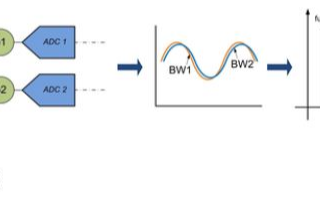

交錯式ADC之間的帶寬失配

2021-04-02 07:52:52

運用時序交錯式類比數位轉換器(timeinterleavedADC)在每秒高達數十億次的同步取樣類比訊號是一個技術上的挑戰,除此之外,對於混合訊號電路的設計也需要非常謹慎小心。基本上,時序交錯

2018-09-17 17:25:18

天線置入手機,其性能更易受外部條件的影響,如手機接近不同材料以及用戶握持手機的方式等。在這些條件下,天線阻抗可能發生變化,導致天線與RF 前端 (RFFE) 之間的阻抗失配。當天線在不同頻段通信時,天線阻抗

2023-05-05 09:43:21

這篇文章提供了對范例式集成比例型三線RTD測量系統的分析,以便了解誤差的來源,包括勵磁電流失配產生的影響。

2020-08-24 07:23:03

為 ~ 35Mhz ADC 時鐘獲得 ~ 8MHz 采樣率(雙交錯 2x4MHz,連續轉換)在我嘗試在禁用連續轉換的情況下從定時器觸發 ADC 之前,這非常有效。對于 8MHz(2 x 4MHz)采樣率,我需要

2023-01-06 07:15:22

設計lna時想要查看差分輸出的增益失配和相位失配,這要怎么設置才能仿真出來?請給位大神指點。

2021-06-25 06:22:44

電壓和參考電壓上。由于ADC輸出代碼表示的是輸入電壓和參考電壓之間的關系,故最終轉換結果可換算為RTD電阻和RREF電阻的比,并非取決于參考電壓或勵磁電流的值(方程式11)。所以,如果勵磁電流完美匹配

2018-11-30 16:48:27

這篇文章將討論兩種可消除勵磁電流失配和失配漂移影響的方法。第一種方法是把內部多路復用器用于大多數集成式解決方案的軟件方法。第二種方法是更改電路拓撲結構的硬件方法。

2020-08-27 07:13:57

匹配、時序不匹配和帶寬不匹配。其中最容易理解的可能是兩個ADC之間的失調不匹配。每個ADC都會有一個相關的直流失調值。當兩個ADC交織并在兩個ADC之間來回交替采樣時,每個連續采樣的直流失調會發

2020-08-05 09:54:42

PWM 波形。該設計實現了新型的電流共享技術,以準確地在相位之間實現電流平衡。主要特色數控式兩相交錯 LLC 諧振直流/直流轉換器無需任何額外硬件即可實現出色的相位間電流共享峰值效率:94.5%。對于

2018-12-26 14:42:54

,這些標準仍將需要高動態范圍,以便充分清晰地觀察小信號。解決這些需求的一種技術是時間交織的ADC。對于高速ADC,性能,采樣率和功耗之間存在折衷。時間交錯在不同時間使用多個ADC采樣來提高有效采樣率,同時

2017-04-26 12:04:25

介紹了采用商用1200V碳化硅(SiC)MOSFET和肖特基二極管的100KHz,10KW交錯式硬開關升壓型DC / DC轉換器的參考設計和性能。 SiC功率半導體的超低開關損耗使得開關頻率在硅實現方面顯著增加

2019-05-30 09:07:24

內存交錯功能可并行閱讀大內存芯片,減小內存訪問時間。內存交錯功能最多可并行訪問單CPU內存板上的 32 個內存芯片。

2019-09-18 09:01:19

的帶寬。SMT焊盤與內部參考銅箔之間的距離取決于SMT焊盤的寬度以及包括連接器引腳和焊錫在內的SMT焊盤有效厚度。在PCB投產之前應先進行3D建模和仿真,確保構建的傳輸通道具有良好的信號完整性。

2018-09-17 17:45:00

CRD-60DD12N,60 kW交錯式升壓轉換器演示板基于1200 V,75mΩ(C3M)SiC MOSFET。該演示板由四個15 kW交錯升壓級組成,每個級使用CGD15SG00D2隔離式柵極驅動板

2019-04-29 09:18:26

由NCP1631板驅動的300W交錯式PFC級的應用示意圖,調整為NCP1632驅動。 NCP1632是NCP1631的升級版本。與他的父親一樣,NCP1632是用于交叉間PFC應用的雙MOSFET

2019-05-16 09:08:22

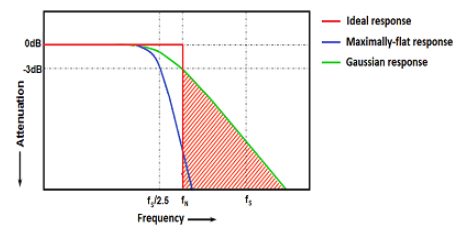

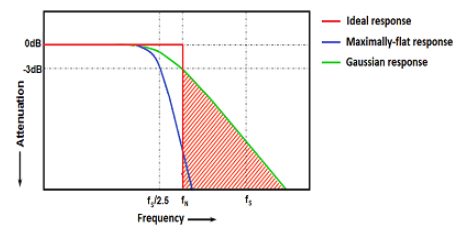

作者:Rob Reeder摘要模擬帶寬的重要性高于其他一切在越來越多的應用中得到體現。隨著GSPS或RF ADC的出現,奈奎斯特域在短短幾年內增長了10倍,達到多GHz范圍。這幫助上述應用進一步拓寬

2019-07-22 08:01:03

我有一個關于 STM32H7(雙核解決方案)的 ADC1/2/3 內核的問題。比方說,我想在 ADC 內核和 Cortex 內核之間拆分幾個 ADC 通道。是否可以在皮質 m4 上為 ADC1 核心

2023-01-10 06:09:51

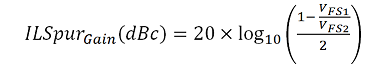

在信號鏈中運用采樣保持放大器(THA),可以從根本上擴展帶寬,使其遠遠超出 ADC 采樣帶寬,滿足苛刻高帶寬的應用的需求。本文將證明,針對 RF 市場開發的最新轉換器前增加一個 THA,便可實現超過

2020-09-30 07:00:00

也對這個問題深感頭痛。“阻抗失配”產生的原因是因為對象模型與關系模型之間缺乏固有的親合力。“阻抗失配”所帶來的問題包括:類的層次關系必須綁定為關系模式(將對象類映射為關系表),ID生成,并發訪問以及

2019-06-04 06:47:47

的基本工作原理圖。 改善信號發生器或頻譜分析儀的失配損耗 如果負載和信號發生器之間的阻抗不匹配,就會產生失配誤差。在任何射頻和微波系統中,最大功率傳輸的條件是阻抗匹配。但實際上,無論是信號發生器還是

2017-11-07 16:43:03

假設一對電流鏡(1:1),電流10uA,寬長分別比50um/1um,finger=2和10um/1um,finger=10兩種情況。失配哪一個大?或者一樣?至少書上說,兩個面積一樣,失配一樣,真是這樣?仿真出來感覺前者好的多啊!為什么?

2021-06-24 07:14:05

控制電路來處理此問題(如果沒有該電路,并聯各相之間的微小器件不匹配就會造成巨大的相位電流不平衡),有些方法優于其它方法。[img][/img]圖1:雙相交錯式雙開關正向轉換器 數字電源管理能夠執行復雜

2011-07-14 08:52:28

有沒有帶寬介于AD637和AD8361之間的芯片?

2017-07-31 18:47:34

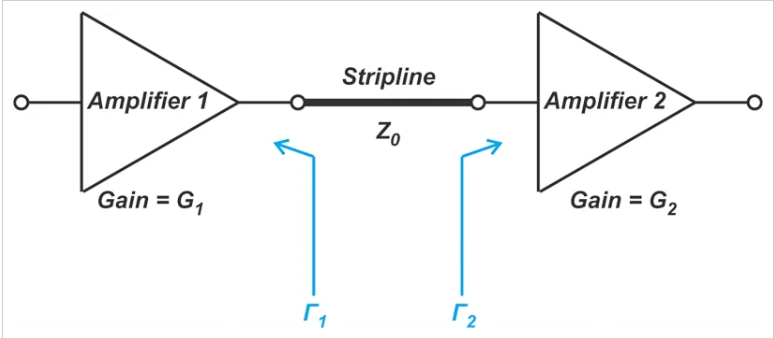

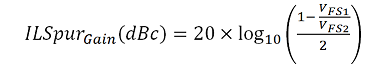

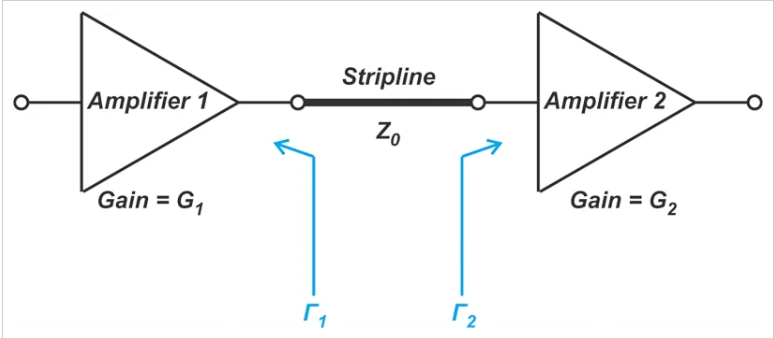

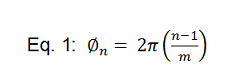

交錯式ADC之間的帶寬失配應該是對于設計師而言最難解決的失配問題。 如圖所示,帶寬失配具有增益和相位/頻率分量。 這使得解決帶寬失配問題變得更為困難,因為它含有兩個來自其他失配參數的分量:增益和時序失配。

2019-07-31 06:59:10

交錯 ADC。對三個通道之間的失配進行校準,以便最大程度減少交錯雜散。圖 5(a) 所示是一個輸入接近 1 GHz的輸出頻譜示例。在該頻譜中,除了約為 1 GHz的輸入音外,還可以看到通道在 500

2018-10-24 09:51:54

描述此參考設計提供了一個用于實現 12.8GSPS 采樣率的交錯射頻采樣模數轉換器 (ADC) 的實用示例。這可通過對兩個射頻采樣 ADC 進行時序交錯來實現。交錯需要在 ADC 之間進行相移,此

2022-09-15 06:46:05

ADC內核可以并行工作,從而實現高于單核的采樣速率。然而,每個這些內核的輸入端之間都存在相位、失調、增益和帶寬微小差異。結果,新的交錯偽像和圖像雜散可能進入頻譜中,從而導致ADC寬帶SFDR下降。這會減小

2018-11-01 11:31:37

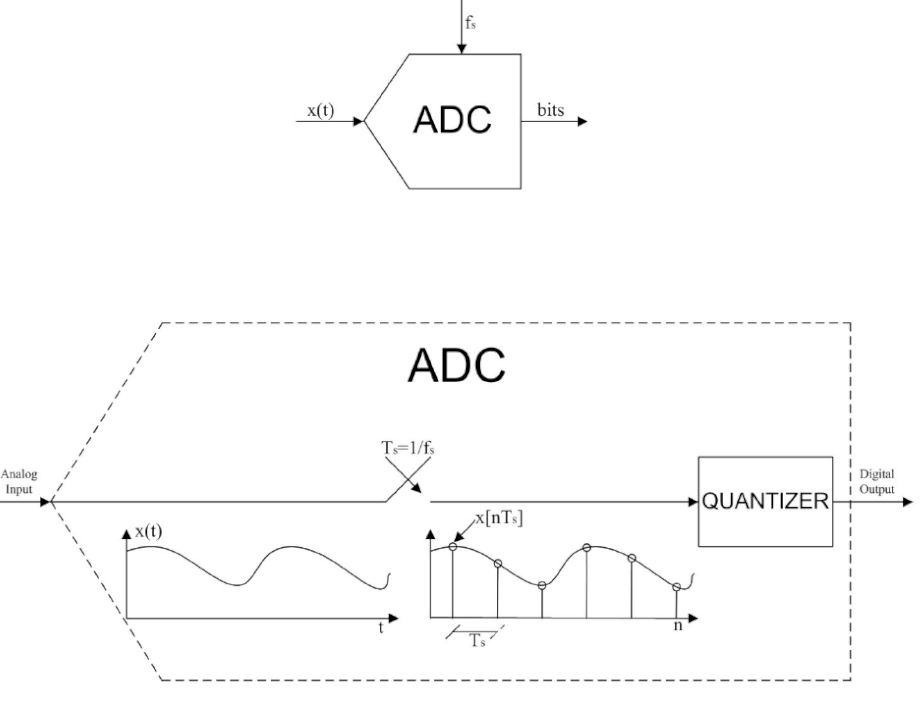

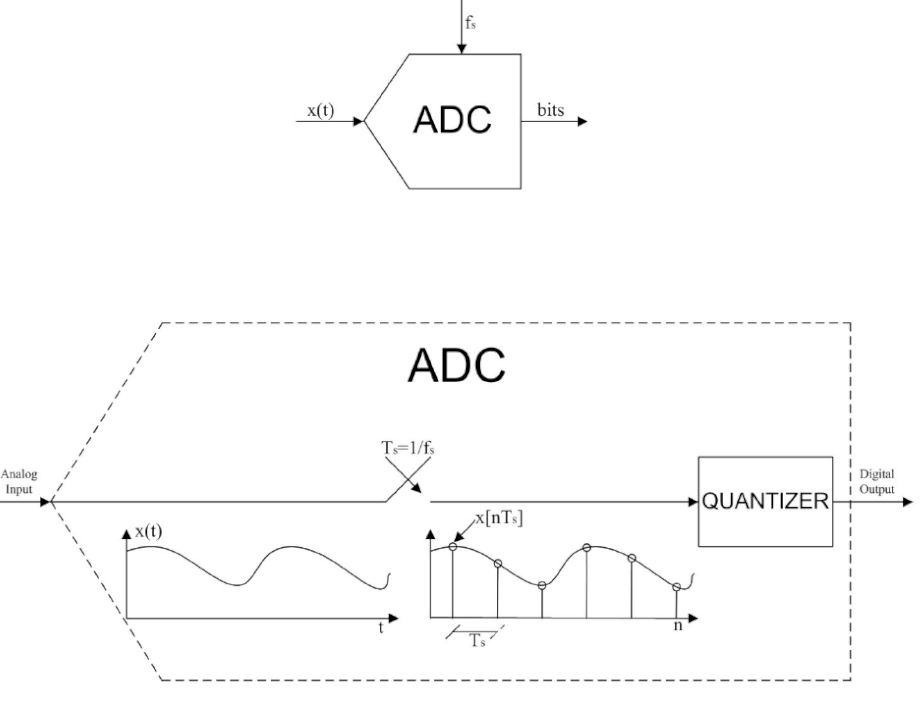

時間交錯技術可使用多個相同的 ADC(文中雖然僅討論了 ADC,但所有原理同樣適用于 DAC 的時間交錯特性),并以比每一個單獨數據轉換器工作采樣速率更高的速率來處理常規采樣數據序列。簡單說來,時間

2019-07-23 06:52:17

我閱讀了有關ADC全功率帶寬的求解過程,文件中說明全功率帶寬由瞬態公式推導求得,此公式的來源是什么?

2023-11-30 06:05:22

`描述TI 設計:TIDA-00200 為需要 ~200W 輸出功率級別的電池充電應用提出了一種具有最低物料清單成本的交錯反激式拓撲。在實際電子組件之外,冷卻機制是總體設計成本的一大來源。該設計利

2015-04-29 11:36:56

描述TIDA-00200 為需要 ~200W 輸出功率級別和超精簡物料清單的電池充電器應用提供了一種交錯反激式拓撲。除了實際的電子元件外,冷卻方面的工作也占了總體設計成本的大部分。該設計利

2022-09-23 06:32:07

描述TI 設計:TIDA-00200 為需要 ~200W 輸出功率級別的電池充電應用提出了一種具有最低物料清單成本的交錯反激式拓撲。在實際電子組件之外,冷卻機制是總體設計成本的一大來源。該設計利

2018-09-18 09:10:25

針對時域交錯模數轉換器(TIADC)的通道失配問題,提出一種在線校正方法。首先建立TIADC的數學模型,將增益和時間失配轉變為通道濾波器幅度和延時參數的差異,然后利用校正后

2009-12-31 14:00:09 13

13 此參考設計提供了一個用于實現 12.8GSPS 采樣率的交錯射頻采樣模數轉換器 (ADC) 的實用示例。這可通過對兩個射頻采樣 ADC 進行時序交錯來實現。交錯需要在 ADC 之間進行

2010-03-26 16:13:22 68

68 交錯式PFC技術趨勢及新穎的單芯片交錯式PFC控制器的應用

近年來,在一些對外形因數有嚴格要求的應用中,如纖薄型液晶電視或筆記本適配器等,一種新興的功率因

2010-01-07 11:05:43 3133

3133

高速ADC提升分辨率與帶寬

ADC(模數轉換器)器件速度提升帶來功耗增加,從而提高了整體系統的成本。因此設計者的首要需求之一就是要降低高速ADC的功耗。ADI

2010-03-30 18:01:58 1181

1181 交錯反激微功率光伏并網逆變器的設計_張錦吉

2016-12-15 19:30:58 4

4 交錯并聯反激式準單級光伏并網微逆變器_季曉春

2016-12-15 19:30:58 2

2 基于過零檢測的TIADC時鐘失配校準算法_王曉蕾

2017-01-07 18:39:17 1

1 時間交織ADC時間失配后臺數字校準算法_鄧紅輝

2017-01-08 10:30:29 1

1 交錯結構的優勢可惠及多個細分市場。 最有用的優勢是通過交錯ADC更寬的奈奎斯特區增加帶寬。 同樣,我們首先舉兩個500MSPS ADC交錯建立1000MSPS采樣速率的例子。 通過交錯兩個ADC

2017-11-16 10:20:06 0

0 交錯式ADC之間的帶寬失配應該是對于設計師而言最難解決的失配問題。 如圖1所示,帶寬失配具有增益和相位/頻率分量。 這使得解決帶寬失配問題變得更為困難,因為它含有兩個來自其他失配參數的分量:增益

2017-11-16 10:51:03 1

1 時間交錯技術可使用多個相同的 ADC(文中雖然僅討論了 ADC,但所有原理同樣適用于 DAC 的時間交錯特性),并以比每一個單獨數據轉換器工作采樣速率更高的速率來處理常規采樣數據序列。簡單說來,時間交錯(IL)由時間多路復用 M 個相同的 ADC 并聯陣列組成。

2018-01-17 14:59:51 7735

7735

目前的語音識別系統在訓練環境與測試環境匹配的情況下具有很高的識別率,而當環境失配時,其性能將急劇下降。作者研兗發現,帶寬失配,即訓練語料和測試語料帶寬不-致,也是引起環境失配的主要原因之一。當測試

2018-11-28 15:21:56 3

3 交錯式ADC之間的帶寬失配應該是對于設計師而言最難解決的失配問題。 如圖1所示,帶寬失配具有增益和相位/頻率分量。這使得解決帶寬失配問題變得更為困難,因為它含有兩個來自其他失配參數的分量:增益和時序失配。

2020-09-27 10:44:00 0

0 交錯式ADC之間的帶寬失配應該是對于設計師而言最難解決的失配問題。 如圖1所示,帶寬失配具有增益和相位/頻率分量。 這使得解決帶寬失配問題變得更為困難,因為它含有兩個來自其他失配參數的分量:增益和時序失配。

2020-09-02 09:56:51 751

751

由于有限的輸入帶寬,除非您將采樣率設置得非常低,否則ADC的帶寬通常小于奈奎斯特頻率。

2021-01-14 14:35:45 19330

19330

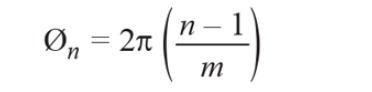

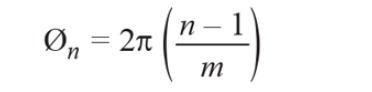

若ADC為交錯式,則兩個或兩個以上具有固定時鐘相位差關系的ADC用來同步采樣輸入信號,并產生組合輸出信號,使得采樣帶寬為單個ADC帶寬的數倍。利用m個ADC可讓有效采樣速率增加m倍。

2021-01-04 16:20:05 1872

1872

電子發燒友網為你提供ADC 的時間交錯特性討論資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-29 16:54:12 7

7 12位時間交織流水線adc的設計與通道失配分析(肇慶理士電源技術有限公司生產車間)-高性能的模數轉換器越來越多的應用在國防、通信和高端家電等領域,是電子信息產業中的一項關鍵技術。隨著電子信息領域

2021-09-17 11:48:05 5

5 模數轉換器(ADC)的時間交錯是一種根據并行應用數個ADC來提升 整體化系統采樣率的方式。考驗取決于處置各種ADC之間的失配,尤其是在較高頻率下。

2021-10-11 11:15:54 804

804 時間交錯技術可使用多個相同的 ADC(文中雖然僅討論了 ADC,但所有原理同樣適用于 DAC 的時間交錯特性),并以比每一個單獨數據轉換器工作采樣速率更高的速率來處理常規采樣數據序列。簡單說來,時間交錯(IL)由時間多路復用 M 個相同的 ADC 并聯陣列組成。

2022-03-10 10:35:38 2508

2508

連續時間線性均衡 (CTLE) 的值來減少 ADC 面積和功耗。由于采用了交錯式 ADC(如閃存),因此 ADC 面積和功率隨 ADC 通道的數量而變化。

2022-07-28 08:03:10 1083

1083 電子發燒友網站提供《ADC in隔板用于ADC in和I/O板之間.zip》資料免費下載

2022-08-16 10:05:30 1

1 本文介紹了一種 12 位 10GS/s 交錯 (IL) 流水線模數轉換器 (ADC)。該 ADC 采用 4 GHz 輸入信號實現 55 dB 的信噪比和失真比 (SNDR) 和 66 dB 的無雜散動態范圍 (SFDR),采用 28 nm CMOS 技術制造,功耗為 2.9 W。

2022-12-15 16:32:33 1538

1538

當ADC交錯時,使用兩個或多個具有定義時鐘關系的ADC同時對輸入信號進行采樣,并產生組合輸出信號,從而在單個ADC的某個倍數處產生采樣帶寬。利用m個ADC可將有效采樣速率提高m倍。為了簡單易懂,我們將重點介紹兩個ADC的情況。

2022-12-21 11:46:07 1046

1046

詳解平衡系統的ADC尺寸、功耗、分辨率和帶寬

2022-12-22 17:56:12 1590

1590

時間交錯是一種允許使用多個相同的模數轉換器的技術[1](ADC)以比每個單獨數據轉換器的工作采樣速率更快的速率處理常規采樣數據系列。簡單來說,時間交錯(IL)包括對M個相同ADC的并行陣列進行

2023-01-08 16:33:51 818

818

使用失配損耗方程,了解失配損耗對射頻功率測量和級聯放大器增益的影響。

2023-02-19 10:06:28 976

976 交錯多個模數轉換器(ADC)通常是為了提高轉換器的有效采樣速率,特別是當沒有或只有少數現成的ADC可以滿足此類應用所需的采樣、線性度和交流要求時。然而,時間交錯數據轉換器并非易事,因為即使使用完全線性的元件,增益/失調失配和時序誤差也會導致輸出頻譜中出現不希望的雜散。

2023-02-24 17:16:21 597

597

了解失配損耗對有損線路的影響、通過固定衰減器減少失配損耗的方法以及該誤差的統計模型。

2023-02-27 14:17:48 723

723

FFE 阻抗通常是恒定的 50Ω,但天線阻抗會根據頻段和使用條件而變化。當存在阻抗失配時,在 RFFE 和天線之間傳輸的 RF 功率會減少。

2023-03-14 14:22:43 795

795 今天我們將圍繞交錯式 ADC 轉換器展開。當 ADC 轉換器交錯時,兩個或多個具有定義的時鐘關系的 ADC 轉換器用于同時對輸入信號進行采樣并產生組合輸出信號,從而導致采樣帶寬為多個單獨的 ADC 轉換器。

2023-05-11 15:19:36 929

929

在當今的許多細分市場,交錯式模數轉換器(ADC)在許多應用中都具有多項優勢。在通信基礎設施中,存在著一種推動因素,使ADC的采樣速率不斷提高,以便支持多頻段、多載波無線電

2023-06-02 10:37:07 368

368

隨著電子信息技術的快速發展,模數轉換器 (ADC) 的應用領域不斷拓展,而各個應用系統對于ADC的要求也不斷提高。

2023-06-02 10:40:43 658

658

前面使用simplis分別介紹了交錯CRM BOOST 過零檢測與起振信號、ON TIME控制、變頻交錯等電路,詳見。

2023-06-23 10:36:00 567

567

通過以雙倍采樣率多路復用(例如)一對轉換器的輸出來對多個模數轉換器進行時間交錯,現在已經是一個成熟的概念——布萊克和霍奇斯于 1980 年首次提出。1, 2在設計 7 位、4MHz 模數轉換器 (ADC) 時,他們確定時間交錯解決方案需要的芯片面積比同類的 2 MHz 模數轉換器n閃存轉換器設計。

2023-06-17 15:37:39 582

582

交錯式ADC轉換器絕對是推動更高效接口的一部分。交錯式ADC轉換器為系統設計人員提供了多種優勢。然而,隨著轉換器帶寬的增加,需要在FPGA或ASIC中處理大量數據。必須有一些有效的方法來處理轉換器

2023-06-30 16:56:35 437

437

現在事情變得越來越有趣。我們一直在研究交錯雜散的位置,并查看了偏移失配產生的雜散水平。通過進行一些計算,我們能夠看到兩個交錯ADC之間的失調失配會產生多大的雜散。就像我們在查看馬刺的位置時所做的那樣

2023-06-30 17:18:17 786

786

使用ADC時需要重點關注的參數。采樣率和帶寬之間的關系是非常重要的,下面將詳細分析采樣率和帶寬之間的關系。 一、 ADC采樣率和帶寬的定義 首先,我們需要了解ADC采樣率和帶寬的定義。采樣率是指ADC每秒鐘可以采集并轉換模擬信號的次數。例如,如果ADC的采樣率為10kHz,則每秒可以將模

2023-09-12 10:51:12 6009

6009 怎么解決失配損耗對有損線路的影響? 有損線路是指在傳輸信號時會有信號衰減和失真現象出現的線路,由于其衰減和失真的特性,有時候會導致失配損耗的出現,從而對傳輸信號帶來不良影響。 失配損耗是指將兩條電纜

2023-10-30 10:56:46 161

161 如何處理同軸阻抗失配?如何避免阻抗失配這種風險呢? 同軸阻抗失配是電子通信領域中一種常見的問題,當同軸電纜的輸出端口的阻抗與接收端口不匹配時,就會發生阻抗失配。這種失配會導致信號反射、傳輸效率降低

2023-11-28 14:18:27 390

390 一文讀懂寬帶、帶寬、網速之間的區別與關系? 寬帶、帶寬和網速是在網絡領域中經常使用的術語,它們之間有一定的區別和關系。在深入理解寬帶、帶寬和網速之間的關系之前,讓我們先了解一下它們的定義。 寬帶

2024-01-31 09:11:30 304

304

電子發燒友App

電子發燒友App

評論