您是否聽到有人抱怨每天要為4G電話充電兩次?很遺憾,他對自己的手機(jī)并不太滿意。

隨著人們對高速數(shù)據(jù)讀寫的需求與日俱增,而電池的容量卻無法跟上通信技術(shù)前進(jìn)的步伐,這種現(xiàn)象一直屢見不鮮。 這并不是電池的問題,而是我們需要一種技術(shù)來使手機(jī)放大器變得更為強(qiáng)大。 過去普遍采用普通的DC-DC轉(zhuǎn)換器來控制手機(jī)電池電量流入不同的芯片。 這包括將手機(jī)信號驅(qū)動回基站的功率放大器(PA),對于2G和3G信號,由于峰均功率比(PAPR)相對較小,該功率放大器可以很好地工作。 但隨著技術(shù)從GSM發(fā)展到GPRS、WCDMA直至HSPA,PAPR也大幅升高。 現(xiàn)在LTE或4G具有非常高的PAPR,極大影響了手機(jī)的耗電量。 圖1顯示的是基于設(shè)備電池特定功率輸入的典型PA輸出隨技術(shù)發(fā)展的變化。

圖1.不同無線標(biāo)準(zhǔn)的PAPR演示: 該圖顯示的是一個典型PA的電池輸入功率(Pin)和輸出功率之比。信號功率壓縮隨著不同的PA設(shè)計而異,但PAPR則保持不變。

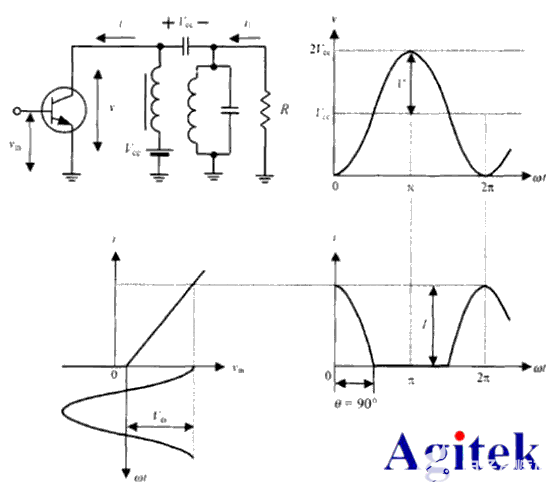

DC-DC轉(zhuǎn)換器在信號功率達(dá)到峰值時以線性方式吸收設(shè)備電池的電量,這種效率并不高。 提高電能效率的一種方式是預(yù)測手機(jī)信號的峰值,然后僅向PA提供所需的電量。這種供電方式稱為功率包絡(luò)跟蹤(ET)。 圖2顯示的是ET方法。

圖2. 當(dāng)傳輸波形(以紅色標(biāo)示)的功率不為峰值時,ET供電方法(以藍(lán)色標(biāo)示)可減少電能的浪費(fèi)。

在過去十年中,功率包絡(luò)跟蹤技術(shù)已經(jīng)解決了基站的這一難題,不僅節(jié)省了功耗,還可防止過熱,這是由于PA可以處理大約200W或更高的功率。 現(xiàn)在,半導(dǎo)體技術(shù)已經(jīng)發(fā)展到一定程度,DC-DC轉(zhuǎn)換器可用于移動設(shè)備,可為PA提供所需的調(diào)制功率,這種技術(shù)出現(xiàn)得非常及時,因?yàn)長TE等4G技術(shù)正在不斷地迫使人們提高PA的效率。 現(xiàn)在我們?nèi)绾螠y試這一新技術(shù)? 以下是一個PA測試解決方案的測試流程概述。

ET測試的挑戰(zhàn)

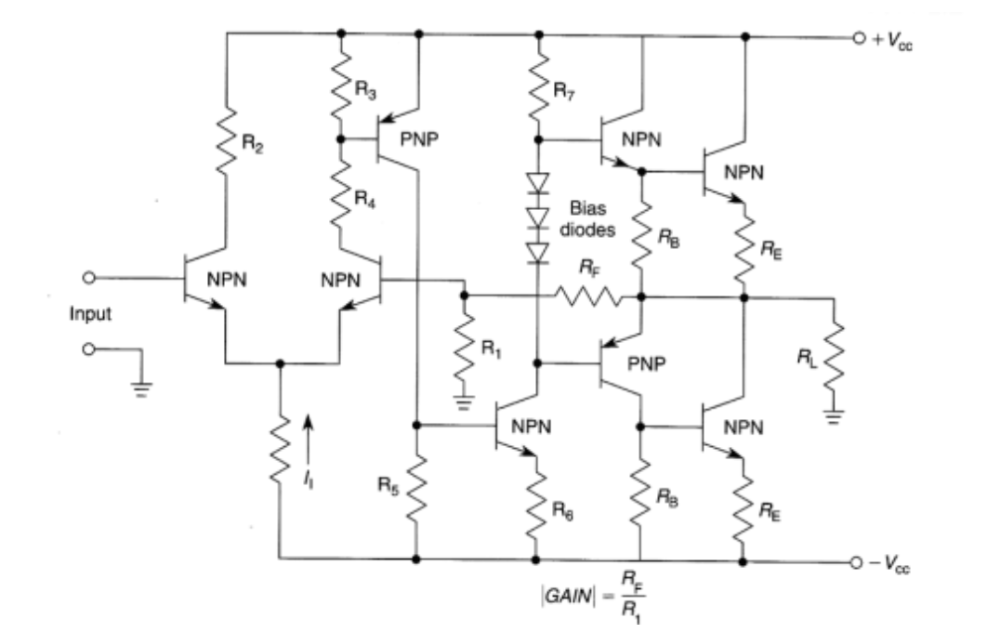

ET測試使得原本就非常復(fù)雜的系統(tǒng)變得更為復(fù)雜。 采用ET技術(shù)的第一個挑戰(zhàn)就是生成調(diào)制的供電電源,該電源需要高達(dá)2W的功率和數(shù)十兆赫茲的帶寬。 這些要求對于電源來說并不常見,因此許多PA制造商使用經(jīng)改良的DC-DC轉(zhuǎn)換器來執(zhí)行功率調(diào)制。 這些芯片可接受直流電源、用于控制放大器增益的包絡(luò)波形以及用于控制芯片的一些數(shù)字線的輸入。 輸出是一個高功率調(diào)制波形,用于提高待測放大器的放大功能。 詳見圖3了解典型的RF PA測試設(shè)置,該設(shè)置已進(jìn)行擴(kuò)展,可支持ET。

圖3. 圖為RF PA測試的典型配置,可實(shí)現(xiàn)包絡(luò)跟蹤。

從測試和特征記述的角度來看,主要的挑戰(zhàn)在于對執(zhí)行ET所必需的不同儀器進(jìn)行同步。 最為重要的是,必須以最低程度的抖動同步RF信號發(fā)生器和基帶任意波形發(fā)生器(AWG)。 此外,它必須能夠以次納秒的精度偏移基帶包絡(luò)相對于RF波形的延遲。 如果使用傳統(tǒng)臺式儀器,要實(shí)現(xiàn)這一程度的同步是非常困難的,而且還很有可能會涉及不同廠商的硬件,使應(yīng)用軟件變得更復(fù)雜。

NI簡化了同步問題,并將軟硬件集成到一個平臺上,從而盡可能地使該流程變得簡單明了。 PXI背板(見 圖4)可用于路由機(jī)箱內(nèi)實(shí)現(xiàn)同步所需的所有時鐘和觸發(fā)線,因而無需外部時鐘和觸發(fā)來路由網(wǎng)絡(luò)。 為了實(shí)現(xiàn)次納秒級的同步和可重復(fù)性,采用NI-TCLK來協(xié)調(diào)多個模塊化儀器間的時鐘和觸發(fā)分布。 如需詳細(xì)了解NI-TClk如何以低達(dá)20psrms的抖動來同步多個儀器,請閱讀NI T-Clock技術(shù)用于模塊化儀器定時和同步。

圖4. 圖為PXI Express背板以及時鐘和觸發(fā)原理圖。

最后, NI的各種模塊化儀器產(chǎn)品可用作為具有ET功能的RF PA測試設(shè)置的每一個組件。 您也可將完整的PA測試系統(tǒng)集成到一個PXI機(jī)箱和統(tǒng)一的硬件驅(qū)動API集合,這可極大簡化系統(tǒng)的集成和測試開發(fā)。

1. NI測試解決方案

硬件設(shè)置

如果要對標(biāo)準(zhǔn)PA測試解決方案進(jìn)行改良以適應(yīng)ET測試,必須在系統(tǒng)中添加AWG(見圖3)。 AWG必須能夠驅(qū)動單端和差分負(fù)載,應(yīng)用常見模式和微分直流偏移、可變增益設(shè)置以及靈活的時鐘選項(xiàng)。 NI PXIe-5451是一款可滿足所有這些需求的400 MS/s雙通道AWG。 它還包含許多板載信號處理函數(shù),其中包括用于脈沖整形和插值的脈沖響應(yīng)(FIR)濾波、平坦度校正以及可減少軟件預(yù)處理的數(shù)字上變頻器。了解更多關(guān)于NI PXIe-5451的信息。

在該應(yīng)用中使用的RF信號發(fā)生器是6.6 GHz NI PXIe-5673E矢量信號發(fā)生器(VSG),其帶寬超過100 MHz。 NI PXIe-5673E是由三個獨(dú)立的模塊組成: NI PXIe-5450任意波形發(fā)生器、NI PXIe-5652本地振蕩器和NI PXIe-5611 I/Q矢量調(diào)制器。

圖5. NI PXIe-5673E VSG的正面圖展示了三個獨(dú)立的模塊。

圖6顯示的是驗(yàn)證VSG和AWG同步和重復(fù)性所使用的設(shè)置。 NI PXIe-5673E VSG用于生成RF波形,NI PXIe-5451用于生成基帶包絡(luò)波形。 NI PXIe-5154 1 GHz數(shù)字化儀用于同步驗(yàn)證,但也可使用任何具有足夠高采樣率和帶寬的示波器。

圖6. 該測試設(shè)置驗(yàn)證了AWG和VSG是同步的。

為了同步AWG和VSG,兩個設(shè)備必須共享同一個10 MHz參考時鐘。 參考時鐘的來源可以是NI PXI 10 MHz背板時鐘,也可以是外部提供的10 MHz時鐘。

軟件

圖7顯示的是生成實(shí)現(xiàn)ET所需的RF和包絡(luò)波形所必需的軟件步驟。 要生成的LTE波形可使用NI LTE工具包來創(chuàng)建,或從文件中讀取。 然后便可計算包絡(luò)波形,包絡(luò)波形是LTE波形的一個函數(shù)。 您也許還希望進(jìn)行一些額外的信號處理,比如數(shù)字預(yù)失真或其他濾波操作來優(yōu)化用于ET的波形。 可對VSG進(jìn)行配置來生成LTE波形,NI PXIe-5451的配置與NI PXIe-5673E VSG中的NI PXIe-5450 AWG相似(見圖5)。 接著包絡(luò)波形便可相對RF波形進(jìn)行時移,并與用于控制波形生成的硬件腳本一起寫入到板載內(nèi)存中。 (查看下面關(guān)于“波形生成延遲實(shí)現(xiàn)”的內(nèi)容,了解包絡(luò)波形時移算法。) 最后,多個設(shè)備可通過TClk來進(jìn)行同步和初始化。

圖7. 圖為生成ET所需的RF和包絡(luò)波形所必需的軟件流程簡圖。

同步基帶包絡(luò)發(fā)生器和RF信號發(fā)生器所需的軟件相對簡單。 VSG和AWG共享同一參考時鐘后,NI-TClk便可用于同步環(huán)節(jié)。 此時,對AWG和VSG生成的波形進(jìn)行相位鎖定,兩個波形之間存在可重復(fù)延遲。 該延遲是由于NI-TClk沒有計算NI PXIe-5450 AWG到NI PXIe-5611 I/Q調(diào)制器之間的模擬路徑而產(chǎn)生的(詳見圖5)。 由于該延遲為常數(shù),因此可通過設(shè)置AWG相對于VSG的延遲來進(jìn)行消除。 對于許多ET應(yīng)用,AWG相對于VSG的延遲(或VSG相對于AWG的延遲)對于找到延遲優(yōu)化設(shè)備性能至關(guān)重要。 該延遲必須是可重復(fù)的,且具有最低程度的抖動,這是因?yàn)榫退阊舆t只偏離最佳值幾納秒,也會使設(shè)備的線性度減少若干個dB。

波形生成延遲實(shí)現(xiàn)

記住:VSG和AWG之間的延遲控制對于ET芯片測試和特性記述是至關(guān)重要的。 該延遲可通過在硬件中添加等待采樣和偏移采樣時鐘或通過在軟件中使用DSP來實(shí)現(xiàn)。 雖然在硬件中可實(shí)現(xiàn)該延遲,但是它需要ET波形重新采樣至200 MHz才能指定納秒級分辨率的延遲。 由于并非每個用戶都能夠?qū)Σㄐ芜M(jìn)行重新采樣,因此我們更傾向于在軟件中實(shí)現(xiàn)延遲。

2. 結(jié)果

在NI LabVIEW系統(tǒng)設(shè)計軟件和ANSI C中均附有用于同步波形并可讓用戶能夠?qū)崿F(xiàn)一個波形相對另一個波形的皮秒級分辨率延遲的范例代碼。項(xiàng)目范例位于本文結(jié)尾處。 圖9 顯示的是使用NI PXIe-5154 1 GHz數(shù)字化儀進(jìn)行數(shù)據(jù)采樣的LabVIEW采樣代碼的典型結(jié)果。 在本范例中,基帶包絡(luò)信號僅為經(jīng)換算的LTE波形幅度。 從圖中我們可以看出基帶包絡(luò)與RF波形是一致的。

圖9. RF LTE波形與基帶包絡(luò)

圖10顯示的是LabVIEW ET演示操作的前面板界面。 除了一些標(biāo)準(zhǔn)的硬件資源控件外,還有其他一些參數(shù)也值得說明一下。 首先是波形IQ率。 本操作演示中,假定RF和包絡(luò)波形均以相同的速率采樣,速率可以是任意值。 之前我們討論的,如果要以任意量延遲包絡(luò)和RF波形,兩個波形均要以200 MHz的頻率重新采樣。第二個重要參量是是AWG相對VSG的延遲控件。 控件實(shí)際上用于控制包絡(luò)相對于RF波形的延遲,可通過輸入負(fù)值來控制RF波形相對于包絡(luò)的延遲。

從圖9的RF和包絡(luò)波形中,我們很難確定精度為納秒級的波形延遲是否與預(yù)期一致。 圖10中的波形圖顯示的是一個RF和包絡(luò)波形范例導(dǎo)出的數(shù)字化標(biāo)記事件。 使用標(biāo)尺,可以看到,RF波形相對于包絡(luò)延遲了7 ns,這主要是由于NI PXIe-5611上變頻器的路徑延遲和電纜長度差異。 如果要使兩個波形完全重疊,則 AWG相對于VSG控件應(yīng)設(shè)置為7 ns,如圖11所示。

圖10. LabVIEW ET演示操作前面板: 標(biāo)記事件從VSG和AWG中導(dǎo)出。 使用標(biāo)尺,可以看到RF波形相對于AWG延遲了7 ns。

圖 11. RF波形和包絡(luò)波形之間的7 ns延遲可通過延遲AWG 7 ns進(jìn)行補(bǔ)償。

使用傳統(tǒng)的直流電源會消耗大量的電能,這使得對于LTE功率放大器而言,ET性能就變得至關(guān)重要。 雖然該技術(shù)有望顯著提高PA效率,但是修改現(xiàn)有測試和特性記述設(shè)置來適應(yīng)ET是一件非常困難且成本不菲的挑戰(zhàn)。 借助NI平臺和本文提供的采樣代碼,您可以對現(xiàn)有NI PXI功率放大器測試站進(jìn)行改進(jìn),以支持ET,且所花費(fèi)的成本和時間遠(yuǎn)低于傳統(tǒng)臺式設(shè)備所要求的。

電子發(fā)燒友App

電子發(fā)燒友App

評論