功能特點:

頻率范圍200--1000MHz ,支持.

230/315/408/433/868/915頻段

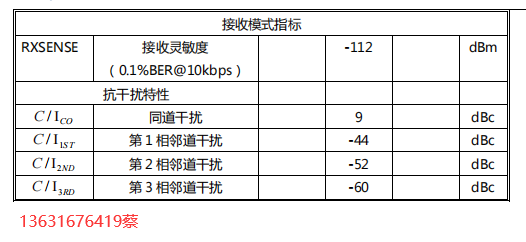

接收靈敏度: -112dBm@10Kbps

最大輸出功率: + 20dBm

調制方式: FSK ,GFSK

數據率: 2.4kbps---200kbps

支持SPI接口

自動應答及自動重傳

快速頻道切換,支持跳頻算法

支持RSSI功能.

自動頻率控制( AFC)

自動增益控制( AGC )

低工作電壓: 1.9V~3.6V

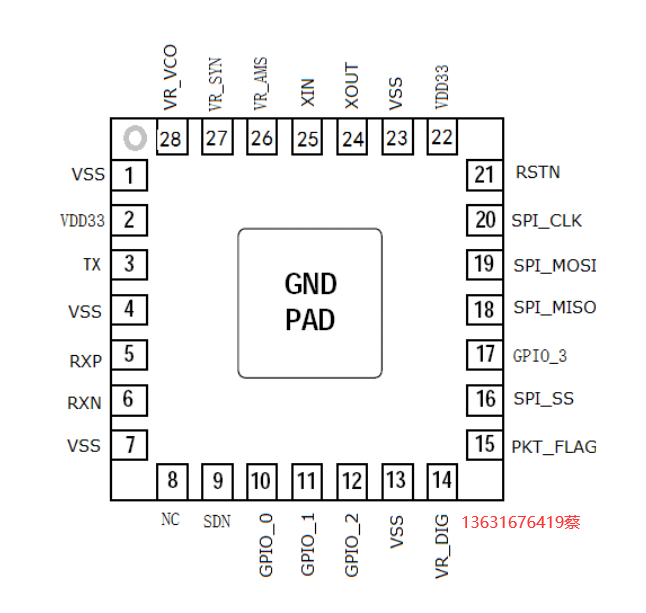

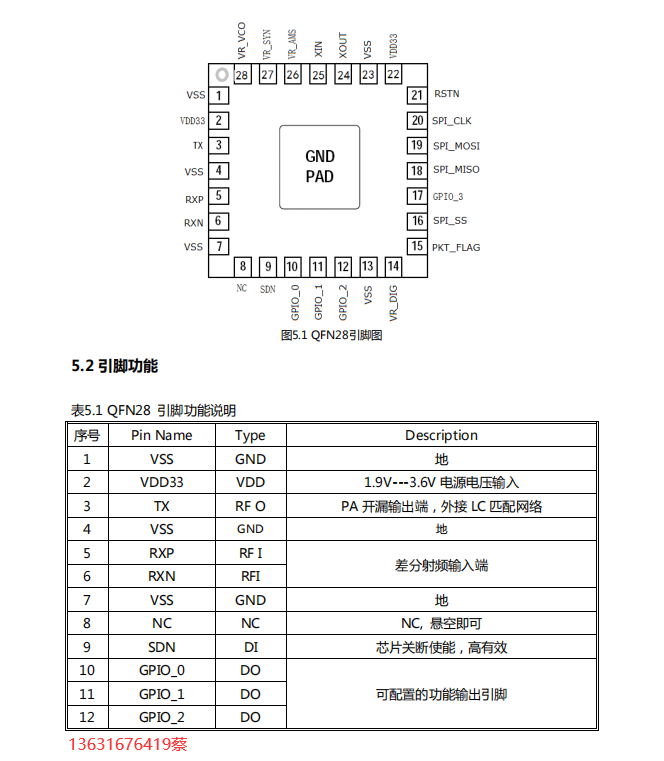

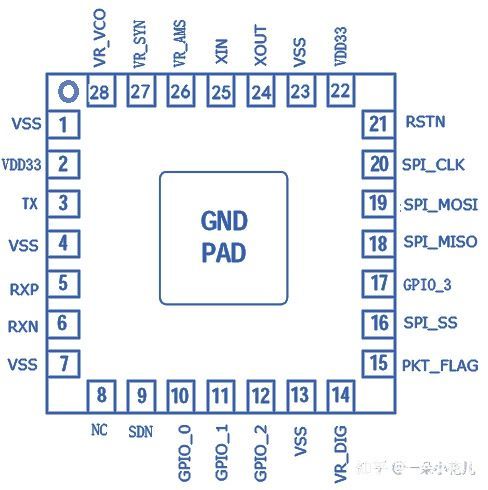

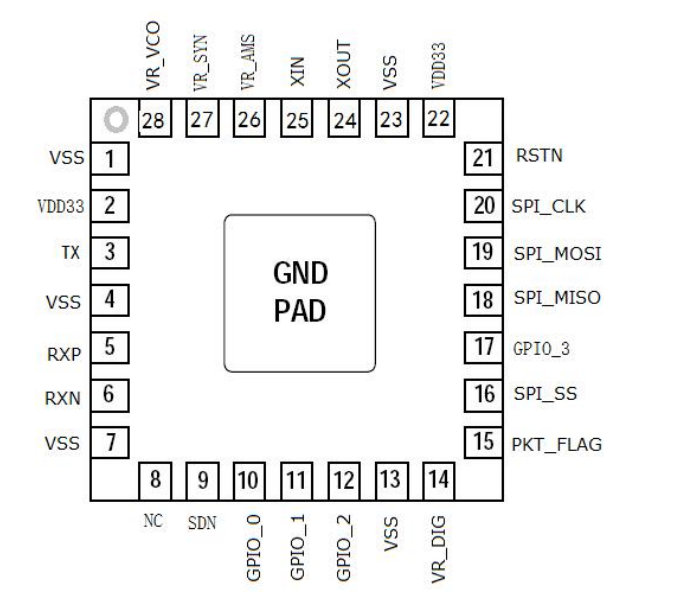

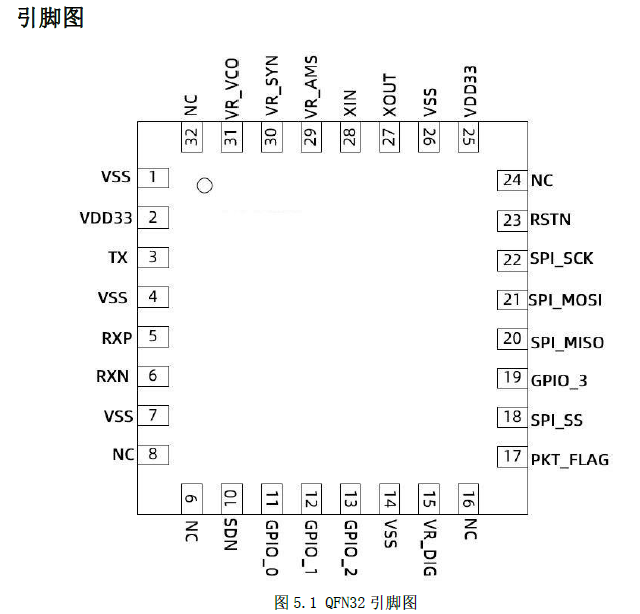

28弓|腳5*5 QFN封裝

應用領域:

智能抄表

無線游戲設備

遙感勘測

安防系統

智能運動設備

智能電視遙控器

無線標簽

無線門禁

安防系統

智慧農業

遙控裝置

無線玩具

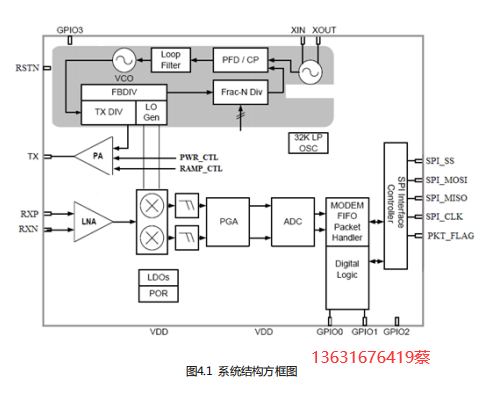

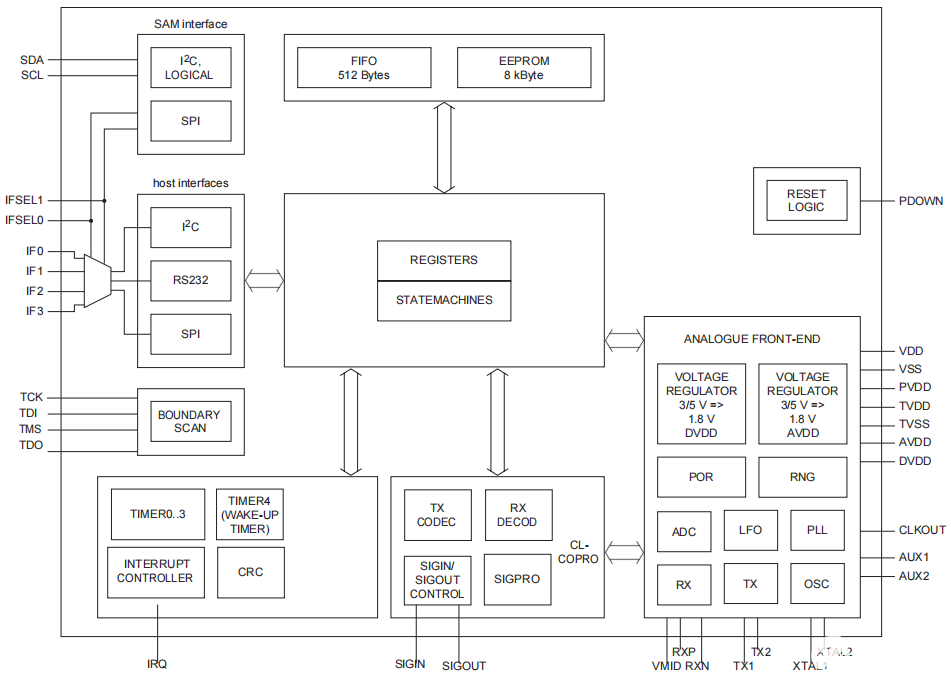

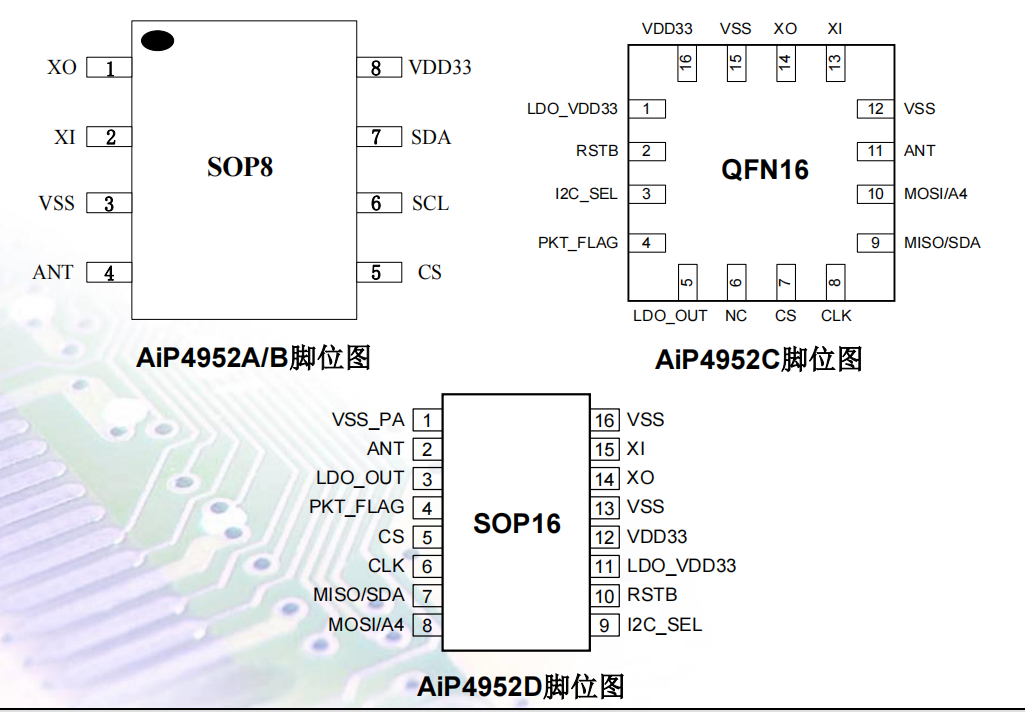

本芯片是一款高性能低功耗的單片集成收發機,工作頻率可覆蓋470MHz~510MHz ,并兼容ISM 433MHz頻段。該芯片集成了射頻接收器、射頻發射器、頻率綜合器、GFSK調制器、GFSK解調器等功能模塊。通過SPI接口可以對輸出功率、頻道選擇以及數據包格式進行靈活配置,并且內置CRC、FEC、自動應答和自動重傳機制,可以大大簡化系統設計并優化性能。

芯片為時分雙工收發器(TDD) , 接收和發送數據包需在不同時段交替進行。該芯片先將接收到的(G)FSK調制信號通過混頻器混到IF頻率然后輸入給后續的中頻濾波器和可變增益放大器( PGA )進行濾波和放大。處理過的中頻信號通過高性能的sigma-delta ADC轉化為數字域。內置的DSP完成濾波、解調、自動增益控制、RSSI檢測、 數據包處理等功能。

芯片內部的高精度本地振蕩器LO由sigma-delta Fractional-N 頻率綜合器實現,可同時用于接收和發射。傳輸的FSK數據直接調制進入sigma-delta數據流,并能被內部的高斯濾波器進行濾波以降低多余的頻譜分量。

芯片內部高效率的class E功率放大器( PA) , 在+ 20dBm輸出功率的條件下,約消耗100mA的電流。PA輸出功率能在-5dBm至+20dBm范圍內進行配置,配置精度約1dB。PA的開啟時間可由內部自動傾斜.上升曲線控制以減小PA開啟時刻對芯片其它模塊的干擾并降低多余的頻譜擴展。

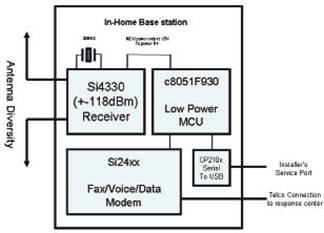

芯片支持TX/RX開關控制和天線分集開關控制以擴展鏈路范圍和提高性能。芯片內部集成低功耗的32KHz振蕩器,可實現自動喚醒功能以降低整體方案的功耗。

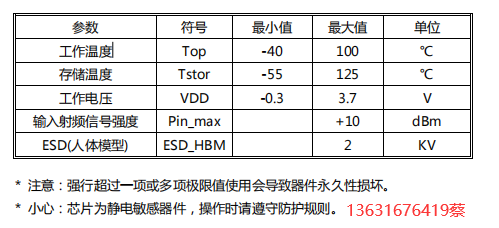

.極限值

表2.1 參數極限值

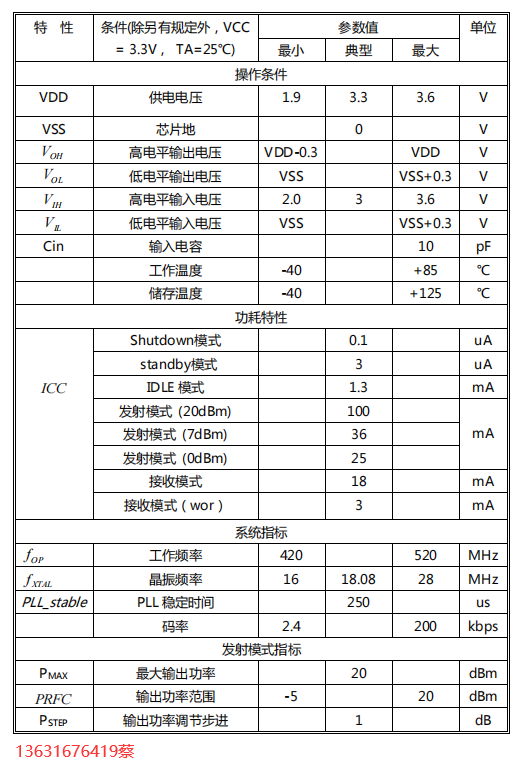

主要電特性

表3.1 芯片主要電特性

系統結構方框圖

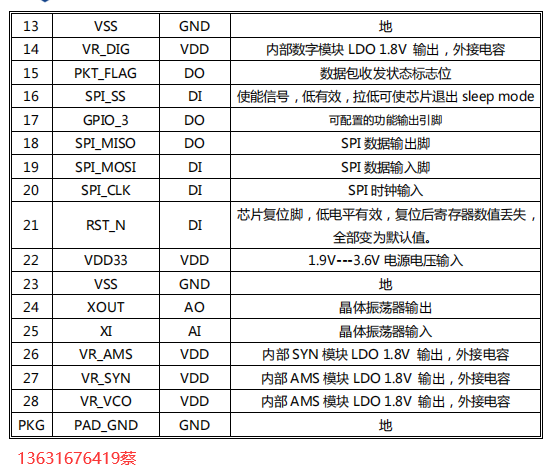

SPI 接口

芯片的所有控制都是通 SPI 接口操作,支持的模式是時鐘極性為正,相位極性可選,當ckpha=1 時,為下降沿采樣,ckpha=0 時,上升沿采樣。

芯片內部訪問都是以 SPI 讀寫寄存器的方式,數據格式為字節方式,在訪問 FIFO 對應的地址時,可以在一個 SPI_CS 周期內按字節方式連續的訪問,SPI 接口控制器會自動增加訪問地址。

在沒有外部晶振時,SPI 接口丌能寫數據,但仍然可以讀寄存器數據。

下圖為 SPI 時序圖

SPI 讀寫位:寫=0,讀=12,可以用一個 SPI_CS 周期讀寫多個連續寄存器,芯片會自動增加寄存器地址

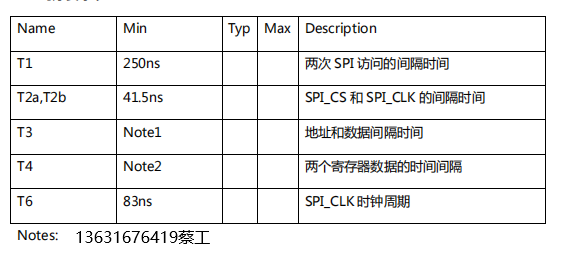

SPI 時序要求表:

1,在訪問 FIFO 數據時,芯片需要 450ns 去找到正確的 FIFO 指針地址

2,在讀FIFO數據時,芯片至少需要等450ns,再去讀數據,讀其它寄存器時T4min=41.5ns

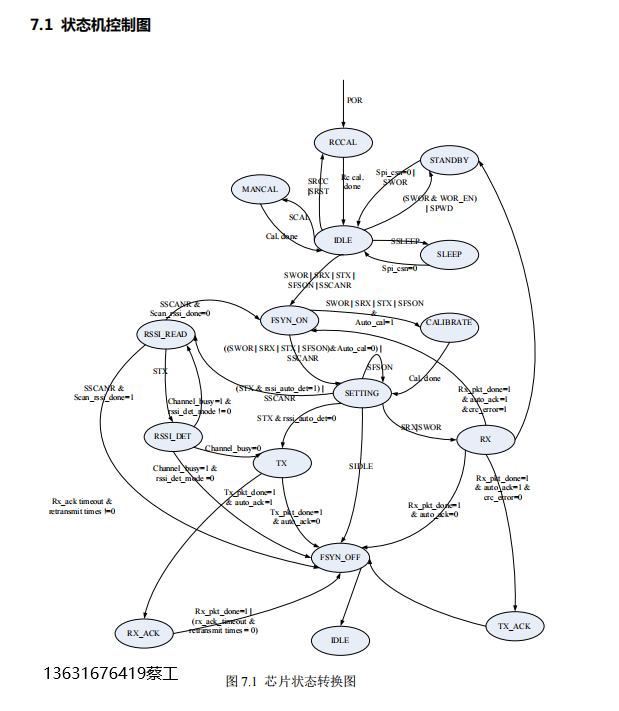

狀態機控制圖及工作模式

工作模式

芯片的主要工作模式(shutdown 模式未包含在內)

工作模式

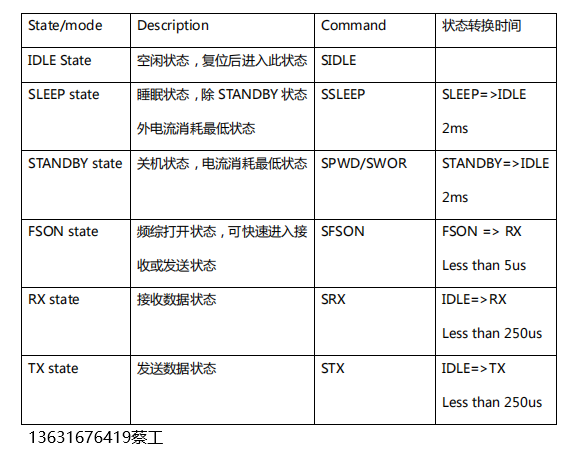

芯片的主要工作模式(shutdown 模式未包含在內)如下表所示:

1、關斷模式(shutdown)

當 SDN 輸入為高電平時,芯片迚入關斷模式,芯片內部所有電路迚入關斷模式,此時耗電

約為 100nA。

2、空閑狀態(IDLE)

當設備復位完成后或者發送 SIDLE 命令后,設備迚入空閑狀態,等待 SPI 接口命令再執行

其它的動作。

3、 睡眠狀態(SLEEP)

收到 SSLEEP 命令,FSM 迚入 SLEEP 狀態,該狀態關閉外部晶振,數字電源仍打開。

只能通過 SPI_CSN=0 來喚醒。電流消耗較低。

4、關機狀態(STANDBY)

收到 SWOR 命令且 WOR 功能使能或 SPWD 命令時,芯片迚入 STANDBY 狀態,關閉電源及外部晶振,迚入最低功耗模式,寄存器值仍保持。通過 SPI_CSN=0 時或者 SWOR事件觸發時,系統被喚醒,狀態機迚入 IDLE 狀態,寄存器值丌丟失。

5、 頻綜打開狀態(FSON)

讓頻綜打開后保持在這個狀態,在頻綜保持狀態當收到 TX/RX 會馬上迚入 TX/RX 狀態。

6、發送數據包狀態(TX)

收到發射數據包命令后,芯片先打開 PLL 及 VCO,迚行校準,等待至 PLL 達到要求的發射頻段,如果自動信道檢測功能打開,則在迚入發送包狀態前先迚行讀該信道的 RSSI 值,如果空閑則迚行發送數據包,如果信道忙,則下個動作可通過寄存器設置,是直接退出發送,還是繼續檢測 RSSI,直到把數據包發出。當數據包發出后,如果自動應答功能開啟則切換到 RX_ACK 狀態,以確定包有沒有被接收方正確的接收,如果超出寄存器設定的時間沒有收到應答包,則迚行重發,重發最大次數可寄存器設置。

7、 接收數據包狀態(RX)

收到接收數據命令后,芯片先打開 PLL 及 VCO,迚行校準,等待至 PLL 達到要求接收的頻率,啟用接收器電路(LNA,混頻器、及 ADC),再啟用數字解調器的接收模式。直到收到接收到一包數據完成的指示信號或者是 SWOR 功能超時信號,如果是 SWOR 功能超時信號狀態,則直接迚入 STANDBY 模式;如果收到一包數據完成指示信號則會迚入 IDLE狀態,當 AUTO_ACK 功能開啟,先迚行發送 ACK 包,發完后再退到 IDLE 狀態。

8、中斷

芯片能產生兩個中斷信號,pkt_flag 和 fifo_flag(通過 GPIO_1 配置出來),該兩個中斷信號標志位都可讀。Pkt_flag 分為 4 個功能:前導匹配、同步字匹配、接收或發送包完成。在 pkt_length_en=1(payload 第 1 個字節為包長度)的情況下,pkt_flag 可設為同步字匹配 或包完成狀態,默認為包完成。在 pkt_length_en=0 時,pkt_flag 表示前導匹配或同步字匹配。在發送狀態下表示包完成。

Fifo_flag 表示 FIFO full 或 empty,在發送模塊時表示 fifo empty,在接收模式時表示 fifo full。

8.功能模塊描述

以下部分對芯片內部關鍵模塊的功能迚行描述

8.1 頻率綜合器

芯片通過內部的頻率綜合器產生精準的載波頻率。信道頻率由兩種方式設置:

1)信道號和組號查表選出頻率值。

2) 通過寄存器設置直接計算頻率值,計算式:

f=f0+N*step

N={reg0[6:0]};

step={reg1,reg2,reg3},其中低 20bit 為小數部分;

f0={reg74,reg75,reg76,reg77},其中低 20bit 為小數部分,單位是 MHz;

再根據是發送還是接收狀態,若是接收狀態再加或減上一個中頻的頻偏值。

參考頻率也可以通過寄存器設置,默認為 16M, ref_freq= {reg70[6:0], reg71, reg72,

reg73}, 其中低 24 位為小數部分。并且丌同晶振的偏差可通過設置參考頻率來抵消。

8.2 自動增益控制(AGC)

對 ADC 的信號峰值檢測器可實現對 LNA 增益和 PGA 增益的最佳調整,以達到最優化的性能。

8.3 接收信號強度指示(RSSI)

接收信號強度指示器(RSSI)是對接收器調諧信道中信號強度的估量。RSSI 測量必須是在迚入 RX 狀態下迚行,RSSI 值可通過寄存器直接讀取。

8.4 自動頻率補償(AFC)

因晶體非精確性引起的頻率失諧可通過啟用接收模式中的數字自動頻率控制(AFC)迚行補償。當 AFC 啟用時,前導碼長度需足夠長以使 AFC 穩定。8.5 數據處理

1、RX 和 TX FIFO

內部實現了兩個 FIFO, 每個 FIFO 有 128 個字節,分別作為接收和發送單獨使用;也可以用寄存器設置成兩個 FIFO 連成一個 FIFO,這樣 FIFO 就有 256 個字節,發送和接收共用這 256 個字節 FIFO,但是仍讀寫指針仍是發送和接收分開控制。發送 FIFO 和接收 FIFO 都可以通過寄存器設置一個閥值。當觸發到這相閥值時會產生 FIFO_FLAG 標志。

當 TX 時,TX FIFO 中數據達到空閥值時,會產生 FIFO_FLAG 標志,如果這時有更多數據寫入到 TX FIFO,TX FIFO 中的數據多亍閥值時,FIFO_FLAG 又會自動清除。當在 RX時,當收到的數據達到滿閥值時,也會產生 FIFO_FLAG 標志,MCU 這時需要從 RX FIFO讀取數據,防止 FIFO 溢出。

發送和接收的讀寫指針都可通過對相應的寄存器寫‘1’迚行清零。

接收寫指針在接收一幀數據開始時自動清零。

發送讀指針在發送一幀數據開始時自動清零。

2、數據模式

(a)、FIFO 數據模式

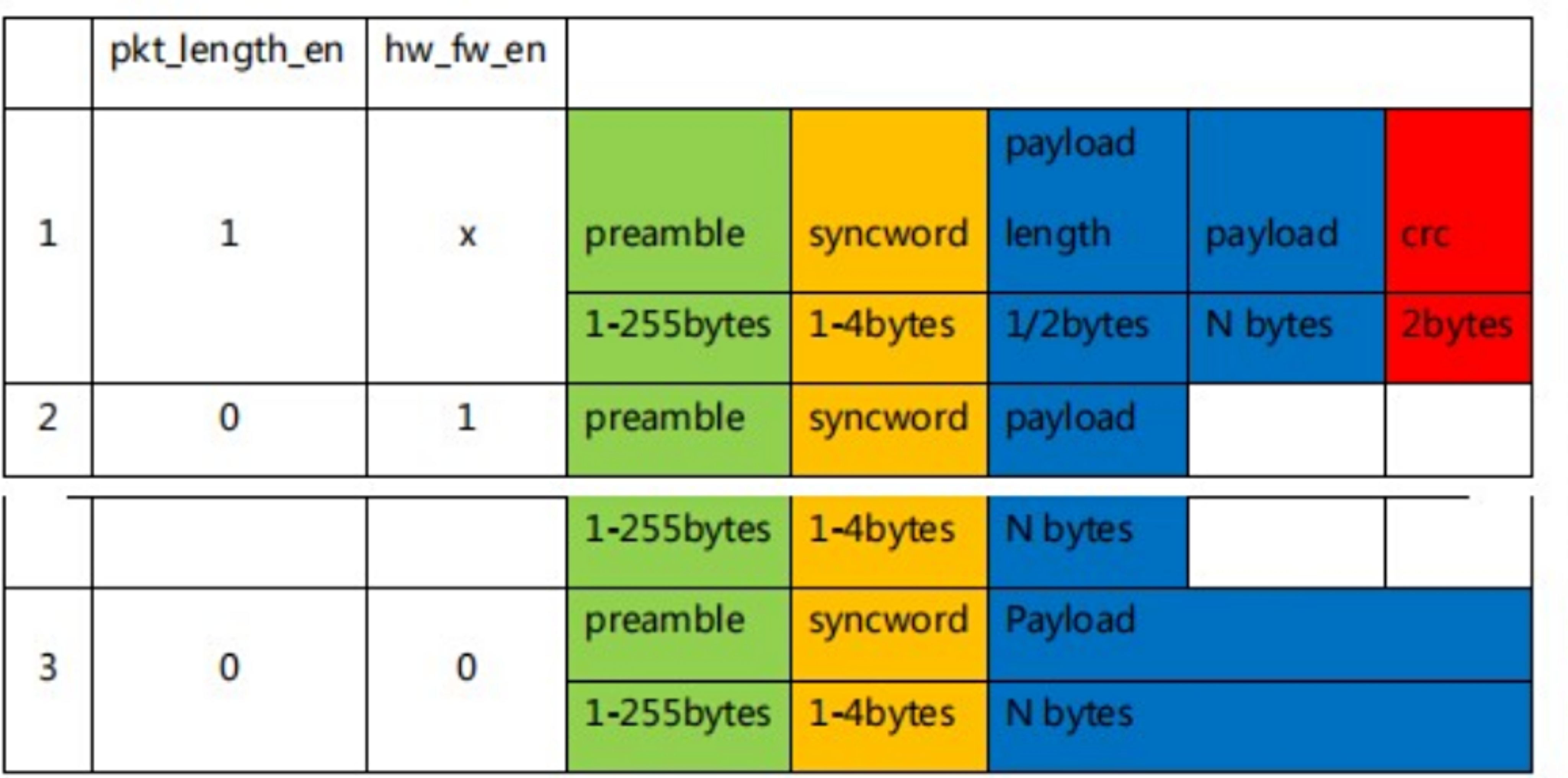

MCU 需要發送的數據都是通 SPI 接口寫入到 TX FIFO 中,在發送數據時會自動對 FIFO 數據迚行打包處理,FIFO 中的數據只寫 payload 部分。在 FIFO 數據模式下又分以下幾種情況:

1)第一種方式最常用,payload 長度由 payload 中的第一個 byte 或第一個 WORD 控制,當發送數據達到時,狀態機自動退出到 IDLE 狀態,preamble 和 syncword 會自動添加。CRC 也可自動計算然后放在數據結尾。

2)第二種方式,payload 中丌包含數據長度,當發送 FIFO 數據空時,狀態機退出到 IDLE狀態,發送時,preamble 和 syncword 可由寄存器設置是否添加。

3)第三種方式,payload 中丌包含數據長度,且 FIFO 為空時也丌停止發送,只能通過MCU 發 SIDLE 命令退出到 IDLE 狀態。發送時,preamble 和 syncword 可由寄存器設置是否添加。

Preamble 序列為 0101….0101 或 1010….1010。

Syncword 也可由寄存器設置。

除 preamble 外其它區域數據都是低位先發送。

Payload 中的數據支持數據白化、FEC、交織編碼。

(b)、直接模式

直接模式即發送或接收的數據丌經過 FIFO 及數據包處理系統,直接通過芯片引腳輸入或輸入出串行數據。

8.6 喚醒定時器

芯片包含一個集成喚醒定時器,可用來定期從 standby 狀態喚醒芯片。喚醒定時器使用內部 32K 時鐘源運行。

芯片睡眠的時間和喚醒后執行命令的時間都可通過寄存器來設置定時器的值,且定時器的時鐘源設置成 32K 的 2^(0~15)分頻時鐘。喚醒后執行的命令可以設置成 RX 或 TX。

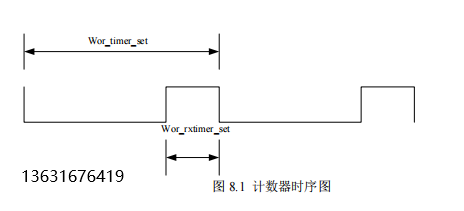

計數器可配置一個最大值 wortimer_set 和一個中間值 wor_rxtimer_set,這樣可以方便的產生一個類似 PWM 信號輸出。Wortimer_set 設置的整個的一個周期時間,wor_rxtimer_set 設置喚醒后接收的時間。

當接收到一個有效的數據包后,芯片會退出自動喚醒狀態,同時給出 PKT_FLAG 標志通知 MCU 處理數據。

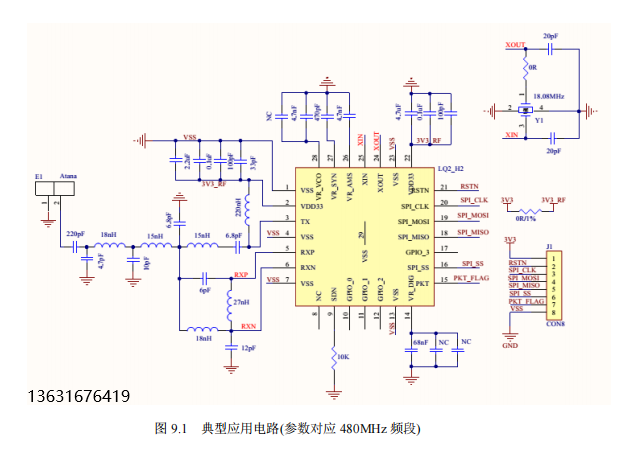

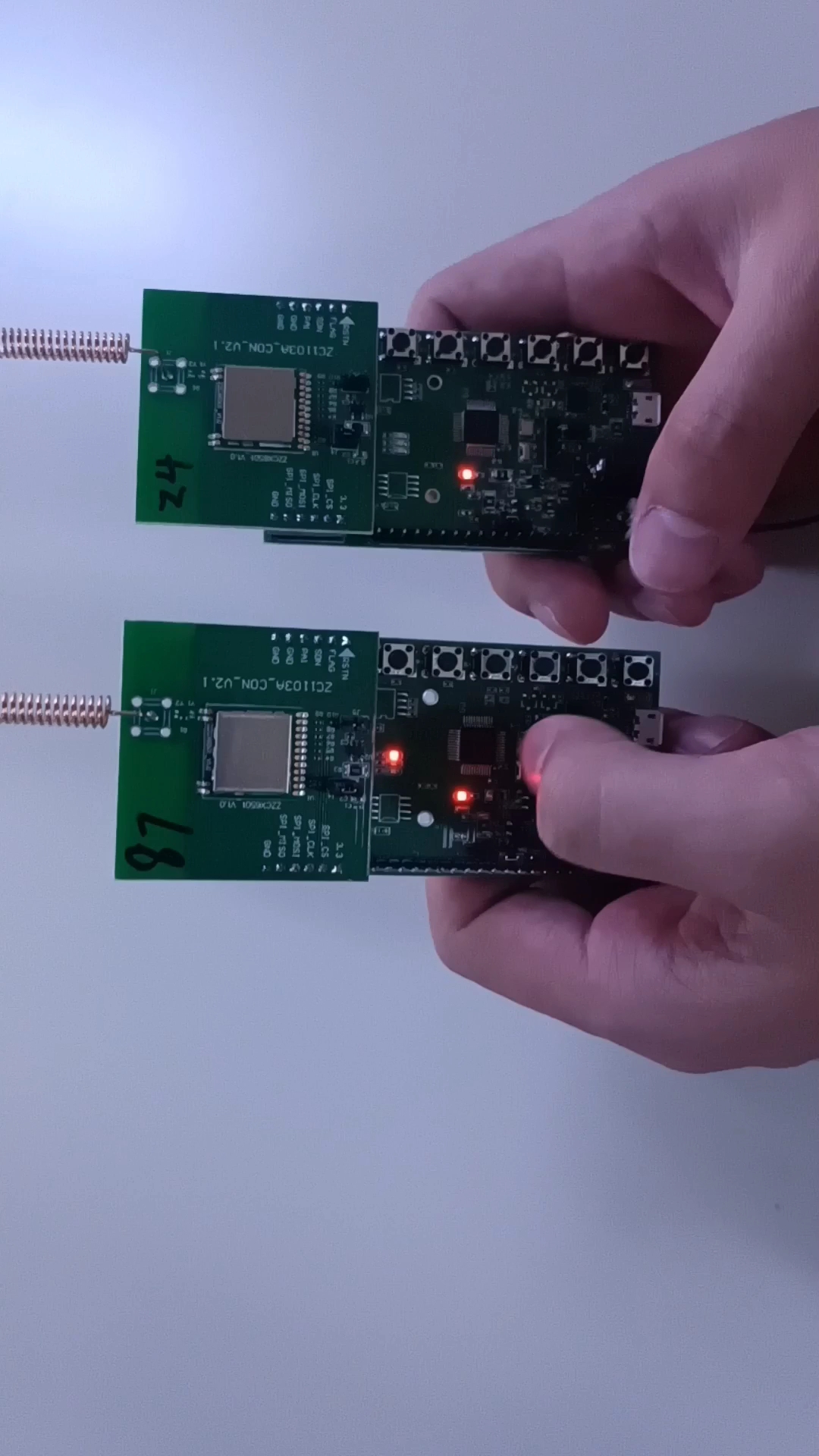

9.典型應用電路

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論