零中頻(ZIF)架構自無線電初期即已出現。如今,ZIF架構可以在幾乎所有消費無線電應用中找到,無論是電視、手機,還是藍牙技術。ZIF技術取得的最新進步對現有高性能無線電架構形成了挑戰,其帶來的新產品取得了性能上的突破,能夠實現ZIF技術以前望塵莫及的新型應用。本文將探討ZIF架構的諸多優勢,介紹這些優勢如何使無線電設計性能達到的新高度。

無線電工程師面臨的挑戰

不斷增多的需求給當今的收發器架構師帶來了挑戰,因為我們對無線設備和應用的需求呈持續增長之勢。結果,消費者需要持續訪問更多的帶寬。

數年以來,設計師已經從單載波無線電走向多載波無線電技術。當一個頻段的頻譜被全部占用時,就分配新的頻段;目前,必須為40多個無線頻段提供服務。由于運營商在多個頻段都有頻譜,并且這些資源必須協調起來,所以,如今的趨勢是走向載波聚合,而載波聚合則會導致多頻段無線電。這又會帶來更多的無線電,其性能更高,需要更優秀的帶外抑制性能,更出色的輻射性能,以及更低的功耗水平。

雖然無線需求在快速增長,但功耗和空間預算并未增長。事實上,在功耗和空間節省需求不斷增強的條件下,同時降低碳排放和物理尺寸非常重要。為了實現這些目標,需要從新的視角去認識無線電架構和分區。

集成

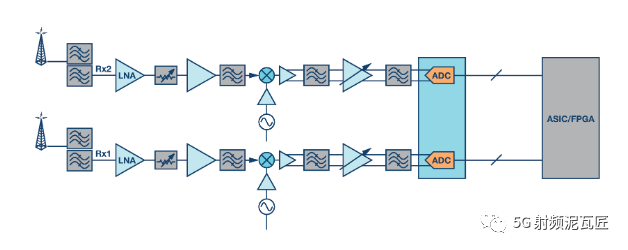

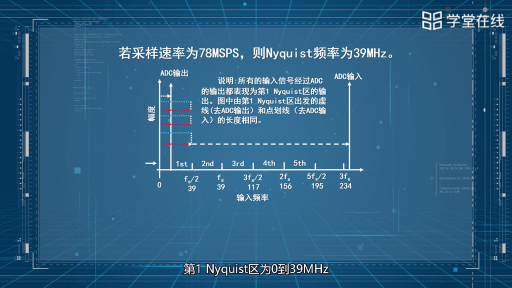

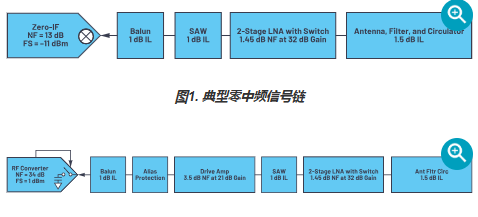

為了增加特定設計中的無線電數目,必須減小每件無線電器件的尺寸。傳統方法是逐步把更多的設計集成到一片硅片當中。雖然從數字角度來看,這樣做可能是合理的,但是,為了集成而集成模擬功能的做法不見得有意義。其中一個原因是,無線電中的許多模擬功能是無法有效集成的。例如,在圖1所示的傳統中頻采樣接收器中,中頻采樣架構有四個基本級:低噪聲增益和射頻選擇級、頻率轉換級、中頻增益和選擇級以及檢測級。選擇級一般使用SAW濾波器這些器件都不能集成,因此,必須部署在片外。雖然射頻選擇級是由壓電或機械器件提供的,但有時中頻濾波器會使用LC濾波器。盡管LC濾波器有時可能會集成到單片結構中,但是,濾波器性能的犧牲(Q和插入損耗)以及數字化器(檢波器)采樣速率必要的增加會提高總功耗。

圖1.傳統型中頻采樣接收器

數字化器(模數轉換器)必須以低成本CMOS工藝制成,以使成本和功耗保持于合理水平。當然可以用雙極性工藝制造,但結果會導致器件尺寸和功耗的增加,有悖于優化尺寸的初衷。所以,標準CMOS工藝是這種功能的最佳制造工藝。這就為集成高性能放大器,尤其是中頻級,造成了極大的挑戰。雖然CMOS工藝可以集成放大器,但是很難從針對低功耗和低電壓而優化過的工藝中取得需要的性能。另外,在片上集成混頻器和中頻放大器要求把級間信號路由到片外,以便訪問中頻和抗混疊濾波器,然后再數字化,因而失去了集成的諸多優勢。這樣做就達不到集成的目的,因為結果會增加引腳數和封裝尺寸。另外,關鍵的模擬信號每次通過一個封裝引腳時,就會犧牲一些性能。

最佳集成方式是對系統分區,消除不能集成的元件。

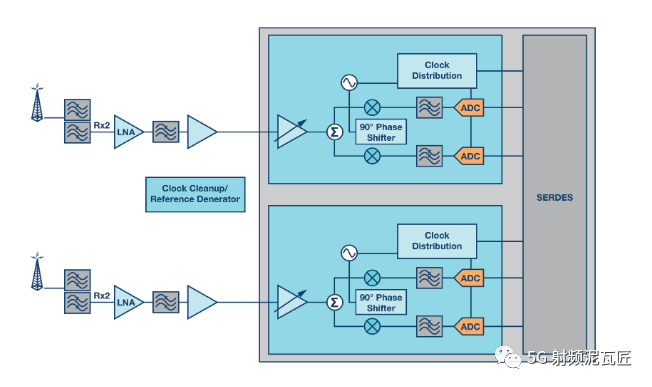

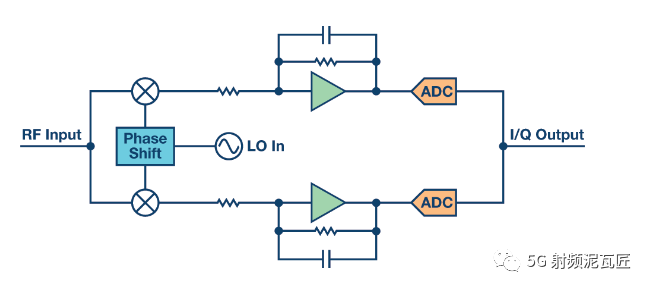

由于不能有效地集成SAW和LC濾波器,所以,最佳選擇是確定如何通過重新設計架構來消除它們。圖2展示了一個典型的零中頻信號鏈,它把射頻信號直接轉換為一個復合基帶,完全消除了中頻濾波器和中頻放大器的必要性,結果實現了這些目標。選擇級則通過在I/Q基帶信號鏈里引入一對低通濾波器的方式予以實現,這對濾波器可以作為有源低通濾波器而非功耗較高的片外固定中頻器件集成。傳統型中頻SAW濾波器或LC濾波器天生就是固定型器件,而這些有源濾波器則可以電子方式,在數百kHz至數百mHz的范圍內調諧。改變基帶帶寬就能使同一器件覆蓋范圍更寬的帶寬,無需改變物料清單,也不用在不同的固定中頻濾波器之間來回切換。

圖2.典型的零中頻采樣接收器

雖然圖示并不直觀,但通過更改本振,零中頻接收器也可覆蓋范圍非常寬的射頻頻率。零中頻收發器可提供真正的寬帶體驗,典型連續覆蓋范圍從數百MHz到約6GHz。不使用固定濾波器,可以實現真正靈活的無線電,結果可以極大地減少,甚至可能消除在開發無線電設計頻段變體方面的投入。得益于靈活的數字化器和可編程的基帶濾波器,零中頻設計不但能實現高性能,還具有極大的靈活性,既能支持范圍超寬的頻率和帶寬,也能維持近乎平坦的性能,而且無需針對每種配置優化模擬電路(如濾波器)—可謂名符其實的軟件定義無線電(SDR)技術。與此同時,這種方法也會大幅減小尺寸,因為它為必須覆蓋多個頻段的應用消除了原本需要的濾波器組。在一些情況下,可以完全消除射頻濾波器,成就完全意義上的寬帶無線電,根據不需要更改頻段。通過消除部分器件、集成其他器件,可以大幅減小零中頻設計所需要的PCB尺寸,不但簡化了頻段高速過程,還能減少有必要更改尺寸時投入的精力。

最小的尺寸

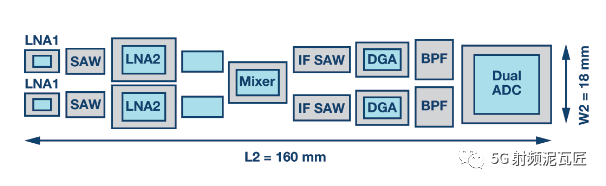

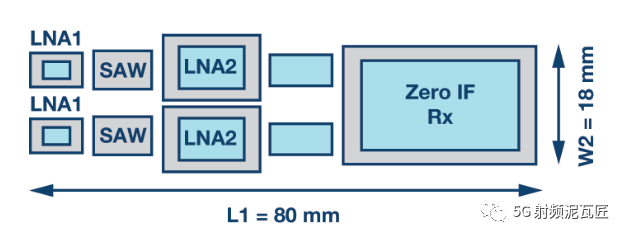

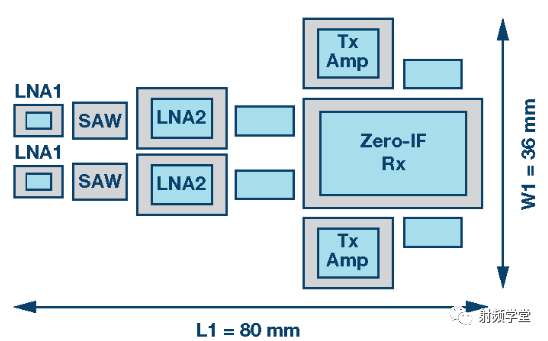

通過直接比較這些架構的PCB面積(圖3和圖4)可知,對于雙接收路徑,在合理實現方式下,中頻采樣和零中頻采樣的PCB面積分別為2880mm2 (18mm×160mm),和1434mm2 (18mm×80mm)。如果不算可能消除的射頻濾波器和其他簡化設計,2零中頻架構有可能比當前的中頻采樣技術減少最高達50%的無線電尺寸。未來的設計有可能通過額外的集成,使尺寸再減少一倍。

圖3.典型的中頻采樣布局圖

圖4.典型的零中頻采樣布局

?

最低成本

直接從物料清單來看,從中頻采樣系統轉向零中頻架構可節省33%的物料。成本分析始終都是非常困難的。然而,深入考察圖1和圖2可知,許多分立式元件均已消除,包括中頻和抗混疊濾波元件,并且混頻器和基帶放大器均已集成。不明確的是,由于零中頻接收器本身具有傳統中頻采樣架構不具備的帶外抑制功能,所以,整體外部濾波要求就大幅降低了。零中頻架構中兩個元件促成了這一結果。第一個元件是有源基帶濾波器,該濾波器同時具備帶內增益和帶外抑制功能。第二個元件是高采樣速率低通Σ-Δ轉換器,用于對I/Q信號進行數字化。有源濾波器減少了帶外元件,而ADC的高采樣速率則使混疊點提高到足夠高的頻率,從而消除了外部抗混疊濾波元件的必要性(因為有源濾波器已經充分地抑制了信號)。

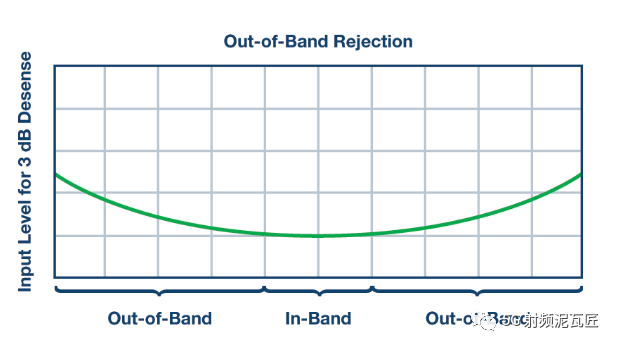

通過把基帶信號施加到有源濾波器上,如圖5所示,可以滾降高頻內容。然后,ADC對來自低通濾波器的任何殘余輸出信號進行數字化和最終濾波。

圖5.有源基帶濾波器與ADC

級聯結果如圖6所示。此圖所示為在有源濾波器和Σ-ΔADC復合效應作用下的典型接收器性能。這里展示的是帶內和帶外功率靈敏度降低3dB的典型情況。注意,在不使用任何外部濾波元件的情況下,帶外性能有所改善。

圖6.典型的零中頻帶外抑制

為了獲得類似的性能水平,中頻采樣接收器采用分立式中頻濾波元件(如SAW技術)來實現選擇性和帶外信號保護功能,以防止寬帶信號混疊和噪聲混疊回頻段等問題。中頻采樣架構還必須采取其他無用混頻器項的保護措施,包括半中頻項,該項會提高射頻和中頻濾波要求并限制采樣速率和中頻規劃。零中頻架構不存在這種頻率規劃限制。

根據設計和應用的不同,這種原生抑制功能可以降低或消除外部射頻濾波要求。通過省去這些元件可以直接節省成本,因為根據類型的不同,外部射頻濾波器可能比較昂貴。另外,移除這些損耗性的器件有助于消除射頻增益級,結果不但能節省成本,同時還能降低功耗、提高線性度。所有這些都可進一步增強分區和智能集成的優勢。

如前所述,成本的估算非常難,因為這在很大程度上取決于產量和與供應商簽訂的協議。然而,詳細分析顯示,通過集成、消除部分元件、降低要求,零中頻架構最高可使系統總成本降低三分之一。需要記住的是,這是系統成本,不是器件成本。由于更少的器件要承載更多的功能,所以在系統總成本減少的情況下,有些器件成本可能會增加。

除了材料成本以外,集成式零中頻接收器還有一些其他優勢。由于集成式系統可以減少系統中的器件數量,所以其裝配成本較低,工廠良品率較高。由于分立式器件數量變少,所以對齊時間也會變短。這些因素相加,可降低工廠成本。

由于零中頻接收器是名符其實的寬帶,所以,調整頻段的工程成本也減少了。在中頻采樣系統中,必須慎重選擇中頻頻率,但對于零中頻系統,則無需進行謹慎的規劃。基本上通過更改本振就可以添加新的頻段。另外,由于在使用零中頻時,許多應用并不要求外部射頻濾波器,所以,結果可能實現進一步的簡化。整體而言,對于零中頻解決方案,如果考慮直接成本以及上面列出的制造成本和工程成本,其成本節省優勢是非常可觀的。

最低功耗

如果只是采用圖1所示架構,并直接將其集成到片上系統中,結果并不會帶來功耗和成本上的優勢。要節省功耗,就要選擇高效的架構,該架構能針對目標工藝進行優化。類似于圖中所示中頻采樣接收器的架構涉及到大量的高頻和中頻頻率,難以在低成本工藝的基礎上進行擴展,因此,要消耗大量功率以支持所需頻率。然而,如圖2所示的零中頻架構能立即降低至直流(基帶)的目標頻率,因而可以實現頻率最低的電路。

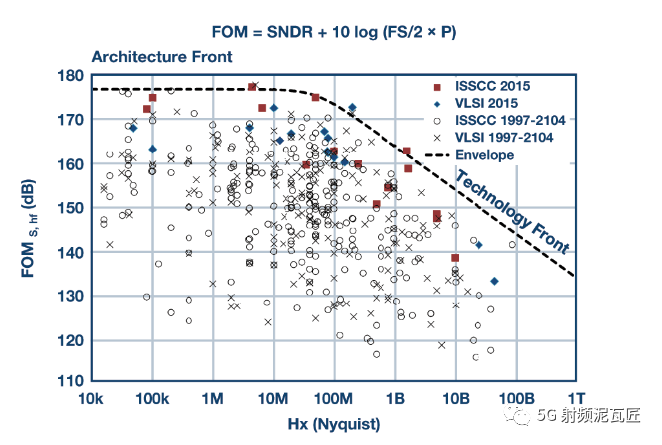

類似地,通過帶寬來解決這個問題也是非常低效的。類似于直接射頻采樣的架構可提供較寬的帶寬,并且具有極大的靈活性。然而,據Walden3 和Murmann.4在文中所述,增加系統帶寬始終都會提高功耗。

除非需要原始帶寬,否則,對多數接收器應用來說,僅僅通過帶寬來解決這個問題并不是一種經濟的解決方案。這些長期研究的數據表明,轉換器的發展有兩個方面值得關注。技術面取得了一些進步,能以動態范圍和帶寬的形式顯著提高內核的交流性能。架構面在內核架構的整體效率方面有所進步。一般地,曲線先是向右移動,然后隨著設計的優化,開始向上運動。對于通信應用,操作趨向沿技術面進行,其中,從線條斜率來看,轉換器效率大約下降了10dB/十倍頻程,如圖7所示。在此斜率下,使帶寬增加一倍會導致功耗增加兩倍。然而,在把這些內核集成到功能器件中之后,效率就有所改善,當其靠近架構面時,功率損失接近2。

圖7.內核ADC技術的品質因數4

對于關心功耗的應用來說,結論是,功耗最低的解決方案是帶寬和采樣速率均針對應用而優化過的解決方案。搭載Σ-Δ轉換器的零中頻采樣設計就針對這類應用進行了優化。依據具體的應用,采用零中頻接收器比中頻采樣架構可節省50%或以上的功耗,比直接射頻采樣可節省高達120%的功耗。

功耗還與成本直接相關。更高的功耗不但會提高封裝成本和電源成本,而且對于電路消耗的每瓦特功率(設電費為12美分/千瓦時),每年每瓦特的運營成本會超過1美元。鑒于許多電子器件成本較低,其一年的運行成本就可能輕松超過其直接成本。因此,隨著集成式無線電解決方案選項的推出,對成本和功耗敏感的應用必須選擇謹慎地做出權衡。選擇會不必要地增加功耗的架構,結果不但會增加功耗,還可能會影響解決方案的長期運行成本。

性能增強

無線電設計有若干重要的關鍵指標需要注意。其中包括噪聲系數(NF)、線性度(IP3、IM3)、降敏、選擇性等。在正常的無線電規格以外,還有一些規格也很重要,但用戶往往看不到。其中包括規格分布和漂移與時間、電源、溫度和流程的關系。零中頻架構符合關于無線電設計的這些和其他關鍵要求。

通過溫度、電源和流程跟蹤

全集成式收發器架構的一個優勢是,對于設計合理的無線電,器件匹配可能要好得多,不僅在起初是這樣,而且如果設計合理,器件可以有效地進行流程、溫度、電源和頻率跟蹤。運用通常嵌入這些集成解決方案中的信號處理技術,可以較好地消除任何殘余的失配問題。雖然對IC設計來說,這是非常典型的情況,但是,無線電集成的不同之處在于,在零中頻設計中,由于依賴于頻率的所有項均部署于片上,所以,這些項也可以實現跟蹤功能。如圖1所示的典型無線電包括一個片外中頻濾波器。該中頻濾波器的特性會隨時間、溫度或器件而變化,與片上的任何元素均無關,并且不能對其進行跟蹤。然而,集成濾波器的一個主要優勢是,因為其以片上器件構建,所以,器件是可以擴展的,或者可以按比例相互跟蹤,以保持性能穩定。對于那些不能通過設計穩定的項,可以輕松進行校準。最終結果是,在預計器件差異時,所需要的裕量要遠遠低于所有器件均無關的分立式設計。

例如,為混頻器、中頻濾波器、中頻放大器和ADC各分配1dB的噪聲系數,這種做法并不罕見。在制定性能預算時,必須把這些差異級聯起來。然而,在集成式設計中,所有關鍵技術規格要么相互跟蹤,要么通過校準予以排除,結果可實現1dB的單一器件差異,極大地簡化了信號鏈差異。相比各項不相關的設計,這可能會對設計造成重要的影響;在各項不相關的設計中,需要額外的系統增益來抵銷可能會增加的噪聲—會影響到最終產品的成本、功耗和線性度。在如圖2所示的集成式設計中,性能總差異要遠遠小于不相關設計,因此,只需較小的系統增益。

高級校正技術

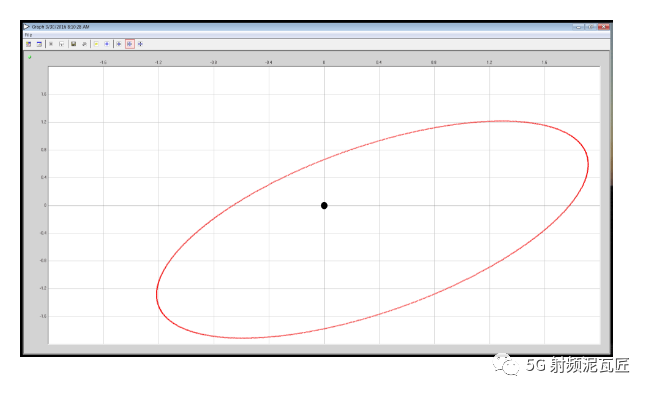

在過去,零中頻接收器通常有兩個領域會引起人們的擔憂。由于復合數據是用一對表示實部和虛部的實數級聯網絡生成和表示的,結果就產生了可能表示各信號鏈增益、相位和失調的誤差,如圖8所示。

圖8.表示增益、相位和失調項的正交誤差

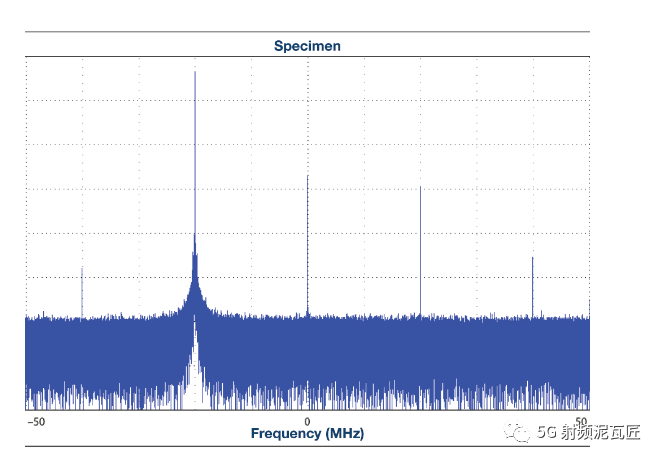

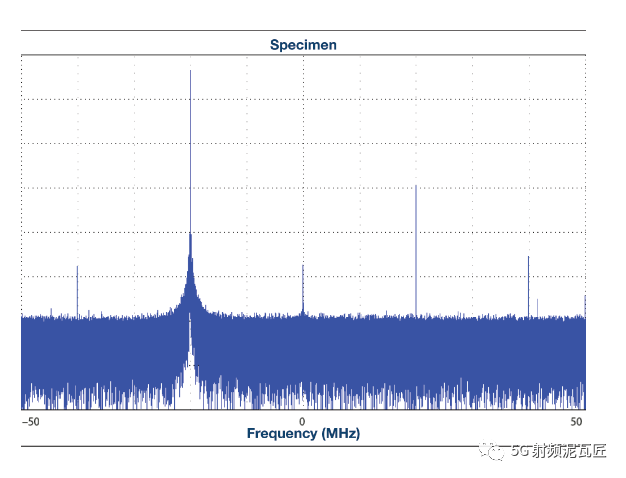

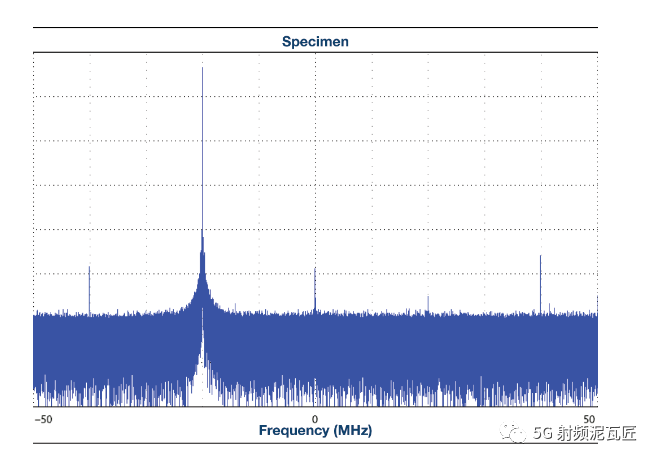

這些誤差在頻譜中表現為鏡像,也是妨礙這些架構廣泛普及的主要原因。然而,作為一種集成式解決方案,通過模擬優化和數字校正技術,可以輕松控制這些鏡像。圖9所示為典型的未經校正的復合數據表示方式。在圖中可以看到LO泄漏(和直流失調)及鏡像抑制(正交誤差)。

圖9.典型的未經校正的LO泄漏和鏡像抑制

LO泄漏控制

LO泄漏在I或Q信號路徑中表現為增大的直流失調。其原因是LO直接耦合至射頻信號路徑中,并被以相干方式下變頻至輸出。結果產生混頻器積,表現為直流失調,加入信號鏈里存在的任何殘余直流失調中。優秀的零中頻架構不但會在初始時自動跟蹤并校正這些誤差,還能隨時間、溫度、電源和流程自動跟蹤和校正,結果可實現優于–90dBFS的性能水平,如圖10所示。

圖10.典型的LO泄漏控制

QEC

為了防止鏡像擾亂性能,一般會采用正交誤差校正(QEC)技術。圖11展示了這種功能可能產生的影響。在此例中,鏡像改善至優于–105dBc的水平,超過了多數無線應用的要求。對于LO泄漏和QEC,運用跟蹤功能是為了確保在性能隨時間而變化時,校正能保持最新狀態,從而保證能始終實現最佳性能。

圖11.LO泄漏控制條件下的典型正交校正

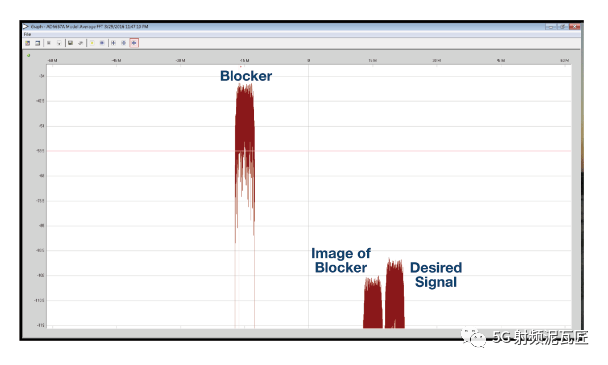

在無線電系統中,正交誤差和LO饋通非常重要。如果誤差足夠大,較大的阻波器鏡像有可能會屏蔽掉較小的目標信號。在圖12中,一個大阻波器的鏡像出現在15MHz處,同時,一個目標信號的中心位于20MHz。如果鏡像部分或全部落在目標信號上,則會導致目標信號SNR下降,結果可能在解調功能里造成誤差。一般地,LTE、W-CDMA等系統都針對這類鏡像設置了合理的容差,但并非完全不受影響。一般情況下,這些系統要求75dBc或更好的鏡像抑制性能,如圖11所示,運用零中頻架構可以輕松達到并維持這一要求。

圖12.鏡像阻礙目標信號的示例

以上我們介紹了零中頻的諸多優勢,接下來介紹零中頻在應用方面的性能如何。

零中頻發射和接收的一個典型示例是?AD9371——

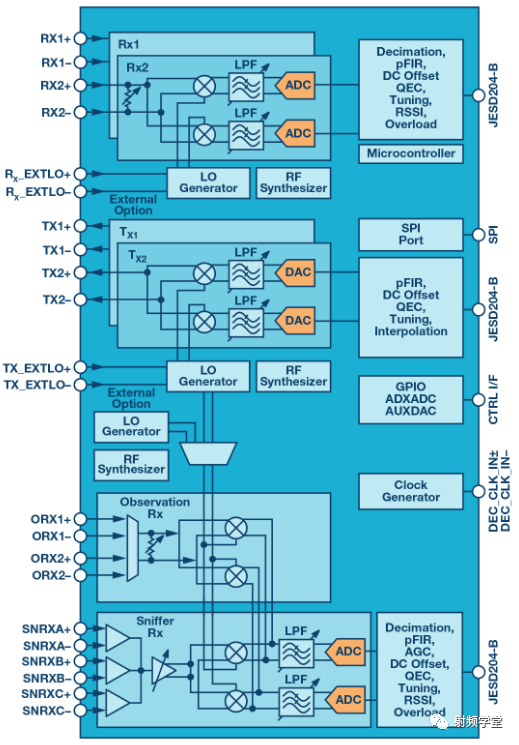

如圖13所示,AD9371具有極高的功能集成度,集成了雙發射、雙接收以及多種額外的功能,包括觀察和嗅探接收器、集成式AGC、直流失調校正(LO泄漏控制)、QEC等。該產品具有較寬的射頻覆蓋范圍,從300MHz至6GHz。每個發射器均可覆蓋20MHz至100MHz的合成帶寬,而每個接收器則能覆蓋5MHz至100MHz的帶寬。雖然此器件瞄準的是3G和4G應用,但也是不超過6GHz的許多其他通用無線電和軟件定義應用的理想解決方案。

圖13.AD9371集成式零中頻收發器

AD9371在12mm×12mm的BGA封裝里集成了完整的系統功能,包括前面討論過的依賴于頻率的所有器件,以及所有校準和對齊功能。在圖4所示接收功能的基礎上,圖14增加了必要的發射功能,造就了一種非常緊湊的雙收發器設計。功耗取決于確切的配置,包括帶寬和實現的功能,但是,AD9371的典型功耗僅為4.86W,包括維持LO泄漏和鏡像抑制的數字功能。

圖14.零中頻收發器的典型布局

AD9371的關鍵性能指標

噪聲系數

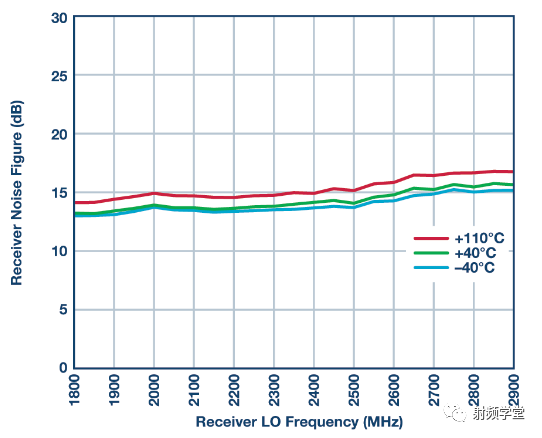

圖15和圖16展示了AD9371的典型噪聲系數特性。第一張圖展示了較寬的射頻頻率,在該頻譜中,噪聲系數相對*坦。該器件的輸入結構采用衰減器的形式,因此,對于每dB,噪聲系數增加1dB。假設最差條件噪聲系數為16dB,衰減為零,外部增益差異允許約4dB的衰減,則可假設總噪聲系數為20dB。對于一個提供至少24dB增益的外部LNA(0.8dB),系統噪聲系數為2dB。

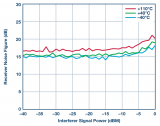

圖15.AD9371噪聲系數(0dB衰減和40MHz帶寬)

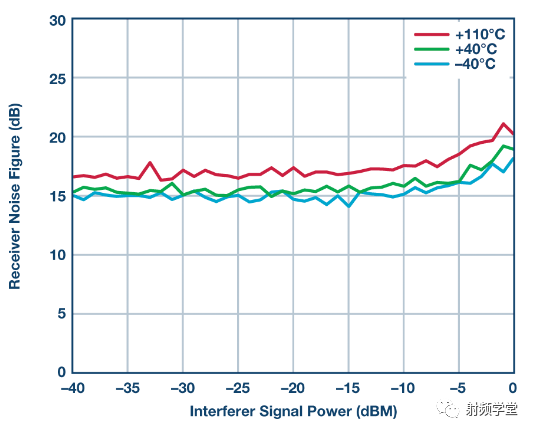

在圖16中,噪聲系數為帶外阻塞相對于AD9371輸入的函數。設外部增益為24dB,在相對于天線連接器–24dBm處,會相對于該器件輸入出現0dBm。如果只考慮AD9371的影響,若集成接收器下降3dB,則噪聲系數的總體下降幅度約為1dB。

圖16.AD9371NF與帶外信號功率的關系

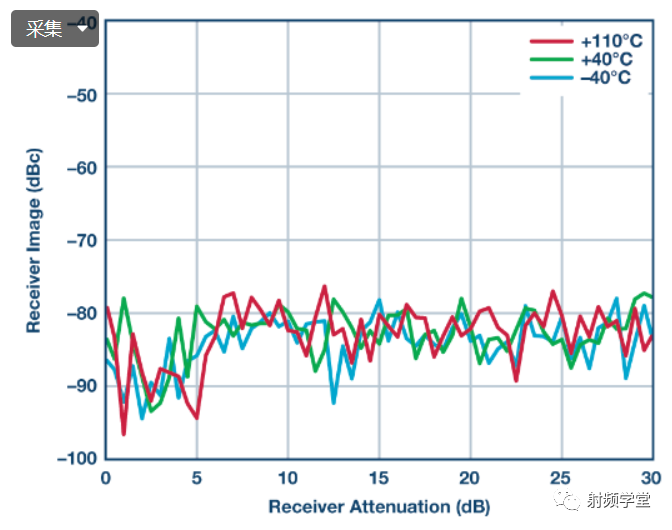

鏡像抑制

與LO泄漏類似,接收鏡像抑制可基于圖17所示信息進行估算。當天線端的典型輸入電*為–40dBm時,則可以估算出,鏡像要優于比天線端口低80dB或–120dBm的水*。

圖17.接收器鏡像抑制

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論