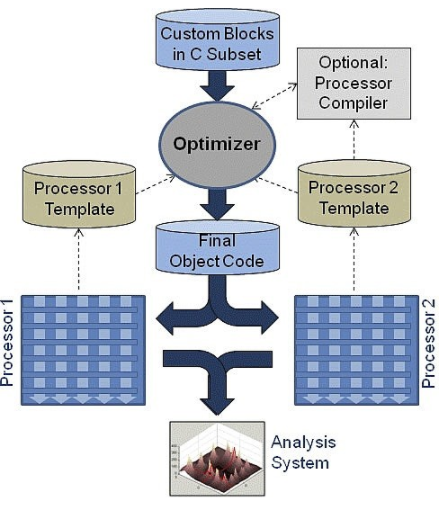

HLS的任務級并行性(Task-level Parallelism)分為兩種:一種是控制驅動型;一種是數據驅動型。對于控制驅動型,用戶要手工添加DATAFLOWpragma,工具會在該pragma指定的區域內判別任務之間的并行性,生成各進程之間的模塊級控制信號。對于數據驅動型,用于需要明確指定可并行執行的任務。

從描述手段來看,控制驅動型本質上是由工具判定各任務能否并行執行。用戶在對各函數描述時只要遵守DATAFLOW的要求即可。例如:讀取輸入數據應該位于DATAFLOW區域的起始位置,寫入輸出數據應位于該區域的終止位置。DATALOW區域內的所有變量遵循“一次讀一次寫”原則。除非使用hls::stream,否則不支持反饋支路。不支持在指定條件下才執行函數。不支持for在指定條件下退出(使用break語句)。但控制驅動型比較靈活,這是因為DATAFLOW的作用對象可以是for循環也可以是函數。

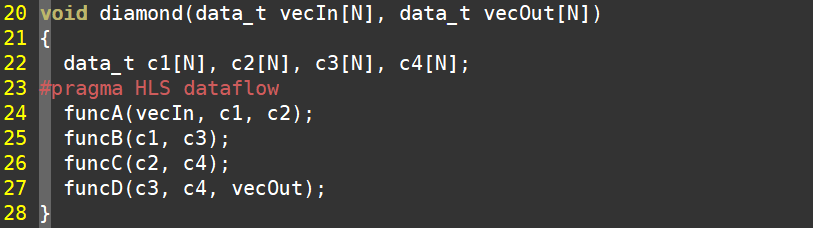

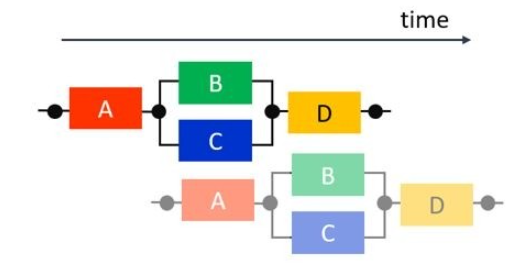

控制驅動器適合于順序執行的C函數。控制驅動型模型帶來的好處包括:當前函數在結束執行之前后續函數可以開始執行;函數在結束執行之前可以重新開始執行;兩個或更多順序函數可以同時開始執行。我們看一個例子。如下圖所示,頂層函數diamond調用了4各函數funcA~funcD。

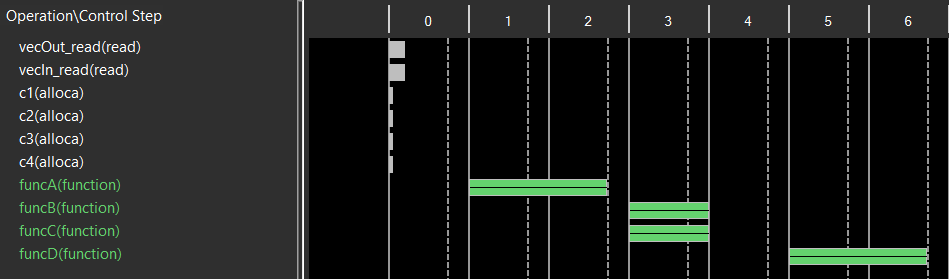

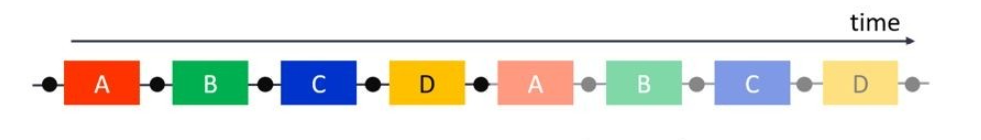

在沒有添加DATAFLOW的情況下,工具能自動探測出funcB和funcC的并行性,這可從Schedule視圖中看到,如下圖所示。

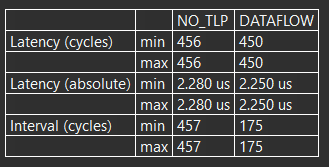

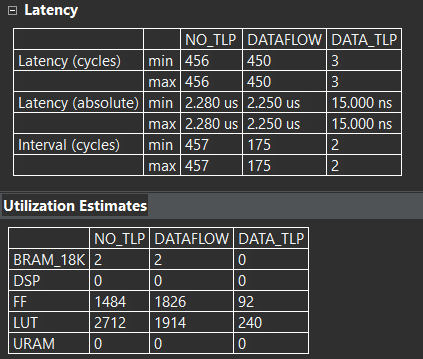

添加DATAFLOW之后,對兩者性能進行對比,如下圖所示(NO_TLP為沒有添加DATAFLOW的solution),從Latency角度看,兩者相當,但從interval角度看,DATAFLOW帶來的效果還是很明顯的。Interval從457降到了175。

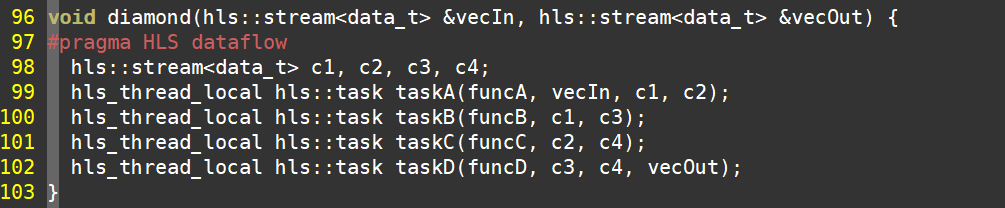

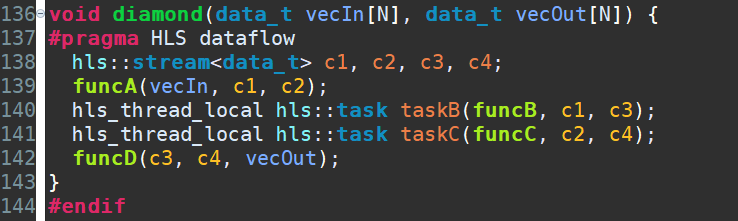

再看數據驅動型。數據驅動型要求任務之前以stream作為接口,允許反饋支路。用戶需要明確通過hls::task指定可并行執行的任務。對于上述函數,我們可以將其改造為數據驅動型,如下圖所示。代碼第98行聲明了4個stream,第99行~第102行通過hls::task指定并行任務。

將三者放在一起對比,如下圖所示。可以看到數據驅動型無論在性能還是資源上都獲得最佳表現。

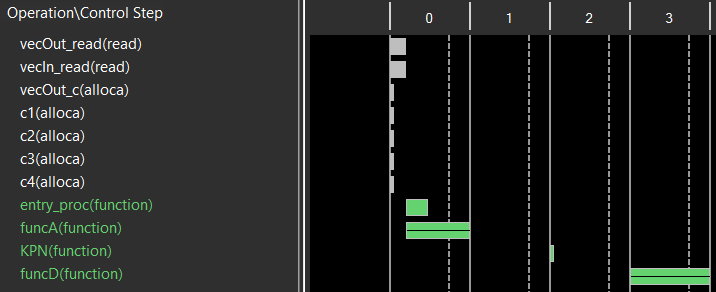

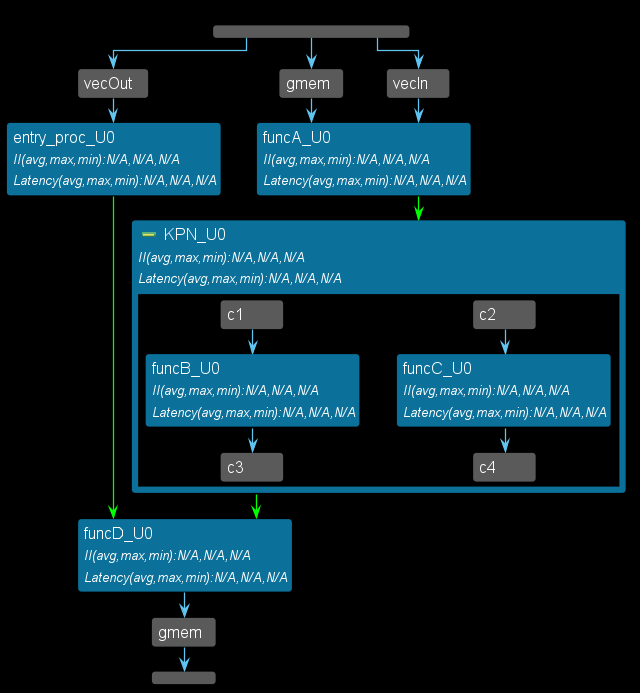

那么兩種類型能否混合使用呢?答案是肯定的,但是有限制的,這源于兩者的自身特征。可以在控制驅動型中嵌入數據驅動型,但反過來是不允許的。我們將上面的例子改造為控制驅動型嵌入數據驅動型的模式,如下圖所示。這里需要注意的是代碼第137行的DATAFLOWpragma,同時代碼第141行和第142行都設置了task,task接口為stream。此外也給出了Vitis HLS的Schedule視圖和Dataflow視圖。Dataflow視圖中也顯示了KPN。

審核編輯:劉清

-

驅動器

+關注

關注

51文章

7988瀏覽量

144979 -

控制驅動器

+關注

關注

0文章

2瀏覽量

5721 -

HLS

+關注

關注

1文章

128瀏覽量

23907

原文標題:再談HLS之任務級并行編程

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Python中的并行性和并發性分析

淺析java異步回調和同步回調

HLS-1Hin人工智能訓練系統

算法隱含并行性的物理模型

矢量化數據并行性的程序方面的作用

有關 Dataflow 指令的原理

如何在不需要特殊庫或類的情況下實現C代碼并行性?

Dataflow | 粗粒度并行優化的任務級流水

HPEC應用子程序線程推測并行性實驗分析

通過利用現代處理器架構的并行性提高SDR的性能

研討會:如何利用最新Vitis HLS提高任務級并行性?

淺析HLS的任務級并行性

淺析HLS的任務級并行性

評論