關鍵詞: C6000 , dsp , MPEG-4 , 編碼器

MPEG-4是一種開放性標準,其中許多部分都沒有規定,可以加入一些新的算法,因此采用通用DSP能夠隨時更新算法、優化算法、使得編碼效率更高。由于MPEG-4編碼算法復雜,需要存儲的數據量大,無論是存儲空間分配、數據傳輸還是運算速度對DSP來說都是挑戰。本文介紹了基于C6000系列DSP的MPEG-4視頻編碼卡的軟硬件實現。利用DSP的VLIW和流水線結構設計程序可以使MPEG-4編碼效率大大提高。

1 DSP特性介紹

由于算法的復雜性及數據量的日益增大,單靠串行結構的處理器完成數據處理工作已經越來越不可行,因此出現了并行結構的CPU以完成這一新的任務。現今最著名的兩種并行體系結構是超長指令字VLIW(Very Long Instruction Word)結構和超標量體系結構。由于超標量體系結構CPU硬件極其復雜,指令動態調度將導致時間的不確定性,所以DSP很少使用這種結構。而一般使用超長指令字(VLIW)結構,這種長指令通常包括多個彼此獨立的同步操作。

C6000系列DSP是TI公司生產的高檔DSP。這一系列DSP都是基于VelociTITM構架的VLIW DSP,它在每個周期可以執行八條32bit的指令,具有高達200MHz的CPU,從而使得其運算能力達到1600MIPS(200MHz×8條指令=1600MIPS)。這些性能都確立了它在高端多媒體應用中的地位。

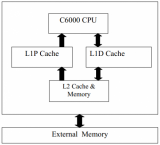

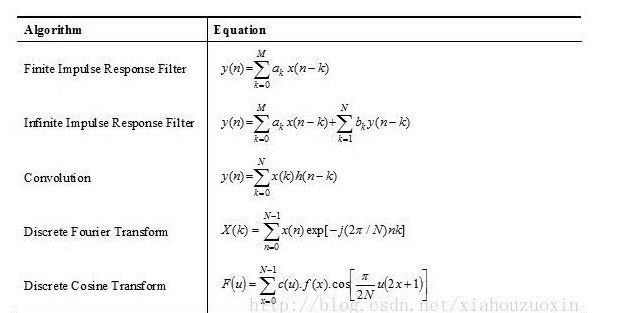

DSP的CPU結構如圖1所示,它具有兩個通道,每個通道具有4個功能單元(1個乘法器和3個算術邏輯單元),16個32位通用寄存器,每個通道的功能單元可以隨意訪問本通道的寄存器。CPU還有兩個交叉單元,通過它們,一個通道的功能單元可以訪問另一個通道的寄存器。另外CPU還具有256bit寬的數據和程序通道,可以使程序存儲器在每個時鐘周期提供8條并行執行指令。這種CPU結構是DSP具有VLIW結構的最基本條件。此系列DSP的存儲空間映射為內部存儲器、內部外設及擴展存儲器。其中內部存儲器由64KB內部程序存儲器和數據存儲器構成,內部程序存儲器可以映射到CPU地址空間或者作為Cache操作。內部和外部數據存儲器均可通過CPU、DMA或HPI(HostPort Interface)方式訪問,HPI接口使上位機可以訪問DSP的存儲空間。

2 MPEG-4編碼卡的硬件設計

MPEG-4編碼卡包括幾部分:視頻采集、視頻的MPEG-4編碼、整個系統的CPLD控制、PC機與DSP的通信等模塊,其結構框圖如圖2所示。

2.1 視頻采集

視頻采集部分主要完成模擬視頻到數字視頻的轉換,包括一片視頻采集芯片和一片小的CPLD。CPLD的作用是控制視頻采集芯片,將采得的數據從8位或16位轉化為32位,并且使數據按照Y、U、V分開的方式排列。這樣相當于對采集到的數據進行了一次預處理,以便于視頻編碼使用。另外,CPLD將32位寬的數據輸出給32位的FIFO。用32位的FIFO以及將視頻數據轉換為32位,可以使DSP讀取視頻數據時32位的數據總線沒有空閑,從而提高DSP讀取視頻數據的效率;這里使用FIFO是為了減少DSP讀取數據的時間、降低高速設備和低速設備的不匹配。每次FIFO半滿時,CPLD會給DSP發送中斷信號,并且在中斷處理程序中使用DMA方式讀取視頻數據;如果不使用FIFO,DSP會頻繁中斷,從而花費大量時間在入棧、出棧以及寄存器的設置上。

2.2 視頻編碼

DSP讀入視頻數據后進行先期處理,如將YUV格式轉為RGB格式等;然后進行MPEG-4視頻編碼。在這一過程中,數據訪問通常要占用50%的時間,算術運算要占用30%的時間,控制要占用20%的時間。因為需要進行運動估計和運動補償,在數據存儲器中通常保存一幀I(原始幀)幀圖像和至少一幀P(預測幀)幀圖像,這些圖像占用的空間都比較大,因此一般都放在外部存儲器SDRAM里。在編碼過程中還要存儲DCT系數、運動向量、量化矩陣、可變長編碼表、Z形編碼表等,由于占用較小的存儲空間而且會反復用到,因此把它們放在片內存儲器中。

2.3 PC與編碼卡通信

PC與編碼卡通信可以通過并口、串口、USB口、PCI接口等方式實現。其中PCI接口方式易于PC與編碼器高速傳輸數據,因此本文采用PCI接口。編碼后的數據通過DSP的HPI、PCI橋芯片、PCI總線到達PC。PC通過DSP的HPI直接對DSP的存儲空間進行訪問。HPI有兩種工作方式:一種是單數據讀寫,這種方式每次只能讀寫一個數據,一般主機對編碼參數進行設置,例如設置圖像大小、幀率等;另一種是burst方式的數據讀寫,在這種方式下只需要指定初始訪問地址,然后以地址自加的方式訪問DSP的存儲空間,這種訪問方式不需要DSP的CPU參與。圖2中CPLD完成PCI橋芯片與DSP之間的訪問控制,DSP、PCI的中斷控制等功能。

3 MPEG-4編碼卡的軟件設計

C6000系列DSP提供的編譯環境支持C++、C以及匯編語言,用C++設計的程序執行效率較低,一般不用;大多數都采用C語言和匯編語言相結合的方式來完成DSP程序設計。DSP程序設計流程如下:先寫出C代碼并對其優化,如果不能達到預期的運行效率,則編寫匯編代碼來提高效率。對于MPEG-4這樣復雜的算法,只運用C語言是遠遠不夠的,在本設計里大部分代碼都由匯編語言完成。

設計高效的代碼,必須充分利用該DSP的VLIW和流水線結構。利用VLIW結構可以在一個時鐘周期并行執行八條32位指令;在流水線結構下,一條指令的執行不用等待上一條指令執行結束,例如DSP從內存中讀取一個數據需要5個時鐘周期,在讀取這個數據的同時,DSP可以去執行別的指令,不必等待這條指令執行結束。具有這兩種結構的DSP在性能提高的同時,程序設計也變得比較復雜。對于具有VLIW和流水線結構的DSP在設計程序時必須注意以下幾個問題:

·每一個指令包可以包括多條操作指令,在C6000系列DSP中每一條指令包括八條32位操作指令;

·可以將兩個16位數據或者四個8位數據合并成一個32位數據,以提高存取效率;

·必須靜態地知道每條操作指令執行需要的時鐘周期,這樣才能取得該操作的正確結果;

·這種結構的處理器不能處理動態事件,例如Cache突然消失;

·對于多周期才能完成的指令,在正確計算的基礎上,一定要提前執行,以免出現一條指令必須等上一條指令執行結束才能執行的情況。

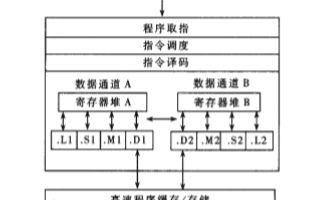

下面結合C6000系列DSP的指令及其具體資源情況,以MPEG-4中的算法為例說明如何利用這兩種結構設計出高效的代碼。

3.1 利用流水線結構設計程序

流水線是指指令的處理可分為幾個子操作,每個子操作由不同的單元完成。對每個單元來說,每隔一個時鐘周期可進入一條新指令,在同一時間內不同單元可以同時處理多條指令。在C6000中B(.unit)lable是一條跳轉指令,它的執行周期為7個時鐘周期,也就是說,在安排這條指令之后6個時鐘周期才能使程序轉移到lable處執行,以程序1為例說明如何利用流水線結構設計程序。該程序的執行順序如下:0000→0004→0008→000C-0010→0014→0008→000C...從程序執行順序知道,要想在執行完0014處的指令后跳轉到LOOP處,就應該在0014的前6個時鐘周期處安排這條指令;如果不提前安排好這條指令,而是在0014后放置這條指令,就需要使CPU等待6個時鐘周期才能跳到LOOP處,從而使程序運行效率降低。從這個程序的執行順序可以看出,必須提前知道每一條指令的運行周期數,并提前安排該指令,才能達到減少等待周期、提高程序效率的效果。C6000系列DSP指令集包括許多多時鐘周期的指令,如跳轉指令、數據訪問指令等。MPEG-4編碼算法需要頻繁地訪問大量數據,并且有很多循環,無論是數據訪問還是循環都要用到多時鐘周期指令。以MEPG-4的DCT算法為例,每一個8×8的塊變換需要用16次的跳轉指令和256次數據訪問指令,由此可見流水線在MPEG-4程序優化中所起的作用。

3.2 利用VLIW結構設計程序

利用VLIW結構設計程序可以充分利用DSP多個功能單元并行工作的特性。DSP的每一個通道都有四個功能單元(L、S、M、D),每個功能單元負責完成一定的邏輯或者算術運算,另外A、B兩個通道的互訪可以通過交叉單元1x、2x完成。程序2中,在一個時鐘周期內并行執行八條指令,使用了所有的功能單元S2、S1、L1、M2、L2、M1、D1、D2,同時使用了所有的交叉單元1x、2x,已經達到極限。但是這種并行指令的使用也有一定的限制,其最根本的要求就是不能引起資源沖突,例如:

·不能用同一個功能單元;

·不能對同一通道的寄存器進行兩次long型寫操作;

·不能對同一通道的寄存器同時進行long型讀操作和存儲操作;

·讀同一寄存器不能超過4次;

·在同一個時鐘周期不能有兩個指令寫入同一寄存器,這不是說向同一寄存器寫的兩條指令不能放在同一個并行指令包內,而是說兩個指令不能在寫寄存器的那個時鐘周期并存。

仍然以MPEG-4中的DCT算法為例說明VLIW結構在程序優化中的作用。進行DCT變換的原始數據是short型的,因此可以將兩個數據合成一個32位的數據來訪問;為了使兩個通道并行訪問數據和運算,應盡量把要訪問的數據平均地分配給不同的通道寄存器;并且通過交叉單元使兩個通道相互訪問,從而達到很高的并行性,大大提高了編碼效率。

MPEG-4編碼的其它算法,例如逆DCT、運動估計、運動補償等算法都包含著大量的循環運算和數據訪問。因此利用DSP的VLIW結構和流水線結構優化MPEG-4編碼算法就成為一種非常合適的方法。

當然,編寫程序時不是將DSP的VLIW結構和流水線結構分開考慮,而是將兩者結合起來,在編寫每一條指令時都要清楚這條指令的執行周期以及使用的功能單元,這樣才能編寫出高效的程序。

表1對1-D Chen 8×8 DCT、100點點積和FIR濾波器算法的C語言實現與利用VLIW及流水線結構的匯編代碼實現進行比較。從統計數據可以看出,利用DSP結構編寫的匯編代碼執行效率要比C語言編寫的代碼執行效率高40倍左右。因此充分利用DSP的VLIW結構和流水線結構設計匯編程序能夠使效率大幅度提高。

本文對MPEG-4編碼卡進行了設計,主要難點是MPEG-4編碼算法的優化,MPEG-4的編碼復雜、代碼量大。利用C6000系列DSP的VLIW結構和流水線結構設計出了MPEG-4編碼算法。實驗證明,算法效率得到了大幅度提高。

電子發燒友App

電子發燒友App

評論