關鍵詞: 處理板卡 , 視頻采集 , 硬件設計

1 引言

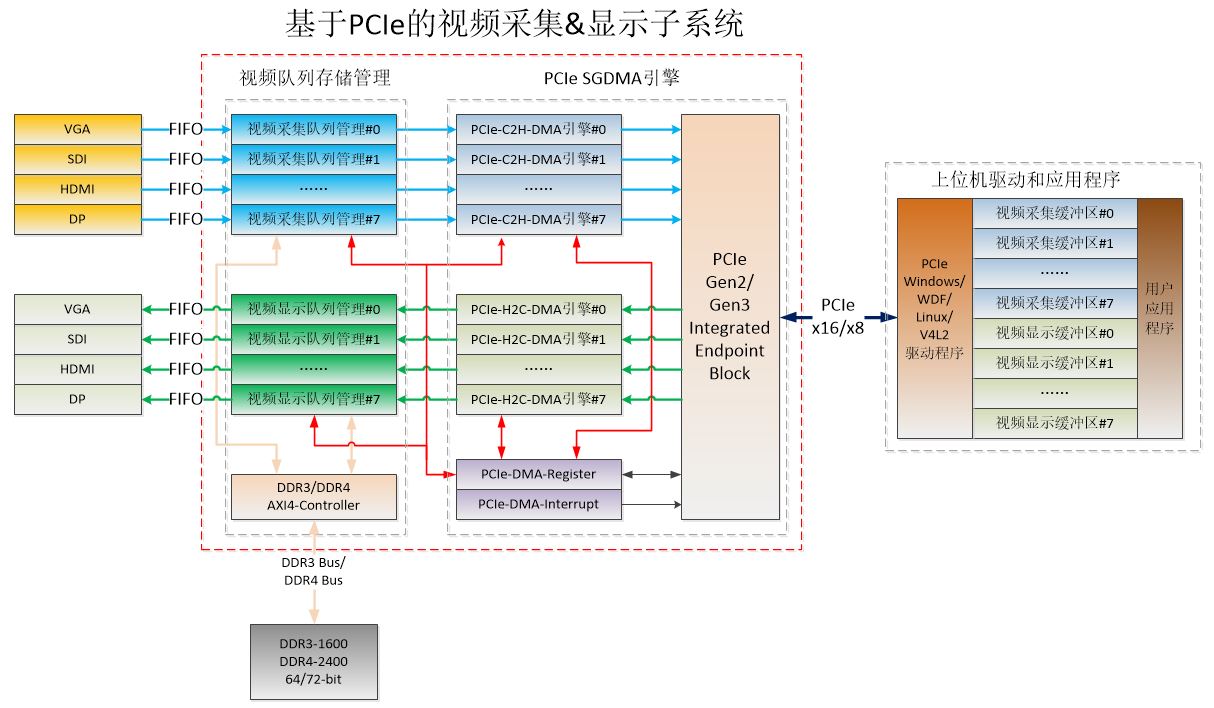

視頻監控系統是安全防范系統的重要組成部分,也是一種防范能力較強的綜合系統。視頻監控系統以其直觀、方便、信息內容豐富而廣泛應用于許多領域。近年來,隨著計算機、網絡及圖像處理、傳輸技術的飛速發展,視頻監控技術也得到長足的進步,集多媒體技術、數字圖像處理和遠程網絡傳輸等最新技術為一體的多媒體數字監控系統正在逐步取代傳統的模擬視頻監控系統。目前,市場上專用的視頻壓縮電路只能實現一種壓縮算法,靈活性和可擴展性較差,基本不具備在此基礎上進行二次開發的能力;各種基于ISA、PCI等總線的圖形采集卡也能在市場上買到,但價格較貴,且處理功能簡單,二次開發效率低,不能很好地滿足用戶的特殊需要。

為了適應多媒體通信技術的發展,美國德州儀器公司推出一款針對視頻和圖像解決方案的TMS320DM642型高性能數字媒體處理器,它是TI公司 C6000系列DSP中最新的定點DSP,其核心是C6416型高性能數字信號處理器,具有極強的處理性能、高度的靈活性和可編程性,同時外圍集成了非常完整的音頻、視頻和網絡通信等設備及接口,特別適用于機器視覺、醫學成像、網絡視頻監控、數字廣播以及基于數字視頻/圖像處理的消費類電子產品等高速 DSP應用領域。筆者針對市場客戶的需求,設計并實現了一款以TVP5150為視頻輸入解碼器、以PCMl801為音頻輸入采集電路、以 TMS320DM642型DSP為核心處理器的多路視頻采集兼壓縮處理PCI板卡,并將其應用于構建高穩定性、高魯棒性的多媒體數字監控系統,取得了較好的社會效益和經濟效益。

2 TMS320DM642的硬件架構

TMS320DM642采用第二代高性能、先進的超長指令字 velociTI.2結構的DSP核及增強的并行機制,在720 MHz的時鐘頻率下,其處理性能為5 760Ml/s,使得該款DSP成為數字媒體解決方案的首選產品。它不僅擁有高速控制器的操作靈活性,而且具有陣列處理器的數字處理能力。 TMS320DM642的外圍集成了非常完整的音頻、視頻和網絡通信接口,主要包括:

3個可配置的視頻端口(VPORTO-2),能夠與通用的視頻編、解碼器實現無縫連接,支持多種視頻分辨率及視頻標準,支持RAW視頻輸入/輸出、傳輸流模式;

1個10/100Mb/s以太網接口(EMAC),符合IEEE 802.3標準;

1個多通道帶緩沖音頻串行端口(McASP),支持I2S、DIT、S/PDIF、IEC60958-1、AES-3、CP-430等音頻格式;

個多通道帶緩沖串行端口(McBSP),采用RS232電平驅動;

1個VCXO內插控制單元(VIC),支持音/視頻同步;

1個32位、66MHz、3.3 V主/從PCI接口,遵循PCI2.2規范;

1個用戶可配置的16/32位主機接口(HPI);

1個16位通用輸入/輸出端口(GPIO);

1個64位外部存儲器接口(EMIF),能夠與大多數異步存儲器(SRAM、EPROM)及同步存儲器(SDRAM、SBSRAM、ZBT SRAM、FIFO)無縫連接,最大可尋址外部存儲器空間為1 024MB;

1個具有64路獨立通道的增強型直接內存訪問控制器(EDMA);

1個數據管理輸入/輸出模塊(MDIO);

1個I2C總線模塊;

3個32位通用定時器;

1個符合IEEE 1149.1標準的JTAG接口及子板接口等。

有關TMS320DM642的詳細性能介紹請參照其數據手冊。

3 多路視頻采集處理板卡硬件設計

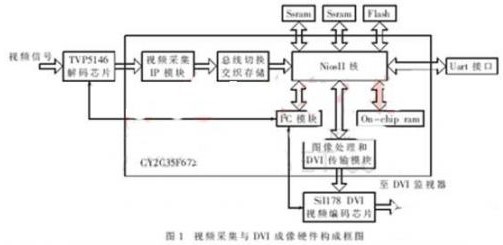

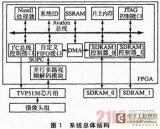

基于TMS320DM642的多路視頻采集處理板卡的主要硬件功能模塊包括視頻輸入解碼模塊、音頻輸入采集模塊、核心DM642型DSP模塊、外部存儲模塊、PCI總線驅動控制模塊及電源管理模塊等。基本工作原理是由CCD攝像頭采集輸入的模擬視頻信號,經過視頻解碼器轉換成數字視頻信號,由拾音器采集輸入的模擬音頻信號經過音頻采集電路轉換成數字音頻數據,送到DM642, DM642再將采集的音、視頻數據用MPEG-4標準編碼壓縮后通過PCI接口傳送到PC上位機,構成數字監控系統。本板卡的總體設計功能框圖及接口信號示意圖如圖1所示,主要由1個TMS320DM642GDK(DSP)、4個TI公司的TVP5150AMl(視頻解碼器)、2個TI公司的 PCMl801U(音頻采集電路)、2個Hynix公司的HY57V283220TP-6(SDRAM)、1個SN74CBTl6233DGGR(PCI 總線橋接電路)以及AMSl085CM和AMSl086CD(電源管理電路)等組成。

3.1 視頻輸入解碼模塊

視頻輸入解碼模塊由4個TVP5150型視頻解碼器及外圍電路組成,主要功能是將每一路CCD攝像頭采集輸入的標準PAL制電視模擬信號發送到視頻解碼器,完成視頻圖像的箝位及抗混疊濾波等預處理、模擬數字化轉換及亮度/色度、水平/垂直同步等信號的分離,實現模擬視頻信號轉換為數字并行信號 BT.656碼流格式。TVPSl50可將基帶模擬NTSC、PAL及SECAM視頻信號轉換成數字分量視頻信號,正常工作時的功耗僅為115 mW,售價比同系列TI產品更低,并且具有業界最小尺寸的32引腳超薄方型扁平封裝(TQFP)。TVPSl50支持2個復合端子或1個S端子輸入,可輸出ITU-RBT.656,并支持Macrovision復制保護及高級VBI功能。

DM642視頻口0、1中的一部分(VPO/A、VPI/A)及視頻口2(VP2/A、VP2/B)分別掛接1個TVP5150,視頻采集的數據格式為 YUV4:2:2,分辨率為CIF(352x288)大小。視頻輸入解碼模塊接口電路原理功能框圖如圖2所示。系統將2個電路的I2C總線接口SCL和 SDA分別互連,TVP5150的視頻輸出口YOUT[0-7]和DM642 VPORT口的VPOD[9-2]相連,TVPSl50的系統時鐘SCLK和DM642VPORT口的VPOCLK0相連。由于采用ITU-R BT.656碼流格式,圖像的水平同步、垂直同步、場同步等同步信號已內嵌在視頻數據流中,并且考慮到DM642每個VPORT口預留的3個用以接收同步信號的VPOCTL[0-2]控制引腳,只能滿足一路視頻同步信號的要求,所以在設計過程中省略同步信號線的連接。

TVP5l50雖然不支持縮放(Scaling)功能,但是可以截取屏幕的一部分再傳輸給DM642作后續的壓縮處理。具體操作是在對應的寄存器中選擇視頻流的起始行和結束行,控制圖像的縱向長度,選擇單行的起始位置和結束位置并利用圖像的AVID功能控制圖像的水平寬度。

DM642對TVP5l50內部寄存器的訪問通過I2C總線實現,在與TVP5l50應答過程中需要從器件TVP5150的地址0x101lIOXl,其中X代表0或者1,并可以在系統上電時配置。TVP5150在上電時會根據YOUT[7]上的電位高低決定X代表O,還是1。這樣,TVP5l50作為從器件的地址只有2個:Oxl0111001和0x10111011。DM642要與4個TVP5I50通信,一路I2C總線是不夠的,需要通過GPIO接口利用軟件模擬I2C總線時序,配置另外兩個TVP5150。

采集輸出的數字視頻數據送入DM642VPORT端口的5 120 Bytes大小的緩沖區。TVP5150在本地時鐘的控制下通過EDMA通道自動向DM642 VPORT端口緩沖區單元發送數據,當采集完一場數據時產生DMA中斷,并在DMA中斷服務程序中根據實際需要完成相應的視頻處理,經過實時編碼壓縮后的視頻數據存儲到外部SDRAM中。硬件電路需要提供TVP5150所需要的14.31818 MHz時鐘頻率,DM642可通過I2C總線對TVP5150的參數進行設置。

3.2 音頻輸入采集模塊

音頻輸入采集模塊由2個PCMl801U型音頻采集電路及其外圍電路組成,主要功能是對由拾音器采集輸入的模擬音頻信號進行采樣,然后將其轉換為DSP可以處理的數字音頻數據格式。PCMl801U是采用5V工作電壓的雙聲道16位音頻模/數(A/D)轉換器,包括1個單端-差分模擬前端、1個5階△一∑ 調制器(64倍重復取樣)、1個內部高通數字均分濾波器。

DM642視頻口0、l中的剩余部分(VPO/B、VPl/B)配置為McASP,與1個PCMl801U連接,實現音頻的輸入采集功能。用 PCMl801U的左、右2個16位音頻聲道獲取4路音頻通道的數字化數據,音頻采集的數據格式為每路單聲道、44.1 kHz采樣率,每個采樣數據用8位量化。采集輸出的數字音頻數據通過McASP傳給DSP的輸入緩沖區單元,當設定用于存放音頻采樣數據的緩存器滿時產生 DMA中斷,并在DMA中斷服務程序中根據實際設定情況處理音頻數據,經過實時編碼壓縮后的音頻數據存儲到外部SDRAM中。DSP通過I2C總線實現對音頻采集電路的編程,以控制采樣速率、音頻源、音量等具體參數。硬件電路需要提供音頻采集電路需要的工作時鐘,筆者使用的時鐘是11.2896 MHz。音頻輸入采集模塊接口電路原理功能框圖如圖3所示。

3.3 核心DM642 DSP模塊

核心DM642 DSP模塊由1個TMS320DM642型數字媒體處理器及其外圍電路組成,主要對采集到內部輸入緩存的數字音、視頻數據流進行處理及壓縮。視頻圖像信號的壓縮一般屬于有損壓縮,同時系統又必須滿足編碼的實時性,所以采用定點DSP可較好地滿足整個壓縮系統對精度和速度的要求。該板卡設計采用的DM642 是專門為圖像視頻領域的應用而設計的,有完備的片外接口,能夠比較方便地擴展片外存儲器等外設。

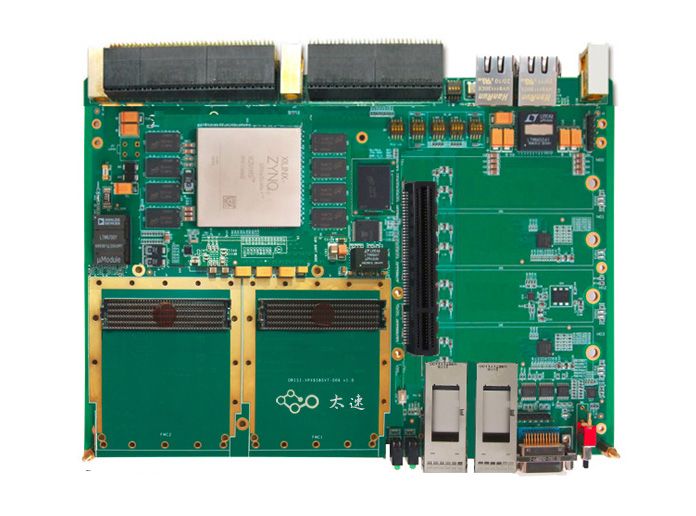

C64xx系列DSP有大量的字節可設定的地址空間,程序代碼和數據可被存儲在統一標準的32位地址空間的任何位置。表l所示的內存映射顯示了本板卡采用的DM642處理器的地址空間。在默認狀態下,內部的寄存器從0x00000000地址空間開始存儲。一部分存儲器由軟件重新映射為L2高速緩存。DM642的EMIF有4個獨立的可設定地址的區域,稱為電路使能空間(CEO-3)。本板卡合并形成了64位長的外部存儲器端口,將地址空間分割成4個電路使能區,允許對地址空間進行8位、16位、 32位和64位的同步或不同步的存取。目前,板卡使用電路使能區CEO,并將其分配給64位的SDRAM總線。CEl-3的電路使能區暫不使用,可以作為今后的擴展,以便分配給8位Flash、UART、FPGA和子板接口等使用。

本板卡在CE0空間連接了64位的SDRAM總線,與2個HY57V283220TP-6相連以構成SDRAM。每個HY57V283220TP-6均為 32位數據總線的SDRAM,其中,高32位存儲在1個SDRAM中,低32位存儲在另1個SDRAM中,從而滿足DM642 64位數據總線的要求。32 MB的SDRAM空間用來存儲程序、數據和視頻信息。總線由外部PLL驅動設備控制,運行在133 MHz的最佳狀態。SDRAM的刷新由DM642自動控制。

DM642可配置EMIF時鐘的原始值。本板卡的ECLKIN引腳選用默認值,也可通過分頻CPU時鐘控制EMIF的時鐘頻率。在初始化時通過對E- CLKINSEL0和ECLKINSEL1引腳的操作進行設置,它們與EAl9引腳和EA20引腳共同分享EMIF的地址空間。

3.4 PCI總線驅動控制模塊

PCI總線驅動控制模塊由1個SN74CBTl6233型PCI總線橋接電路及其外圍電路組成。本模塊中的信號按照功能可以分為系統信號、地址數據復用信號和接口控制信號等。系統信號包括CLK和RST,為系統提供時鐘和復位。對地址數據復用信號來說,在總線傳輸操作周期中,1個PCI總線周期由1個地址段和緊隨其后的1個或多個數據段組成,其中AD[0-31]是地址數據復用總線,可為PCI接口電路提供地址和數據信號;復用引腳PCBE[0-3]為 PCI接口電路提供總線命令信號和字節允許信號。接口控制信號主要由FRAME、TRDY、IRDY和DE-VSEL等信號組成,其中,FRAME信號是總線周期構成信號,由當前總線中主設備驅動,表明1個總線周期的開始和延續;TRDY是目標設備就緒信號,在寫操作中,TRDY有效表明從設備已準備好接收數據,而在讀操作中,TRDY有效則表明AD[0-31]上已有有效數據;IRDY表明驅動設備已準備好數據;DEVSEL為設備選擇信號,當其有效時,說明驅動它的主設備已將其地址譯碼作為當前操作的目標設備,該信號作為輸入信號時,DEVSEL用來表示總線上已有目標設備被選中。其他PCI總線所需但本系統不用的信號則可用高阻態代替。PCI總線驅動控制模塊接口電路原理功能框圖如圖4所示。

本板卡使用DM642型DSP片內集成的1個主/從模式的PCI接口與PCI總線相連,該接口支持PCI 2.2規范,通過PCI總線能夠實現DSP與PCI主機的互連。主機可以通過DM642的PCI接口訪問整個片內RAM及外部存儲器。DSP的EMIF通過EDMA將數據傳輸到DSP的內存中,EMIF支持同步FIFO,為了能夠使PCI總線實時讀出視頻壓縮數據流,并及時地傳送給主機,本系統采用了中斷機制。當FIFO滿時,DSP產生一個中斷信號,通知PCI接口模塊啟動DMA,需傳輸的數據經FIFO由DSP利用DMA傳輸方式在計算機和板卡間實現視頻壓縮碼流的高速傳輸,在提供高速傳輸接口的同時不影響其他DMA操作。

3.5 電源管理模塊

本板卡通過PCI插槽供電,選用AMSl085和AMSl086提供板卡正常工作時的穩壓電源。AMSl085、AMSl086均為3端可調節穩壓集成電路,AMSl085輸出電流為3 A、輸出電壓為1.5 V/3.3 V.5.O V,AMSl086的輸出電流為1.5 A、輸出電壓為1.5 V/1.8V/3.3 V/5.0 V。它們比較容易使用,而且都有短路電流保護以及過熱保護等防護措施,具有高精度的輸出電壓及工作穩定性。設計時,內部+5 V輸入電源被整流為+1.4 V、+1.8 V和+3.3V,其中,+1.4 V電壓提供給DSP處理器,+1.8 V電壓提供給TVP5150,+3.3 V電壓提供給DSP內的I/O和板卡上其他電路。3.3 V和1.4 V電源之間應連接肖特基二極管,保證給DM642內核和外部端口同時供電。

4 板卡設計的難點及關鍵技術

本設計方案中.處理器的主頻高達720 MHz,SDRAM的最高頻率為133 MHz,這對信號完整性及電磁兼容性都是極大的挑戰。在多路視頻采集處理板卡的PCB設計中突出體現以下難點:

一是時序問題,工作頻率的提高和信號上升/下降時間的縮短,首先會使設計系統的時序余量縮小甚至出現時序方面的問題。

二是傳輸線效應導致的信號振蕩、過沖和下沖都會對設計系統的故障容限、噪聲容限及單調性造成很大的威脅。

三是信號沿的時間下降到l ns后,信號之間的串擾成為很重要的問題。

四是當信號沿的時間接近0.5 ns時,電源系統的穩定性和電磁干擾(EMI)也十分關鍵。

多路視頻采集處理板卡PCB的設計策略如下所述:

(1)高速數字電路設計

為了更快地推出更高性能的產品,電路板設計按6層板考慮,在元器件布局及布線過程中嚴格遵守高速電路設計原則,為確保系統功能的實現及整機性能指標達到檢測標準,在PCB布線時需要特別注意串接電阻降低高速電信號反射的影響及保證同一組數據同步到達。由于信號在頂層、底層與中間層的傳輸阻抗和傳輸速率不一樣,因此應盡量將接到同一器件的信號線分布在同一層上,并使導線長度相等。

(2)電源設計

電源是系統正常工作的基礎,一般來說,只要電源工作正常,都可以通過JTAG口將程序下載到DM642中,進而調試其他的模塊。在設計中,應使用足夠多的電源層和地層,對AVDD、DVDD、AGND、DGND分層設計,并將模擬地與數字地單點接地,這樣可以避免模擬電路與數字電路相互影響。

5 結束語

筆者在引進和消化TMS320DM642的多媒體數字處理技術的基礎之上,成功研發了這款多路視頻采集處理板卡。本板卡結構緊湊、功能完善、性能可靠、音/視頻效果優異、系統升級方便。目前,業內的主流還是基于CIF分辨率的監控記錄,今后高分辨率(D1) 的監控記錄以及采用H.264技術的編碼壓縮產品的市場需求將逐漸增加,給算法優化及處理器能力的提升提出了新的課題,這將是下一步關注的重點。

電子發燒友App

電子發燒友App

評論