關鍵詞: LED , 大屏幕 , 嵌入式 , 顯示屏

1 引 言

LED顯示屏的應用已經比較普遍,而且隨著應用的普及,更多新式的LED顯示屏會應用在更多的場合,所以研究嵌入式大屏幕點陣LED的顯示很有實際意義。

但是現在市場上的多種LED顯示屏在顯示性能上良莠不齊,并且大多需要上位機對顯示過程進行實時控制。本文提出一種優化的高性能高可靠性的嵌入式大屏幕LED顯示系統,只需要用1片FPGA和2片SRAM就可以實現大屏幕LED顯示的驅動和內容更換,可以說其性能已經大有改善。本設計可以應對多種大屏幕顯示的場合。

2 系統硬件設計與實現

硬件連接的方式多種并且靈活,其連接方式直接影響到顯示的性能。下面給出的硬件連接方式是最優的方式,能夠達到高性能的顯示,并且使軟件編寫變得簡單。

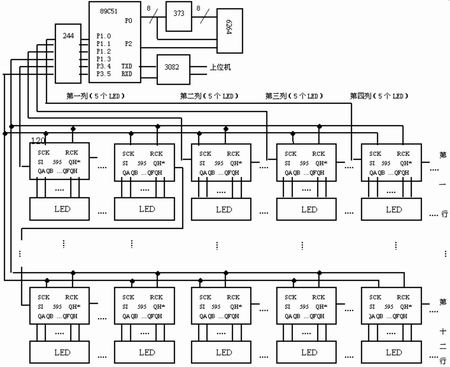

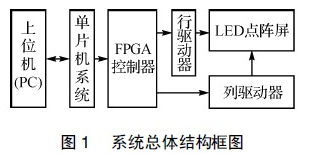

每個8×8的LED點陣塊稱為最小模塊。每16個8×8的LED點陣塊為一個基模塊,一個基模塊橫向有8個,縱向有2個最小模塊,如圖1所示。圖中每個小方格代表一個最小模塊。

每個最小模塊控制信號為8個行信號H1~H8和8個數據信號R1~R8。行信號接一個38譯碼器74HC138的輸出,他的輸入為HangQ[2..0];而列信號給具體這一行的數據信號接的是一個74HC595的輸出,如圖2所示。

74HC595是移位鎖存芯片,他內部有一個移位寄存器,還有一個數據移入引腳(DS)、一個數據移出引腳(Q8)、8個數據輸出引腳(Q1~Q8),另外還有脈沖信號(CLK)和數據鎖存信號(ST)。他的工作原理是當脈沖信號作用時將移入引腳的數據移入芯片內部的移位寄存器,當移滿8位數據以后,第8位的數據就會出現在數據移出引腳上,再給一個脈沖信號,這一位數據就會被移出同時也有新的數據移入。當數據鎖存信號有效時,芯片內部的的移位寄存器就將8位數據就鎖存到8個數據輸出引腳上,從而實現數據輸出。

對于一個最小模塊,當數據信號R有效后,時鐘信號TSCK就將該數據移入74HC595的內部寄存器,內部寄存器的8位全部移滿數據后,鎖存信號TLOCK有效,就能將移滿的數據全部送到8個數據信號R1~R8上。這個時候,再用HangQ[2..0]選中其中的某一行信號,行鎖存信號TLEDEN有效后,就可以在這個8×8的點陣列上實現數據顯示。因為在一個特定的時間只能在這個8×8的LED點陣塊上顯示其中的一行,所以將第一行到第8行依次循環顯示,只要速度足夠快,人眼看起來就是連續的。

對于一個基模塊,因為每個最小模塊都有一個74HC595移位鎖存芯片,只要將各個最小模塊的74HC595串聯起來,也就是將前一個74HC595的數據移出引腳接到下一個74HC595的數據移入引腳上,而74HC595的脈沖信號和數據鎖存信號都接同一個信號,就可以實現一個基模塊的數據顯示。與最小模塊一樣,在一個特定的時間只能顯示基模塊中的所有最小模塊的某一行。只要在8行依次顯示的過程中速度足夠快,人眼就看不出閃爍。

這樣就實現了上面16個基模塊連在一起。數據及控制信號從右邊進入,從左邊輸出。一個基模塊為64×16的LED點陣塊,本設計中的顯示規模為512×512點陣,所以要將橫向有8個,豎向有32個最小模塊連接起來。而在實際的設計中分為上半屏和下半屏顯示,分別為512×256。當數據裝滿上半屏后再裝下半屏,數據鎖存信號和行鎖存信號最后給出,從而實現整屏的最小模塊的某一行顯示。當然要實現整屏數據的顯示,只有循環顯示整屏中最小模塊的8行。

在上半屏顯示中,又將其分為8個512×32的塊,這樣的塊叫單獨顯示模塊,也就是說將橫向的2行基模塊看成一個單獨的模塊并用單獨的一組信號進行控制,上半屏就要8組信號控制。這8組信號除了數據信號R不同外,其他的信號都是一樣的。也就是說,在上半屏顯示中8條數據線同時給上半屏的8個單獨顯示模塊串打數據,當然只是給單獨顯示模塊中的最小模塊的某一行打滿數據,然后再給下半屏打入數據。所以下半屏的情況與上半屏基本一樣,除了8組數據信號R不同外,還有時鐘信號也不一樣。輸入數據時,上半屏的時鐘信號首先有效,根據基模塊的理論要輸入2048個脈沖以后上半屏的數據才被灌滿;然后下半屏的數據才有效,從而輸入下半屏的數據,情況與上半屏完全一樣。

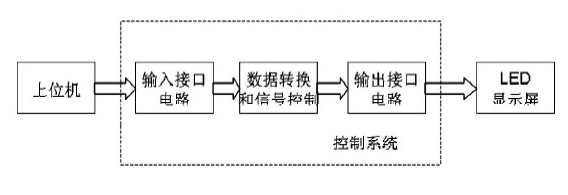

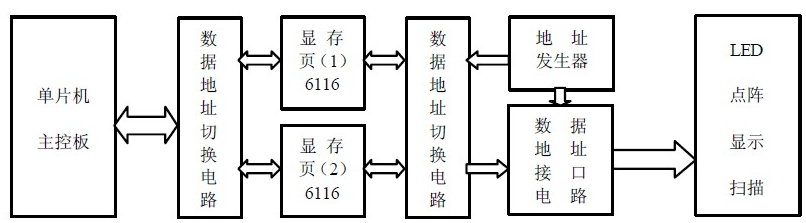

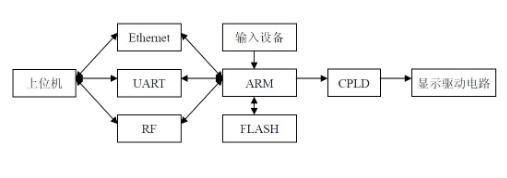

在顯示控制方面,使用一塊ALTERA公司的FPGA芯片,型號為EPF10K20TC1444,另外還使用了2塊SRAM芯片,每塊的容量為128kB,他們都用來存放顯示的數據(見圖3)。

工作時,FPGA在一個特定的時間只從2塊SRAM的其中一塊取出顯示的數據進行顯示,而同時另外一塊SRAM與MPU進行數據交換,MPU會寫入新的數據,以便FPGA在下一個時間段顯示這塊SRAM的數據,以此交替的工作。如果顯示的圖像不改變,即一塊SRAM里的數據不變時,MPU就不需要給另一塊SRAM寫數據,這時該嵌入式顯示模塊就可以獨立于MPU工作。一幀的數據大小為32kB,遠小于SRAM的容量,所以可以在編寫程序的時候加入一些顯示的技巧,比如從上往下顯示等。

由以上所知,FPGA有2個基本作用,一個是從一塊SRAM中取出數據并顯示在顯示屏上;另外一個是將MPU給的數據寫到另一塊SRAM中。

3 軟件設計

軟件設計要根據硬件的連接情況編寫,主要分為顯示部分和寫RAM部分(見圖4)。

在掃描顯示中,首先上半屏的8組控制信號的時鐘脈沖信號有效,并且在這個過程中,8組控制信號的數據信號R有效,所以就可以先將上半屏的8個單獨顯示模塊中的最小模塊的某一行灌滿數據。然后用同樣的方法將下半屏的8個單獨顯示模塊中的最小模塊的某一行灌滿數據,當然上半屏和下半屏灌滿的都是最小模塊的相同的一行。最后數據鎖存信號和行鎖存信號有效,使其顯示。在這個過程中要注意的是數據信號R,因為要顯示整屏的數據,在軟件編寫的過程中要將某個位置顯示的數據準確的顯示在該位置,就要從內存中準確的取出這個數據。

每一幀顯示的數據大小為32768B,對于2塊RAM交替工作的情況是完全符合要求的。并且SRAM的存取速度快,換幀的時候也能夠很好地顯示出預期的數據。程序中用一個RAM選擇模塊,用來選擇某個時間是讀出哪一塊RAM,還是寫入哪一塊RAM。

FPGA與存儲器聯接的信號為am1A[16..0], Ram1D[7..0], Ram1Rd, Ram1 Wr; Ram2A[16..0], Ram2D[7..0], Ram2Rd, Ram2Wr。當FPGA從Ram1取出數據進行顯示時,其中有關Ram1的信號就有效;同時就給Ram2寫數據。程序中還用到4個內部變量Rt[7..0][7..0],Gt[7..0][7..0],Rs[7..0][7..0]和Gs[7..0][7..0]分別代表4個數組,每個數組里有8個字節。

程序中用到1個全局時鐘clk,他用來驅動1個內部全局信號counter_temp,他是1個15位的矢量。TSCK和TNsck信號將8個clk時鐘周期作為他們的1個時鐘周期,也就是說8個clk時間送出1位數據。FPGA讀RAM的時序為:首先地址信號出現在RamxA[16..0]上,然后RamxRd,RamxWr分別置為低電平和高電平,經過12~15ns,讀出的數據就會出現在RamxD[7..0]上以便FPGA讀這個數來顯示。

FPGA寫Ram的時序是外部MPU信號控制,首先地址信號出現在Ram2A[16..0]上,然后RamRd, RamWr分別置為高電平和低電平,寫的數據出現在Ram2D[7..0]上。經過很短的時間,數據就寫入了。

程序設定FPGA中的Ram1D和Ram2D為雙向口,可寫可讀。在內部要設相應的緩沖器。因為寫RAM是MPU寫給RAM,MPU要指明寫的地址和數據,所以在程序中要有地址和數據輸入口。實際設計中為了減少FP2GA的端口,設計成低地址和數據復用線AD[7..0],用一個信號ALE選擇;當其為低電平時,AD[7..0]有效的數據是地址,為高電平時為要寫入RAM中的數據。

靜態圖像顯示過程中為了使眼睛看上去不閃爍,就要使一幀圖像在一秒內至少顯示50次,即使一幀圖像在最多20ms顯示完。要達到這個要求,就要使一個最小模塊的8行在最多20ms內完成一個循環顯示。因為是上半屏與下半屏分開傳輸數據,所以要求在最多1.25ms內傳完半屏數據,時鐘周期需要在0.6μs以下,而選用的FPGA的時鐘頻率可以達到50MHz以上,完全符合顯示的要求。

4 結 語

硬件連接和軟件設計是融為一體的,在最初系統的整體規劃中,就是要兼顧兩者。本設計從硬件連接到最后的軟件實現,都是優化以后的結果。所以按照本設計中的硬件連接情況而設計的軟件,只需要一片2萬門的FPGA就可以實現如此大規模的點陣顯示,并且本設計的LED顯示屏,畫面非常清晰穩定,并且在換幀的過程中能夠做到流暢自如,看不出停滯。

電子發燒友App

電子發燒友App

評論