三維圖像信息處理一直是圖像視頻處理領域的熱點和難點,目前國內外成熟的三維信息處理系統不多,已有的系統主要依賴高性能通用PC完成圖像采集、預處理、重建、構型等囊括底層和高層的處理工作。三維圖像處理數據量特別大、運算復雜,單純依靠通用PC很難達到實時性要求,不能滿足現行高速三維圖像處理應用。

???

本系統中,采用FPGA實現底層的信號預處理算法,其處理數據量很大,處理速度高,但算法結構相對比較簡單,可同時兼顧速度和靈活性。高層處理算法數據量較少、算法結構復雜,可采用運算速度快、尋址方式靈活、通信機制強大的DSP實現[1,4]。

1 三維圖像處理系統組成

1.1 硬件系統構成

???

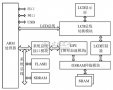

該系統由五個模塊組成,如圖1所示。

???

系統信息處理流程見圖2所示。CCD攝像機采集的多路模擬視頻信號經MAX440按需要選定后,送入模數視頻轉換器SAA7111A將攝像機輸出的模擬全電視信號CVBS轉換成數字視頻信號;之后視頻信號流入圖像預處理器Spartan XC3S400,經過提取中心顏色線、提取激光標志線和物體輪廓線的預處理后,配送到兩片TS201進行定標參數計算、坐標計算、三維重建、數據融合以及三維構型的核心運算;最后將DXF文件數據經由PCI接口傳送到PC,完成三維圖像變換和顯示等最終處理;整個系統的邏輯連接和控制以及部分數據交換由另一片FPGA來完成[1]。

???

在體系結構設計上,FPGA處理器采用SIMD結構,在一個控制單元產生的控制信號下,數據通路中的三個算法并行運行。由于該系統要求處理速度較高,因而在數據通路中采用了流水線技術以提高速度。此外,本系統中為圖像存儲采用了許多大容量高速FIFO,以達到減少地址線,簡化控制的目的。

1.2 處理器芯片

???

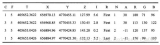

為滿足系統大數據量快速處理的要求,三款核心芯片均為最新高性能產品,其硬件方面的特點給系統設計帶來極大的方便,其優異的運算性能可確保系統的快速實時性。

???

FPGA芯片采用Xilinx公司近期推出的采用90nm工藝的Spartan3系列的XC3S400,該系列芯片是目前為止工藝最先進、價格較低、單位成本內I/O管腳最多的平臺級可編程邏輯器件。XC3S400芯片內部時鐘頻率可達326MHz,信號擺幅1.14V和3.45V,I/O口支持622Mbps的數據傳輸率,具有高性能SelectRAM內部存儲器,多達4個數字時鐘管理器模塊和8個全局時鐘多路復用緩沖器。

???

DSP采用ADI公司的最新款基于并行處理設計、具有海量片內RAM的TigerSHARC ADSP TS201。其內部集成的RAM容量高達24Mbit,核心速度最高達600MHz。內設雙運算模塊,每個包含一個ALU、MUL、64bit移位寄存器、32個32bit寄存器組和一個128bit通信邏輯單元,相關的數據對齊緩沖器;雙整數ALU,各有獨立的寄存器組,提供數據尋址和指針操作;4個128bit寬度內部總線,每個都連接到6個4Mbit的內部存儲器塊;提供與主機處理器、多處理器空間、片外存儲器映射外設、外部SRAM和SDRAM相連的外部端口;14通道DMA控制器;4個全雙工低電壓差分信號輸入的Link Port;具有片內仲裁總線,用于多DSP無縫的連接。

???

數字化器采用了Philips公司的增強視頻輸入處理器(EVIP)——SAA7111A模數轉換器。該產品廣泛應用于個人視頻、多媒體、數字電視、可視電話、圖像處理、實時監控等領域,純3.3V CMOS工藝的模擬視頻前端和數字視頻編碼器,能夠將PAL/TSC/ECAM視頻信號解碼為與CCIR-601相兼容的多種數字視頻格式,支持TV或VTR信號源的CVBS或S-Video視頻信號,最高圖像分辨率可達720×576,支持24位真彩色,可以通過串行總線動態配置

SAA7111A模數轉換器的工作方式和各種參數。

2 模塊設計

2.1 視頻采集與數字化模塊

???

由于模擬攝像機采集的是PAL制的復合視頻信號(CVBS),所以必須先將其數字化才能開始后繼數字視頻處理。視頻采集與數字化模塊主要包括一片視頻多路復用器MAX440、一片SAA7111A、一片I2C接口控制器PCF8584和一些連接邏輯。MAX440用來快速切換來自不同模擬輸入端的模擬視頻流,SAA7111A模數轉換器是該模塊的核心,它采集模擬視頻,將其數字化為720×576的RGB(8,8,8)真彩色信號格式的數字視頻,其輸出的RGB真彩色信號為16位,其中高字節和低字節數據周期分別為74ns和37ns,即低字節的頻率是高字節的1倍。這樣就要利用觸發器和兩個分別為13.5MHz和27MHz的時鐘信號,將輸入數據格式轉換為24位、周期均為74ns的RGB真彩色信號,此外,它還為整個硬件系統提供必要的時鐘和同步信號;PCI接口控制器通過PCF8584來配置和控制SAA7111A,連接邏輯由FPGA實現。

2.2 FPGA圖像預處理模塊

???

預處理從巨大的視頻信息中提取極少量的對三維重建有用的信息傳送至DSP后處理。該模塊包括主處理FPGA芯片和高速FIFO,負責實時采集視頻信號并對采集到的無壓縮的視頻信息進行預處理,包括提取激光中心線、提取輪廓線、提取中心顏色線三個部分。

???

為了提高視頻采集的整體性能,更重要的是為預處理提供相鄰的有激光幀和無激光幀,必須通過視頻幀緩存首先暫存無激光幀。緩存由3片AverLogic公司的AL422B及一些由FPGA實現的連接邏輯組成;當前端模塊輸出無激光幀時,SA7111A控制3片AL422B寫操作,將其存入FIFO;當前端輸出有激光幀時,后端的視頻處理模塊控制3片AL422B進行讀操作,讀出暫存在其中的無激光幀數據。預處理FPGA將讀取的無激光幀和有激光幀進行相減運算。輸出同樣采用3組緩存分別用來暫存激光樣條數據、目標輪廓線數據和圖像中心線數據;所有模塊均采用同步時鐘控制,同步時鐘采用由SAA7111A模數轉換器產生的LLC2信號。為了提高系統速度,算法復雜、耗時較長的計算過程進行了流水線處理。

2.3 DSP三維重建模塊

???

為了應對三維圖像大數據量復雜高速運算的需要,這里采用了兩片TigerSHARC 201芯片并行三維重建運算。由控制FPGA對兩片DSP所要處理的圖像進行任務分配,DSP結合預處理FPGA存入FIFO的數據和PCI總線所給處理參數進行定標參數計算、坐標計算、三維重建和構型。由于TS201內部集成的總線仲裁機制,雙DSP可以實現無縫連接,大大減小了多DSP協調工作的設計難度。DSP間的連接是依靠其擁有的全雙工LinkPort,它采用LVDS(低電平差分信號)輸入數據。鏈路口能獨立或同時工作,在時鐘的上升沿和下降沿鎖存數據。鏈路時鐘頻率最高可以與處理器核相同,高達500MHz,每個鏈路能完成500Mbps的單向數據傳輸。每個DSP的4個LinkPort合起來最大的通透率為4.0Gbps。連線短且簡單,不需要額外的輔助電路,且可有效防止連線長引起的信號畸變。LinkPort傳輸協議由控制FPGA完成。

2.4 PCI通信接口模塊

???

根據三維信息獲取系統的速度傳輸要求,采用PCI接口完成該系統與通用PC的信息交互。PCI接口控制器是硬件部分的控制中心和數據交換中心,它接收設備驅動程序的命令和數據,配置和控制系統的各個模塊使其協調工作,完成系統任務;它還負責將采集到和處理后的數據通過PCI總線轉送給通用PC。本系統采用PLX公司的32bit/33MHz PCI9030作為接口芯片,串行EEPROM-FM93CS56L電可擦除只讀存儲器保存PCI9030的配置信息。

2.5 系統控制與數據交換模塊

???

控制單元對處理器的數據處理單元和輸入數據格式轉換單元以及所有FIFO存儲器產生控制,與預處理FPGA配合完成DSP的LinkPort協議。由于數據處理單元中為流水處理,在控制單元的設計中要特別注意由流水線產生的固定周期的延時,延時的周期數等于相應流水線的級數。控制單元還與PCI接口連接,接收來自主計算機的控制信號和背景閾值等信息。控制FPGA還是SAA7111A、PCI接口和DSP之間的圖像和信息交換的橋梁,為其提供所需要的參數和數據信息。

3 軟件設計與實現

3.1 圖像預處理算法

???

如圖3,激光帶預處理算法的實現[2]為:由于有激光幀和無激光幀是依次交替產生的,因此首先要保存一幀有激光幀,在其下一幀,即無激光幀到來時,將保存的有激光幀和當前無激光幀的相同行、列的點相減,再對結果進行亮度提取,處理完成后的數據存入目標緩存。

???

如圖4,實現提取輪廓線算法分為三個部分[3],首先由計算比較模塊對輸入像素點的值與預先計算好的閾值進行比較,判斷其是否為目標像素;然后利用一個序列檢測模塊進行一維尺度濾波以去除某些噪聲點;再經過一個邊緣檢測模塊,提取出每行的第一個目標像素作為目標的左邊緣點;完成后將此點所對應的列地址數據存入目標緩存。在某些情況下,可能整行都檢測不到邊緣點,這時將0存入目標緩存作為無邊緣點的標識。

???

提取中心線算法實現比較簡單,只需對目標緩存的寫允許信號加以控制,使RGB數據只能在每行的中心點處寫入目標緩存即可。

3.2 三維重建和構型

???

如圖5所示,高速DSP將根據預處理信息得到的激光標志線、輪廓線和中心顏色線數據與源數字化圖像結合起來進行三維重建。首先根據獲取的圖像標志點數據結合控制點三維坐標數據計算出系統定標數據;其次根據輪廓線計算物體外表面展開圖,再依據定標數據結合展開圖和機械參數對圖像中的坐標點進行計算,給出數據集,輸出深度數據文件;最后對多次掃描的數據進行融合,將離散點構型成立體模型(或立體彩色模型),將模型生成DXF、STL等數據文件傳入PC機,使用后端處理軟件進行顯示[3]。

3.3 算法實現

???

圖像預處理算法設計使用Verilog HDL在Xilinx公司的ISE8.1集成編譯環境下成功實現;FPGA開發流程不再贅述。

???

DSP三維重建算法已使用C語言在ADI公司Visual DSP++環境下成功實現[4]。算法實現步驟如下:①用C語言編程實現算法。②使用Visual DSP++編譯器將源程序編譯成目標文件。③根據產生的目標文件,分析結果及源程序結構并優化源代碼。④應用TigerSHARC 201評估板進行運算時間評估。⑤重復上述步驟直至達到系統實時性要求,最后下載到目標板。

???

整個系統聯機運行穩定,滿足設計要求,實時性好。

???

實時三維圖像信息處理以其數據量大、速度要求高、處理過程復雜的特點使其難以使用集成電路實現。本文研究的以目前最新高性能處理器的FPGA+DSP為核心架構的三維圖像處理系統精心設計了算法的硬件實現,充分利用了兩種處理器的長處。實驗表明,該系統有著良好的性能,對實現基于網絡的實時三維掃描應用,如三維傳真、機械遠程加工、快速成型和虛擬現實,有著重要的意義。

參考文獻

[1] LEI HAIJUN,LI DEHUA.High-Speed aerial image processing system based on DSP,In neural nerwork and distributed processing,Proceedings of SPIE Vol.4555,2001:131-136

[2] 雷海軍,李德華,王建永等.一種結構光條紋中心快速檢測方法[J].華中科技大學學報,2003,31(1):74-76.

[3] 金 剛.三維掃描儀中三維信息獲取理論與技術研究[D].華中科技大學博士學位論文,2002,(3)

[4] 陸海東,吳明贊.基于FPGA+DSP結構的小波圖像處理系統設計[J],電子技術應用,2006,(3)93-95

電子發燒友App

電子發燒友App

評論