TL16C550D--具有自動流控制的異步通信元件

The TL16C550D and the TL16C550DI are speed and operating voltage upgrades (but functional equivalents) of the TL16C550C asynchronous communications element (ACE), which in turn is a functional upgrade of the TL16C450. Functionally equivalent to the TL16C450 on power up (character or TL16C450 mode), the TL16C550D and the TL16C550DI, like the TL16C550C, can be placed in an alternate FIFO mode. This relieves the CPU of excessive software overhead by buffering received and transmitted characters. The receiver and transmitter FIFOs store up to 16 bytes including three additional bits of error status per byte for the receiver FIFO. In the FIFO mode, there is a selectable autoflow control feature that can significantly reduce software overload and increase system efficiency by automatically controlling serial data flow using RTS output and CTS input signals.

The TL16C550D and TL16C550DI perform serial-to-parallel conversions on data received from a peripheral device or modem and parallel-to-serial conversion on data received from its CPU. The CPU can read the ACE status at any time. The ACE includes complete modem control capability and a processor interrupt system that can be tailored to minimize software management of the communications link.

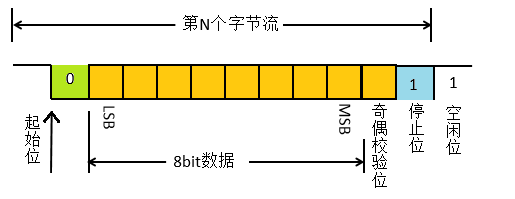

Both the TL16C550D and the TL16C550DI ACE include a programmable baud rate generator capable of dividing a reference clock by divisors from 1 to 65535 and producing a 16× reference clock for the internal transmitter logic. Provisions are included to use this 16× clock for the receiver logic. The ACE accommodates up to a 1.5-Mbaud serial rate (24-MHz input clock) so that a bit time is 667 ns and a typical character time is 6.7 ms (start bit, 8 data bits, stop bit).

Two of the TL16C450 terminal functions on the TL16C550D and the TL16C550DI have been changed to TXRDY and RXRDY, which provide signaling to a DMA controller.

The TL16C550D is being made available in a reduced pin count package, the 32-pin RHB package. This is accomplished by eliminating some signals that are not required for some applications. These include the CS0, CS1, ADS, RD2, WR2, and RCLK input signals and the DDIS, TXRDY, RXRDY, OUT1, OUT2, and BAUDOUT output signals. There is an internal connection between BAUDOUT and RCLK.

All of the functionality of the TL16C550D is maintained in the RHB package.

The TL16C550D is being made available in a reduced pin count package, the 24-pin ZQS package. This is accomplished by eliminating some signals that are not required for some applications. These include the CS0, CS1, ADS, RD2, WR2, DSR, RI, DCD, and RCLK input signals and the DDIS, TXRDY, RXRDY, OUT1, OUT2, DTR, and BAUDOUT output signals. There is an internal connection between BAUDOUT and RCLK.

Most of the functionality of the TL16C550D is maintained in the ZQS package, except that which involves the eliminated signals.

特性

Programmable Auto-RTS and Auto-CTS

In Auto-CTS Mode, CTS Controls Transmitter

In Auto-RTS Mode, RCV FIFO Contents

and Threshold Control RTS

Serial and Modem Control Outputs Drive a RJ11 Cable

Directly When Equipment Is on the Same Power Drop

Capable of Running With All Existing

TL16C450 Software

After Reset, All Registers Are Identical to the

TL16C450 Register Set

Up to 24-MHz Clock Rate for up to 1.5-Mbaud

Operation With VCC = 5 V

Up to 20-MHz Clock Rate for up to 1.25-Mbaud

Operation With VCC = 3.3 V

Up to 48-MHz Clock Rate for up to 3-Mbaud

Operation with VCC = 3.3 V (ZQS Package Only,

Divisor = 1)

Up to 40-MHz Clock Rate for up to 2.5-Mbaud

Operation with VCC = 3.3 V (ZQS Package Only,

Divisor ≥ 2)

Up to 16-MHz Clock Rate for up to 1-Mbaud

Operation With VCC = 2.5 V

In the TL16C450 Mode, Hold and Shift Registers Eliminate the

Need for Precise Synchronization Between the CPU and Serial Data

Programmable Baud Rate Generator Allows Division of Any Input

Reference Clock by 1 to (216 –1) and Generates an Internal 16× Clock

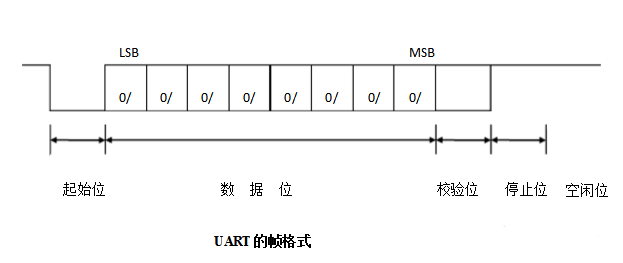

Standard Asynchronous Communication Bits (Start, Stop, and Parity)

Added to or Deleted From the Serial Data Stream

5-V, 3.3-V, and 2.5-V Operation

Independent Receiver Clock Input

Transmit, Receive, Line Status, and Data Set

Interrupts Independently Controlled

Fully Programmable Serial Interface Characteristics:

5-, 6-, 7-, or 8-Bit Characters

Even-, Odd-, or No-Parity Bit Generation and Detection

1-, 1 =-, or 2-Stop Bit Generation

Baud Generation (dc to 1 Mbit/s)

False-Start Bit Detection

Complete Status Reporting Capabilities

3-State Output TTL Drive Capabilities for Bidirectional

Data Bus and Control Bus

Line Break Generation and Detection

Internal Diagnostic Capabilities:

Loopback Controls for Communications Link Fault Isolation

Break, Parity, Overrun, and Framing Error Simulation

Fully Prioritized Interrupt System Controls

Modem Control Functions (CTS, RTS, DSR, DTR, RI, and DCD)

Available in 48-Pin PT, 48-Pin PFB, 32-Pin RHB,

and 24-Pin ZQS Packages

Number of Channels 1??

FIFOs(bytes) 16??

Operating Voltage(V) 2.5, 3.3, 5??

Operating Temp Range(Celsius) -40 to 85,0 to 70??

Pin/Package 24BGA MICROSTAR JUNIOR, 32QFN, 48LQFP, 48TQFP??

Rating Catalog??

Tx / Rx FIFO INT Trig No / 4 Levels??

Auto RTS/CTS Yes??

CPU Interface X86??

Baud Rate (max) at Vcc = 1.8V and with 16X Sampling(Mbps) N/A??

Baud Rate (max) at Vcc = 2.5V and with 16X Sampling(Mbps) 1.0??

Baud Rate (max) at Vcc = 3.3V and with 16X Sampling(Mbps) 1.25??

Baud Rate (max) at Vcc = 5.0V and with 16X Sampling(Mbps) 1.5??

電子發燒友App

電子發燒友App

評論