CXL(Compute Express Link)是一種業(yè)界支持的高速緩存一致性互連協(xié)議,用于處理器、內(nèi)存擴(kuò)展和加速器之間的通信。

2024-03-20 13:56:53 52

52

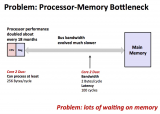

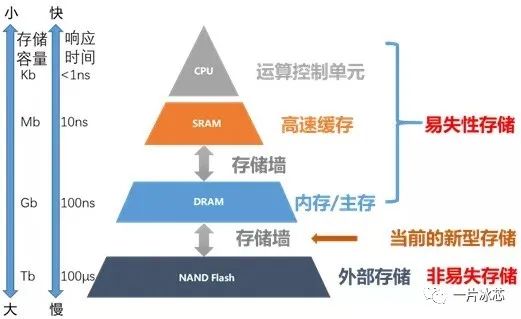

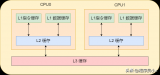

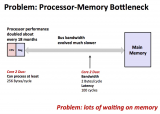

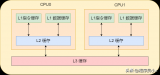

高速緩存(Cache)主要是為了解決CPU運(yùn)算速度與內(nèi)存(Memory)讀寫速度不匹配的矛盾而存在, 是CPU與存儲(chǔ)設(shè)備之間的臨時(shí)存貯器,容量小,但是交換速度比內(nèi)存快。內(nèi)置高速緩存通常對(duì)CPU的性能提升具有較大作用。

2024-01-22 16:07:33 489

489

結(jié)合5nm和6nm工藝節(jié)點(diǎn),采用先進(jìn)的小芯片(Chiplets)設(shè)計(jì),全新的計(jì)算單元和第二代AMD高速緩存技術(shù),相比AMD RDNA 2架構(gòu)的每瓦性能提高54%;

2024-01-04 16:27:36 509

509

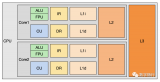

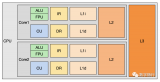

CPU的核心功能包括數(shù)據(jù)運(yùn)算和指令控制。CPU運(yùn)算的數(shù)據(jù)和執(zhí)行的指令全部存儲(chǔ)在CPU的寄存器中,這些數(shù)據(jù)和指令又都來自于CPU高速緩存。

2024-01-02 16:01:48 662

662

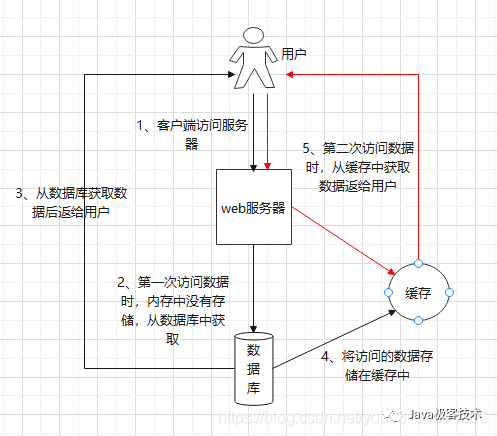

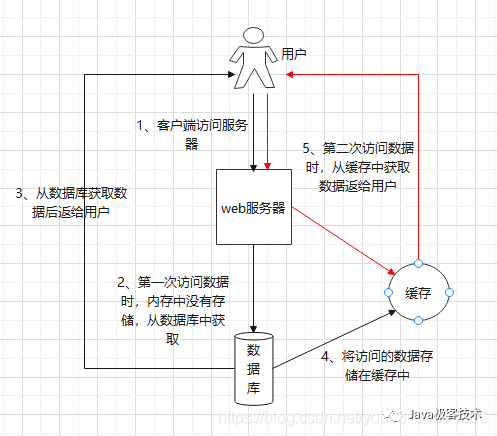

緩存預(yù)熱就是系統(tǒng)上線后,提前將相關(guān)的緩存數(shù)據(jù)直接加載到緩存系統(tǒng)。

2023-12-25 09:41:02 250

250

靠近 CPU 的小、快速的高速緩存存儲(chǔ)器(cache memory)做為一部分存儲(chǔ)在相對(duì)慢速的主存儲(chǔ)器(main memory)中數(shù)據(jù)和指令的緩沖區(qū)域。

2023-12-25 09:21:50 241

241

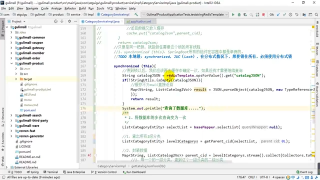

MyBatis是一種輕量級(jí)的持久化框架,它提供了一級(jí)緩存和二級(jí)緩存的機(jī)制來優(yōu)化數(shù)據(jù)庫操作性能。一級(jí)緩存是默認(rèn)開啟的,而二級(jí)緩存需要手動(dòng)配置啟用。 一、一級(jí)緩存 1.1 緩存生命周期 一級(jí)緩存存在于

2023-12-03 11:55:11 438

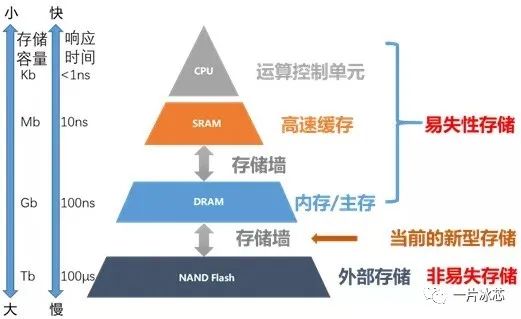

438 SRAM是目前最成熟的易失性高速存儲(chǔ)器,通常由6管(6T)實(shí)現(xiàn)數(shù)據(jù)的讀寫,可以用做CPU和內(nèi)存(DRAM)之間的高速緩存。

2023-10-31 17:46:55 1259

1259

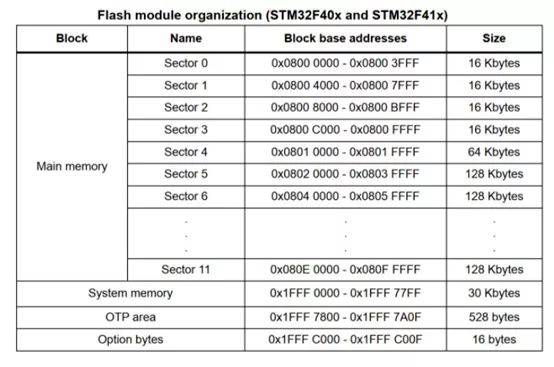

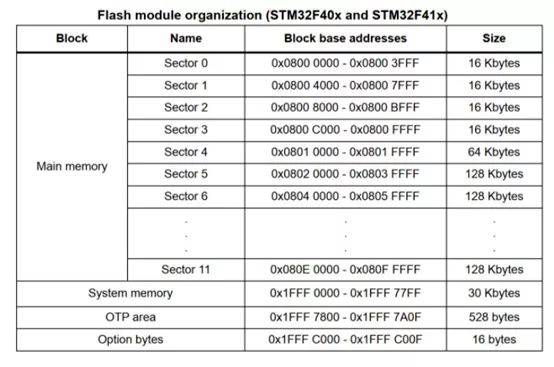

STM32加密問題:怎樣預(yù)置一段Flash讀保護(hù)和清除讀保護(hù)的程序 在STM32加密方案中,為了對(duì)芯片進(jìn)行加密,我們需要加入讀保護(hù)功能。讀保護(hù)功能即使未經(jīng)授權(quán)的人無法讀取芯片的Flash程序

2023-10-29 17:24:46 1083

1083 STM32的Flash寫了保護(hù)怎么辦?STM32如何設(shè)置讀保護(hù)和解除讀保護(hù)? 一、STM32的Flash寫了保護(hù)怎么辦? 當(dāng)STM32的Flash寫了保護(hù)后,我們需要先了解STM32的Flash

2023-10-29 17:24:43 5495

5495 講講STM32單片機(jī)Flash的讀保護(hù)和寫保護(hù)

2023-10-26 15:52:31 3243

3243

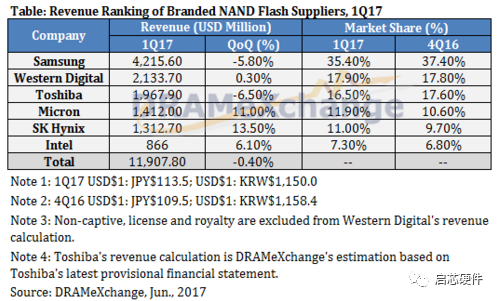

緩存技術(shù)被認(rèn)為是減輕服務(wù)器負(fù)載、降低網(wǎng)絡(luò)擁塞、增強(qiáng)Web可擴(kuò)展性的有效途徑之一,其基本思想是利用客戶訪問的時(shí)間局部性(Temproral Locality)原理, 將客戶訪問過的內(nèi)容在Cache

2023-10-08 14:07:17 300

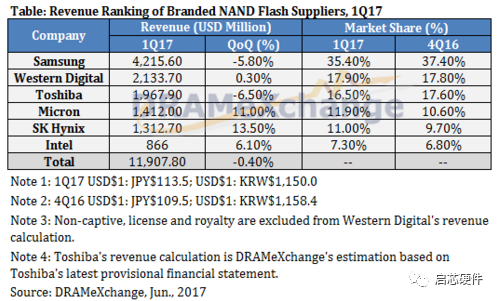

300 目前,NOR FLASH和NAND FLASH是市場(chǎng)上主要的非易失性閃存技術(shù),但是據(jù)我了解,還是有很多工程師分不清NAND FLASH與NOR FLASH。

2023-10-01 14:05:00 468

468

一、摘要 說到緩存,面試官基本上會(huì)繞不開以下幾個(gè)話題! 項(xiàng)目中哪些地方用到了緩存?為什么要使用緩存?怎么使用它的?引入緩存后會(huì)帶來哪些問題? 這些問題,基本上是互聯(lián)網(wǎng)公司面試時(shí)必問的一些問題,如果

2023-09-30 15:29:00 338

338

電子發(fā)燒友網(wǎng)站提供《管理基于Cortex-M7的MCU的高速緩存一致性.pdf》資料免費(fèi)下載

2023-09-25 10:11:48 0

0 電子發(fā)燒友網(wǎng)站提供《利用MPLAB Harmony v3在Cortex-M7(SAM S70/E70/V70/V71)MCU上創(chuàng)建不可高速緩存的存儲(chǔ)區(qū).pdf》資料免費(fèi)下載

2023-09-20 11:50:46 0

0 電子發(fā)燒友網(wǎng)站提供《利用MPLAB Harmony v3在Cortex-M7 MCU上在運(yùn)行時(shí)使用高速緩存維護(hù)操作處理高速緩存一致性問題.pdf》資料免費(fèi)下載

2023-09-20 11:40:24 0

0 電子發(fā)燒友網(wǎng)站提供《使用MPLAB Harmony v3基于PIC32MZ MCU在運(yùn)行時(shí)使用高速緩存維護(hù)操作處理高速緩存一致性問題.pdf》資料免費(fèi)下載

2023-09-19 16:28:10 0

0 STM32MP151A/D器件基于高性能ARM?Cortex?-A7 32位RISC內(nèi)核,運(yùn)行頻率高達(dá)800 MHz。

Cortex-A7處理器包括一個(gè)32K字節(jié)的一級(jí)指令高速緩存、一個(gè)32K字節(jié)

2023-09-13 07:23:32

片上閃存特性和系統(tǒng)框圖

? 存儲(chǔ)空間組織架構(gòu)

? 用戶閃存

? 系統(tǒng)閃存

? OTP

? 選項(xiàng)字節(jié)

? 閃存讀接口

? 等待周期

? 指令預(yù)取

? 指令高速緩存

? 數(shù)據(jù)高速緩存

? 擦除和編程操作

? 讀保護(hù)和寫保護(hù)

? STM32F2和STM32F1的閃存特性比較

2023-09-13 07:10:38

什么是高速緩存?? 高速存儲(chǔ)器塊,包含地址信息(通常稱作TAG)和相關(guān)聯(lián)的數(shù)據(jù)。? 目的是提高對(duì)存儲(chǔ)器的平均訪問速度? 高速緩存的應(yīng)用基于下面兩個(gè)程序的局部性 :? 空間局部性:如果一個(gè)存儲(chǔ)器的位置

2023-09-07 08:22:51

1.具有雙發(fā)布功能的高性能6級(jí)流水線(每個(gè)時(shí)鐘周期最多執(zhí)行兩條指令)。

2.作為系統(tǒng)總線的64位AXI總線接口。

3.可選的指令高速緩存(4至64KB)和數(shù)據(jù)高速緩存(4至64KB),每個(gè)高速

2023-09-04 06:28:56

?v8.3-A擴(kuò)展中引入的加載獲取(LDAPR)指令·ARM?v8.4-A擴(kuò)展中引入的Dot產(chǎn)品支持說明。

·EL1和EL0高速緩存控制的陷阱、支持Spectre變體4軟件緩解的PSTATE SSB

2023-08-29 08:05:54

)指令以及Armv8.4-A擴(kuò)展中引入的點(diǎn)積指令。

Cortex-A77內(nèi)核具有1級(jí)(L1)內(nèi)存系統(tǒng)和專用的集成2級(jí)(L2)高速緩存。

它還包括一個(gè)超標(biāo)量、可變長度、無序的管道。

Cortex-A77

2023-08-29 07:51:54

就是防止ICE讀取MCU flash中的代碼的保護(hù),手冊(cè)上怎么找不到呢?

2023-08-28 08:20:39

和設(shè)備放置·可選的系統(tǒng)級(jí)高速緩存(SLC)。

有關(guān)SLC存儲(chǔ)系統(tǒng)功能的更多信息,請(qǐng)參閱第867頁的6.1關(guān)于SLC存儲(chǔ)系統(tǒng)。

CMN-650支持ARM?AMBA?5 CHI版本D,包括以下功能:

·內(nèi)存系統(tǒng)性能資源分區(qū)和監(jiān)控(MPAM)·具有兩部分響應(yīng)的永久緩存維護(hù)操作(PCMO)

2023-08-25 07:49:25

受影響的ARM CPU上,建議的緩解措施包括在轉(zhuǎn)換到需要保護(hù)以前的執(zhí)行上下文的執(zhí)行上下文時(shí),使部分或全部分支預(yù)測(cè)器緩存失效。

有關(guān)術(shù)語執(zhí)行上下文的定義,請(qǐng)參見第1.2節(jié)。

CVE-2018-3639,也

2023-08-25 07:36:27

)指令以及Armv8.4-A擴(kuò)展中引入的點(diǎn)積指令。

Cortex-A77內(nèi)核具有1級(jí)(L1)內(nèi)存系統(tǒng)和專用的集成2級(jí)(L2)高速緩存。

它還包括一個(gè)超標(biāo)量、可變長度、無序的管道。

Cortex-A77

2023-08-24 07:30:56

電子發(fā)燒友網(wǎng)站提供《LSI MegaRAID CacheVault技術(shù)工具.pdf》資料免費(fèi)下載

2023-08-23 14:22:59 0

0 電子發(fā)燒友網(wǎng)站提供《CacheVault技術(shù)(CVM02 CVPM02和CVPM05)產(chǎn)品介紹.pdf》資料免費(fèi)下載

2023-08-23 09:23:55 0

0 電子發(fā)燒友網(wǎng)站提供《MySQL服務(wù)器優(yōu)化LSI MegaRAID CacheCade Pro 2.0讀寫緩存軟件和固態(tài)硬盤(SSD).pdf》資料免費(fèi)下載

2023-08-21 14:19:00 0

0 CPU高速緩存集成于CPU的內(nèi)部,其是CPU可以高效運(yùn)行的成分之一,本文圍繞下面三個(gè)話題來講解CPU緩存的作用

2023-08-21 12:17:35 793

793

電子發(fā)燒友網(wǎng)站提供《LSI SAS 9207-4i4e 8端口、6Gb/s SAS+SATA轉(zhuǎn)PCI高速主機(jī)總線適配器.pdf》資料免費(fèi)下載

2023-08-21 11:05:21 4

4 Cortex-A7 MPCore處理器是一款實(shí)現(xiàn)ARMv7-A架構(gòu)的高性能、低功耗處理器。

Cortex-A7 MPCore處理器在帶有一級(jí)高速緩存子系統(tǒng)、可選集成GIC和可選二級(jí)高速緩存控制器的單個(gè)多處理器設(shè)備中具有一到四個(gè)處理器

2023-08-18 07:25:18

吞吐量的Thumb-2技術(shù)。

該流水線具有雙重算術(shù)邏輯單元(ALU),具有雙重指令發(fā)布,以有效地利用其他資源,例如寄存器堆。

該處理器在具有最多兩個(gè)處理器的群集中具有1級(jí)(L1)數(shù)據(jù)高速緩存一致性

2023-08-18 06:34:29

為了有效利用其他資源,例如寄存器文件,實(shí)現(xiàn)了有限的雙指令發(fā)布。

提供硬件加速器一致性端口(ACP)以減少在與其他主機(jī)共享存儲(chǔ)器時(shí)對(duì)緩慢的軟件高速緩存維護(hù)操作的要求。

通過中斷和重新啟動(dòng)加載存儲(chǔ)多條指令

2023-08-18 06:09:34

Neoverse N1處理器集群。

該系統(tǒng)通過以下方式在高速緩存一致性加速器互連(CCIX)協(xié)議的背景下演示ARM技術(shù):

·在N1 SoC和加速卡之間運(yùn)行一致的流量。

·兩個(gè)N1 SoC之間的連貫通信。

·支持開發(fā)支持CCIX的FPGA加速器。

2023-08-17 08:14:26

(SB)、所有內(nèi)核以及內(nèi)核之間共享的邏輯。

共享邏輯包括CPU橋(CPU側(cè))(CBC)、L2高速緩存,以及維護(hù)核心中的高速緩存與L2高速緩存和低延遲RAM(LLRAM)存儲(chǔ)器之間的一致性的一致性邏輯

2023-08-17 08:02:29

Cortex-A8處理器是一款高性能、低功耗、高速緩存的應(yīng)用程序處理器,可提供完整的虛擬內(nèi)存功能。

該處理器的功能包括:

·完全實(shí)現(xiàn)ARM體系結(jié)構(gòu)v7-A指令集·具有高級(jí)可擴(kuò)展接口(AXI)的可配

2023-08-17 07:43:12

Cortex-A5處理器是一款高性能、低功耗的ARM宏單元,具有提供完整虛擬內(nèi)存功能的一級(jí)高速緩存子系統(tǒng)。

Cortex-A5處理器實(shí)現(xiàn)了ARMv7架構(gòu),并在Jazelle狀態(tài)下運(yùn)行32位ARM指令、16位和32位Thumb指令以及8位JAVA?字節(jié)碼

2023-08-17 07:16:41

執(zhí)行模式將嵌入式內(nèi)存內(nèi)容轉(zhuǎn)儲(chǔ)到調(diào)試器,使其適用于芯片啟動(dòng)和調(diào)查軟件故障,如高速緩存一致性錯(cuò)誤。

它允許快速測(cè)試內(nèi)存和內(nèi)存保護(hù)邏輯。

因此,MBIST事務(wù)是使用IP核時(shí)鐘連續(xù)執(zhí)行的,因此,可以通過以全功能

2023-08-17 07:10:53

Cortex-A17 MPCore處理器是一款高性能、低功耗的處理器,采用ARMv7架構(gòu)。

Cortex-A17 MPCore處理器在帶有L1和L2高速緩存子系統(tǒng)的單個(gè)多處理器設(shè)備中具有一到四個(gè)處理器。

2023-08-17 07:06:31

Cortex-A9處理器是一款高性能、低功耗的ARM宏單元,具有提供完整虛擬內(nèi)存功能的一級(jí)高速緩存子系統(tǒng)。

Cortex-A9處理器實(shí)現(xiàn)ARMv7-A架構(gòu),并在Jazelle狀態(tài)下運(yùn)行32位ARM

2023-08-17 06:53:00

電子發(fā)燒友網(wǎng)站提供《理解CacheVault模塊系統(tǒng)工程說明.pdf》資料免費(fèi)下載

2023-08-16 15:45:54 0

0 在多處理器配置中,在監(jiān)聽控制單元(SCU)的控制下,高速緩存相關(guān)群集中最多有四個(gè)Cortex-A32處理器可用,該監(jiān)聽控制單元維護(hù)L1和L2數(shù)據(jù)高速緩存一致性。

Cortex-A32處理器支持

2023-08-16 06:54:59

電子發(fā)燒友網(wǎng)站提供《MegaRAID CacheVault Flash模塊02快速安裝指南.pdf》資料免費(fèi)下載

2023-08-15 10:31:35 0

0 在多處理器配置中,在監(jiān)聽控制單元(SCU)的控制下,高速緩存相關(guān)群集中最多有四個(gè)Cortex-A35處理器可用,該監(jiān)聽控制單元維護(hù)L1和L2數(shù)據(jù)高速緩存一致性。

Cortex-A35處理器支持

2023-08-12 07:39:00

在多處理器配置中,在監(jiān)聽控制單元(SCU)的控制下,高速緩存相關(guān)群集中最多有八個(gè)處理器可用,該監(jiān)聽控制單元維護(hù)L1、L2和L3數(shù)據(jù)高速緩存一致性。

本節(jié)提供周期模型與硬件的功能比較的摘要,以及周期模型的性能和準(zhǔn)確性

2023-08-12 07:30:35

的電源、性能和面積(PPA)目標(biāo)和其他關(guān)鍵要求。

RD-V2提供以下功能:

·32個(gè)MP1 ARMv9.0-A ARM?Neoverse?V2內(nèi)核,支持直接連接和2MB專用,

每個(gè)核心的專用二級(jí)高速緩存

2023-08-11 07:54:59

電子發(fā)燒友網(wǎng)站提供《優(yōu)化數(shù)據(jù)庫性能使用LSI MegaRAID CacheCade Pro 2.0讀/寫緩存軟件.pdf》資料免費(fèi)下載

2023-08-10 17:38:15 0

0 電子發(fā)燒友網(wǎng)站提供《MegaRAID CacheVault電源模塊02快速安裝指南.pdf》資料免費(fèi)下載

2023-08-09 10:35:22 0

0 Cortex?-A510是高效內(nèi)核。

Cortex?-A510內(nèi)核在稱為聯(lián)合體的模塊中實(shí)施,該模塊最多包含兩個(gè)內(nèi)核。在雙核復(fù)合體中,向量處理單元(VPU)、L2轉(zhuǎn)換后備緩沖器(TLB)和L2高速緩存邏輯在核心之間共享。

2023-08-09 07:50:45

電子發(fā)燒友網(wǎng)站提供《Broadcom CacheVault功率模塊02和CacheVault功率模塊05入門指南.pdf》資料免費(fèi)下載

2023-08-08 09:16:51 0

0 )AHB(高級(jí)高性能總線)接口。它是的成員ARM9E-S Thumb?高性能32位片上系統(tǒng)(SoC)系列處理器,它非常適合廣泛的嵌入式應(yīng)用程序。的大小指令和數(shù)據(jù)高速緩存以及指令和數(shù)據(jù)SRAM是單獨(dú)

2023-08-08 07:33:30

電子發(fā)燒友網(wǎng)站提供《LSI SAS 9200-8e高速主機(jī)總線適配器產(chǎn)品介紹.pdf》資料免費(fèi)下載

2023-08-07 09:55:15 0

0 ARM946E-S? 是一個(gè)可合成的宏小區(qū),結(jié)合了ARM9E-S? 帶指令和數(shù)據(jù)高速緩存的處理器核心、帶保護(hù)單元的緊密耦合指令和數(shù)據(jù)SRAM存儲(chǔ)器、寫緩沖區(qū)和AMBA? (高級(jí)微處理器總線體系結(jié)構(gòu)

2023-08-02 17:50:31

CCI-400將互連和一致性功能組合到一個(gè)模塊中。它支持最多可連接兩個(gè)ACE主機(jī),例如:

?Cortex?-A7處理器。

?Cortex-A15處理器。

?Cortex-A17處理器。

?Cortex-A53處理器。

?Cortex-A57處理器。

CCI-400還支持多達(dá)三個(gè)ACE Lite主機(jī),例如ARM Mali?-T600系列圖形處理器單元(GPU)。

在所有這些接口上都有可選的DVM消息支持,以管理分布式內(nèi)存管理單元(MMU),例如CoreLink MMU-400。這些可以通信通過具有多達(dá)三個(gè)ACE Lite從機(jī)的CCI-400。

硬件管理的一致性可以通過以下方式提高系統(tǒng)性能并降低系統(tǒng)功耗共享片上數(shù)據(jù)。管理一致性有以下好處:

?減少外部存儲(chǔ)器訪問。

?減少軟件開銷。

2023-08-02 17:33:01

高性能和高性能之間進(jìn)行權(quán)衡代碼密度。ARM922T處理器是哈佛高速緩存體系結(jié)構(gòu)處理器,其目標(biāo)是全內(nèi)存管理、高性能和低功率是至關(guān)重要的。此設(shè)計(jì)中的獨(dú)立指令和數(shù)據(jù)緩存每個(gè)大小為8KB,具有8字線長度。ARM922T實(shí)現(xiàn)了增強(qiáng)型ARM體系結(jié)構(gòu)v4 MMU為指令和數(shù)據(jù)地址

2023-08-02 15:44:14

:

?用于增強(qiáng)操作系統(tǒng)安全性的TrustZone架構(gòu)?專為高性能系統(tǒng)設(shè)計(jì)的主、從和外圍AXI/AMBA接口?智能能源管理器(IEM)支持。

高速緩存控制器是一個(gè)統(tǒng)一的、物理尋址的、物理標(biāo)記的8路高速緩存。您可

2023-08-02 15:09:49

當(dāng)中央處理器(CPU)產(chǎn)生大量內(nèi)存流量時(shí),添加片上二級(jí)緩存(也稱為二級(jí)緩存,L2CC)是提高計(jì)算機(jī)系統(tǒng)性能的公認(rèn)方法。根據(jù)定義,二級(jí)緩存假定存在與CPU緊密耦合或內(nèi)部的一級(jí)緩存或主緩存。

2023-08-02 13:11:45

高速緩存體系結(jié)構(gòu)處理器,適用于全內(nèi)存管理、高性能和低功耗至關(guān)重要的多程序應(yīng)用。此設(shè)計(jì)中的獨(dú)立指令和數(shù)據(jù)緩存大小分別為16KB,具有8字線長度。ARM920T處理器實(shí)現(xiàn)了一個(gè)增強(qiáng)的ARM架構(gòu)v4-MMU,為

2023-08-02 13:05:00

ARM720T是一款通用的32位微處理器,具有8KB的高速緩存、擴(kuò)大的寫入緩沖區(qū)和內(nèi)存管理單元(MMU),組合在一個(gè)芯片中。ARM720T中的CPU是ARM7TDMI。ARM720T是與ARM處理器

2023-08-02 11:36:56

時(shí)執(zhí)行關(guān)鍵異常處理程序。

?每個(gè)指令和數(shù)據(jù)CPU接口的緊密耦合SRAM。指令和數(shù)據(jù)SRAM的大小都是實(shí)現(xiàn)者可配置的。

?指令和數(shù)據(jù)緩存。該設(shè)計(jì)可以很容易地修改,以允許從4K字節(jié)到1M字節(jié)的任何高速緩存組合

2023-08-02 09:41:21

。

Cortex-A720核心在DSU-120 DynamIQ中實(shí)現(xiàn)? 簇它連接到DynamIQ? 共享單元-120,其表現(xiàn)為具有L3高速緩存和窺探控制的完全互連。

這種連接配置也用于具有不同類型內(nèi)核的系統(tǒng)中,其中Cortex-A720核心是性能均衡的核心。

2023-08-02 08:55:50

的ARM高速緩存處理器宏單元,提供完整的虛擬內(nèi)存功能。ARM1020T設(shè)計(jì)用于運(yùn)行復(fù)雜的操作系統(tǒng),如JavaOS、Linux、Microsoft WindowsCE、NetBSD和Symbian

2023-08-02 08:33:42

MBIST是測(cè)試嵌入式存儲(chǔ)器的行業(yè)標(biāo)準(zhǔn)方法。MBIST通過根據(jù)測(cè)試算法執(zhí)行對(duì)存儲(chǔ)器的讀取和寫入序列來工作。存在許多行業(yè)標(biāo)準(zhǔn)的測(cè)試算法。MBIST控制器生成正確的讀取和寫入序列。ARM L210 MBIST控制器用于與ARM L210一起執(zhí)行二級(jí)高速緩存RAM的內(nèi)存測(cè)試。

2023-08-02 08:07:10

內(nèi)核是高效內(nèi)核。

Cortex-A520內(nèi)核在一個(gè)名為complex的塊中實(shí)現(xiàn),該塊最多包含兩個(gè)核心。在雙核復(fù)合體中,矢量處理單元(VPU)、L2翻譯Lookaside緩沖區(qū)(TLB)和L2高速緩存邏輯在核心之間共享。

下圖顯示了雙核配置的示例。

2023-08-02 07:05:57

電子發(fā)燒友網(wǎng)站提供《STM32F7技術(shù)--高速緩存.pdf》資料免費(fèi)下載

2023-08-01 15:18:55 0

0 電子發(fā)燒友網(wǎng)站提供《在Readme文件使用MegaRAID Cachevault選項(xiàng).zip》資料免費(fèi)下載

2023-07-27 16:42:47 0

0 ,用于構(gòu)建新一代信任設(shè)備,例如:便攜式多媒體EFT-POS終端。MAX32590集成了存儲(chǔ)器管理單元(MMU)、32KB指令高速緩存器、16KB數(shù)據(jù)高速緩存、4KB指

2023-07-14 14:33:26

構(gòu)建新一代信任設(shè)備,例如:便攜式多媒體EFT-POS終端。MAX32591集成了存儲(chǔ)器管理單元(MMU)、32KB指令高速緩存器、16KB數(shù)據(jù)高速緩存、4KB指令

2023-07-14 14:09:44

構(gòu)建新一代信任設(shè)備,例如:便攜式多媒體EFT-POS終端。MAX32592集成了存儲(chǔ)器管理單元(MMU)、32KB指令高速緩存器、16KB數(shù)據(jù)高速緩存、4KB指令

2023-07-14 14:04:11

緩存服務(wù)器是什么?緩存服務(wù)器是專用網(wǎng)絡(luò)服務(wù)器或充當(dāng)在本地保存網(wǎng)頁或其他互聯(lián)網(wǎng)內(nèi)容的服務(wù)器的服務(wù)。通過將以前請(qǐng)求的信息放入臨時(shí)存儲(chǔ)(或高速緩存)中,高速緩存服務(wù)器既可以加快數(shù)據(jù)訪問速度,又可以減少

2023-07-07 17:48:59 353

353 Chiplet技術(shù)和NoC技術(shù)目前已經(jīng)成為解決摩爾定律無法延續(xù)的一種重要方法,現(xiàn)在的CPU芯片對(duì)外的接口已經(jīng)不是普通的IO了,而是一套標(biāo)準(zhǔn)的NoC總線接口,可以與專門的NoC總線DIE(暫稱為IO

2023-06-29 09:56:59 519

519

SPI Flash為Slave (從設(shè)備),可將應(yīng)用程序放在外部內(nèi)存SPI Flash,要執(zhí)行放在外部SPI Flash的程序時(shí),硬件會(huì)透過SPI Flash控制單元將應(yīng)用程序讀取至新唐專為M480 SPI Flash 設(shè)計(jì)的32KB高速緩存執(zhí)行應(yīng)用程序。

2023-06-15 07:11:48

本地緩存 :應(yīng)用中的緩存組件,緩存組件和應(yīng)用在同一進(jìn)程中,緩存的讀寫非常快,沒有網(wǎng)絡(luò)開銷。但各應(yīng)用或集群的各節(jié)點(diǎn)都需要維護(hù)自己的單獨(dú)緩存,無法共享緩存。

2023-06-11 15:12:21 556

556

使用 TI SysBIOS,您可以在其中將高速緩存的一部分定義為具有特殊地址的快速 RAM。然后固件可以考慮將代碼或變量放在那里,從而大大加快算法的速度。

我不知道 i.MX8mm 是否一般提供,我也不知道如何在構(gòu)建嵌入式 Linux 時(shí)配置它。

2023-05-18 11:48:08

微機(jī)保護(hù)裝置由硬件和軟件兩部分組成,其中硬件主要包括以下幾個(gè)部分:

1. 微處理器:微機(jī)保護(hù)裝置使用的微處理器通常會(huì)配置為高性能、低功耗、支持多核心、高速緩存的處理器,以保證系統(tǒng)的穩(wěn)定性

2023-04-21 18:12:26 2998

2998 )的縮寫。是 Motorola 公司推出的一種同步串行接口技術(shù),是一種高速的,全雙工,同步的通信總線。SPI 支持以三線同步串行模式進(jìn)行數(shù)據(jù)交互,加上片選線支持硬件切換主從模式,支持以單根數(shù)據(jù)線通訊。

2023-04-17 15:30:56

LSI1013LT1G

2023-03-29 21:39:10

TBU?高速保護(hù)器

2023-03-28 18:13:42

高速DAP仿真器 BURNER

2023-03-28 13:06:20

溝道高速IGBT及場(chǎng)阻技術(shù)

2023-03-28 12:56:28

高速線路的2線ESD保護(hù)

2023-03-24 13:58:22

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論