Si8220,Si8233,Si8234,Si8235 ISOdriver 接口 評估板

2024-03-14 22:30:47

Si5350,Si5351 時鐘發生器 計時 評估板

2024-03-14 22:30:46

Si5344 時鐘乘法器 計時 評估板

2024-03-14 22:30:44

Si5348 時鐘發生器 計時 評估板

2024-03-14 22:30:44

SI5010 時鐘和數據恢復(CDR) 計時 評估板

2024-03-14 22:30:31

Si50122-A5 時鐘發生器 計時 評估板

2024-03-14 22:30:31

SI5013 時鐘和數據恢復(CDR) 計時 評估板

2024-03-14 22:30:31

SI5020 時鐘和數據恢復(CDR) 計時 評估板

2024-03-14 22:30:31

新一代FLIR Si2系列聲學成像儀共有三個型號,Si2-PD——適用于局部放電檢測,Si2-LD——適用于壓縮氣體泄漏和機械故障檢測,Si2-Pro——綜合二者的功能點,均可檢測!

2024-03-13 18:08:18 397

397 電子發燒友網站提供《Si24R03數據手冊.pdf》資料免費下載

2024-03-01 15:44:53 0

0 Si二極管,即硅二極管,是利用硅半導體材料制成的二極管,廣泛應用于各種電子設備中。根據不同的功能和用途,Si二極管可以分為以下幾類: 整流二極管主要用于將交流電(AC)轉換為直流電(DC)。 這類

2024-02-23 11:01:13 146

146

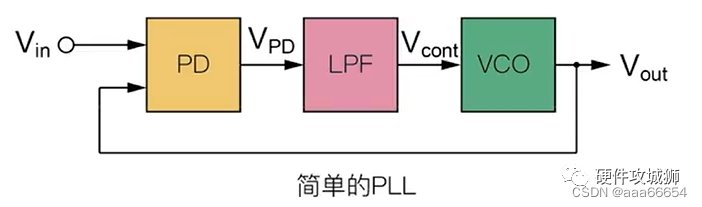

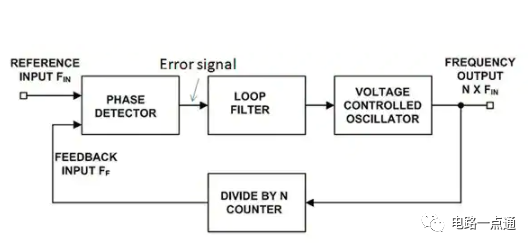

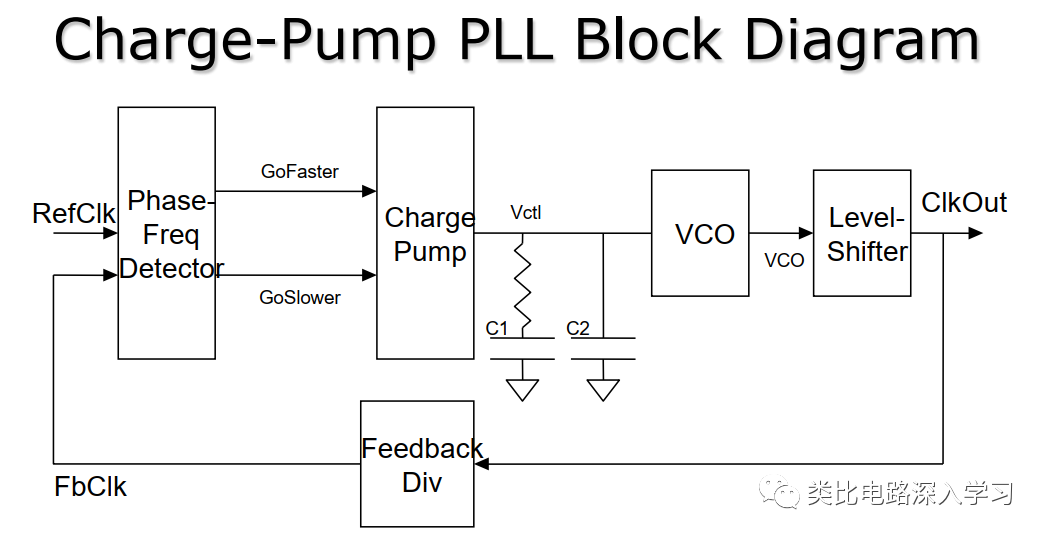

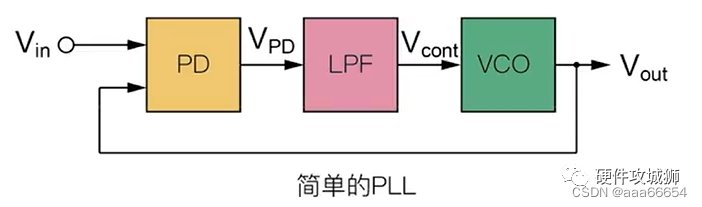

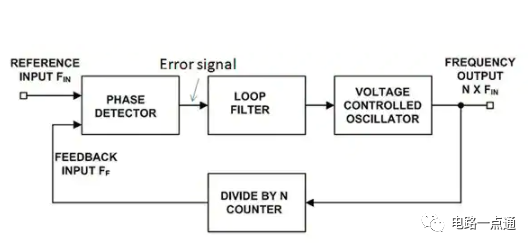

鎖相環 (PLL) 是電子系統中最通用、最靈活和最有價值的電路配置之一,因此在許多應用中都有使用。它用于時鐘重定時和恢復,作為頻率合成器和可調諧振蕩器,僅舉幾個例子。

2024-02-17 14:07:00 161

161

時鐘發生器芯片廠家 時鐘芯片是一種基于PLL的時鐘發生器,采用ADPLL(全數字鎖相環)技術,以實現的高頻低相噪性能,并具備低功耗和高PSNR能力,可實現小于0.3ps RMS的相位抖動性能

2024-02-04 11:41:14

的靈敏度可調,從而實現更長的通信距離,并且適應噪聲環境下工作。Si3933 具有內部時鐘產生器,可選擇使用晶體振蕩器或者 RC 振蕩器。用戶也可以選擇使用外部時鐘。

Si3933 支持可編程的數據速率

2024-01-30 16:10:55

Si512 NFC 前端芯片PN532/PN5121. 介紹?Si512 是一款高度集成的 NFC 前端,支持 13.56MHz 下的多種主動/被動模?式非接觸式通信方法和協議,支持自動載波偵測功能

2024-01-24 13:51:11 0

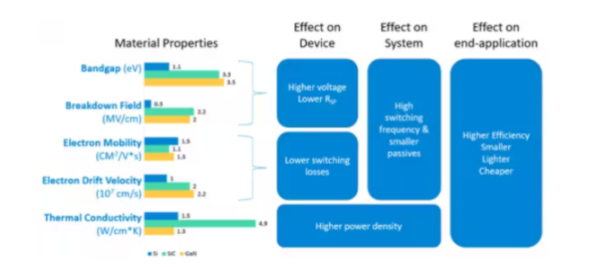

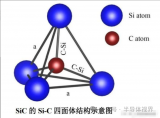

0 SiC是一種Si元素和C元素以1:1比例形成的二元化合物,即百分之五十的硅(Si)和百分之五十的碳(C),其基本結構單元為 Si-C 四面體。

2024-01-18 09:42:01 520

520

14通道自動靈敏度校準低功耗電容觸摸傳感器動能世紀芯片Si314

2024-01-05 14:32:51 0

0 電子發燒友網站提供《SI4606集成電路IC電壓低壓英文資料.pdf》資料免費下載

2023-12-29 11:09:55 0

0 時鐘發生器芯片廠家 時鐘芯片是一種基于PLL的時鐘發生器,采用ADPLL(全數字鎖相環)技術,以實現的高頻低相噪性能,并具備低功耗和高PSNR能力,可實現小于0.3ps RMS的相位抖動性能

2023-12-29 09:29:50

時鐘緩沖器芯片時鐘芯片是一種基于PLL的時鐘發生器,采用ADPLL(全數字鎖相環)技術,以實現的高頻低相噪性能,并具備低功耗和高PSNR能力,可實現小于0.3ps RMS的相位抖動性能。可輸出差分

2023-12-28 13:46:09

如題,目前項目要做一個100m16bit的數據采集卡,看了下貴公司的AD9460,但是差分參考時鐘無法選擇?

需不需要加一個時鐘綜合芯片比如Si5324?但類似的這種芯片市場上很不好買到。

如果用elcosc能否推薦個廠家和芯片?還有ad9460能否申請樣品?謝謝

2023-12-25 07:44:39

高性能20路PCIe時鐘緩沖器新品推介SQ82100PCI-Express(PCIe)是一種高速串行計算機擴展總線標準,主要用于擴充計算機系統總線數據吞吐量以及提高設備通信速度。目前服務器

2023-12-20 08:19:38 240

240

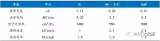

碳化硅(SiC)是一種由硅(Si)和碳(C)組成的半導體化合物,屬于寬帶隙(WBG)材料系列。它的物理結合力非常強,使半導體具有很高的機械、化學和熱穩定性。

2023-12-11 11:29:35 196

196

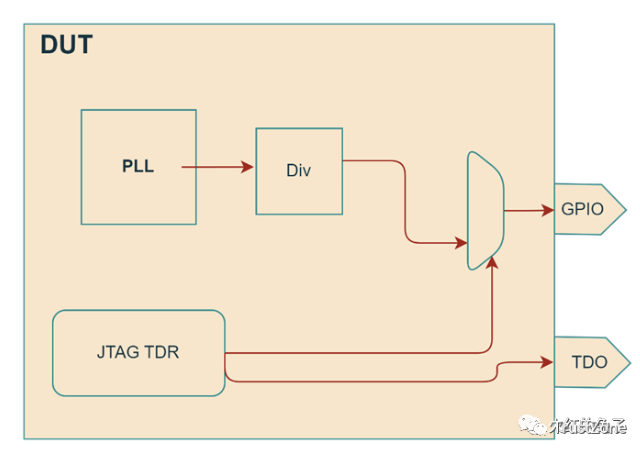

今天想來聊一下芯片設計中的一個重要macro——PLL,全稱Phase lock loop,鎖相環。我主要就介紹一下它是什么以及它是如何工作的。

2023-12-06 15:21:13 386

386 今天想來聊一聊芯片設計中的一個非常基礎的概念——時鐘。對于外行來說聽到這個詞可能會感覺迷茫,猜一個大概意思吧可能也不太準。

2023-12-06 14:41:00 303

303 中的Tick數就是基于模塊時鐘的)。本系列文章就來詳細介紹TC3xx芯片的時鐘系統及其具體配置。本文為TC3xx芯片時鐘系統的鎖相環PLL詳解。

2023-12-01 09:37:22 545

545

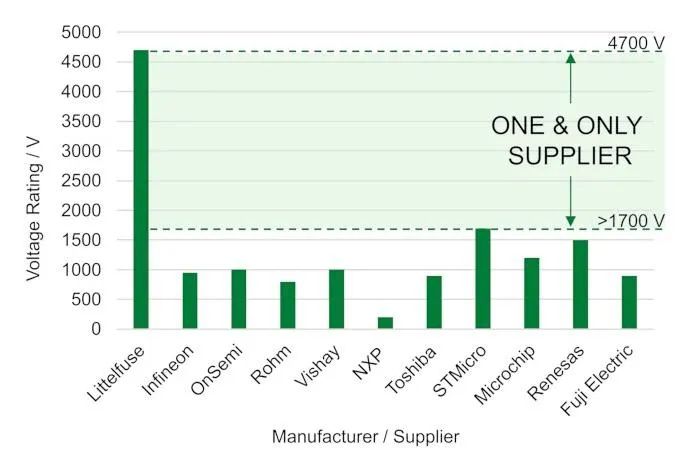

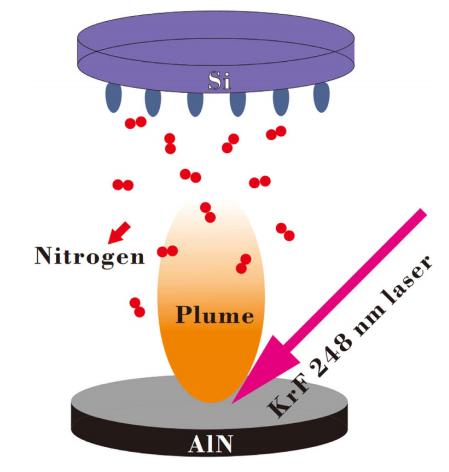

Si對比SiC MOSFET 改變技術—是正確的做法

2023-11-29 16:16:06 149

149

高壓分立Si MOSFET (≥ 2 kV)及其應用

2023-11-24 14:57:39 195

195

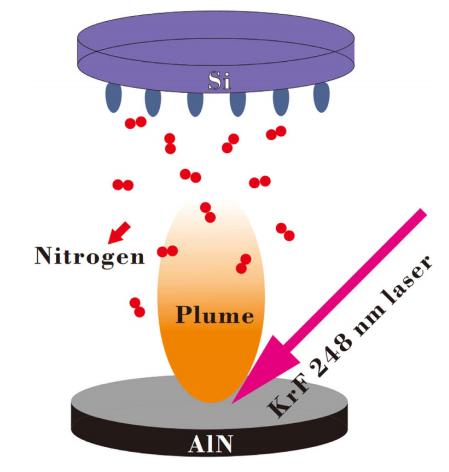

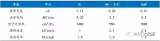

通過有效控制AlN薄膜與Si襯底之間的界面反應,利用脈沖激光沉積(PLD)在Si襯底上生長高質量的AlN外延薄膜。英思特對PLD生長的AlN/Si異質界面的表面形貌、晶體質量和界面性能進行了系統研究。

2023-11-23 15:14:40 232

232

SiC的導熱性大約是Si的三倍,并且將其他特性的所有優點結合在一起。導熱率是指熱量從半導體結傳遞到外部環境的速度。這意味著SiC器件可以在高達200°C的溫度下工作,而Si的典型工作溫度限制為150°C。

2023-11-23 15:08:11 486

486

現想用Cadence做PCB的的SI仿真,但是AD8139沒有IBIS仿真模型,只有SPICE模型,請問利用SPICE模型能不能進行PCB的SI仿真?謝謝

2023-11-22 08:11:44

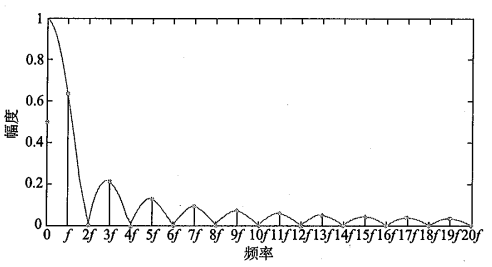

V CO 輸出本地參考頻率。由于V CO 采用模擬電路, 這將帶來元件 飽和、直流漂移、非線性等問題。因此, 全數字鎖相環得到了越來越廣泛的應用。

本文介紹一種 DD S(D irect D igital Syn thesizer) 與 PLL (Phase L ocked L oop ) 技術

2023-11-09 08:31:40 1

1 一、友商的nRF24L01+不要求芯片底部的金屬焊盤接地,Si24R1規格書上也沒要求接地,這是因為發射功率較低只有0dbm的情況,當芯片發射功率大于0dbm以后,芯片底部的金屬焊盤會有很多白噪聲

2023-11-06 10:27:02

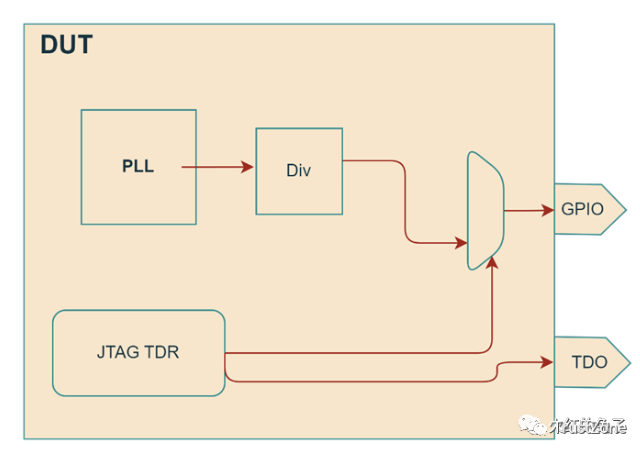

自動測試設備 (ATE)對PLL(鎖相環)進行測試時,我們首先要明白PLL在系統級芯片(SoC)中的重要性。

2023-11-01 15:43:10 683

683

為何不用一根導線代替鎖相環? 鎖相環(PLL)是一種廣泛使用的電路,用于同步和追蹤時鐘和數據信號。它通常由一個鎖相環振蕩器(VCO)、一個相鎖環(PLL)和一個數字控制器(DCO)組成。 PLL

2023-10-31 10:33:15 191

191 DFT PLL向量,ATE怎么用? 自動測試設備(ATE)對PLL(鎖相環)進行測試時,我們首先要明白PLL在系統級芯片(SoC)中的重要性。它是SoC中關鍵的時鐘或信號同步部件,其性能直接影響

2023-10-30 11:44:17 662

662

PLL芯片對電源的要求有哪些? PLL芯片是廣泛應用于電子電路中的一種重要的芯片,它主要用于頻率合成、時鐘信號的處理和數據傳輸等方面。在應用中,PLL芯片對電源的要求非常高,以確保系統的穩定、精度

2023-10-30 10:46:54 510

510 控制多片PLL芯片時,串行控制線是否可以復用? 當需要控制多片PLL芯片時,使用復雜電路來進行控制并非理想方案,因為使用多個電路芯片會導致整個系統變得復雜且難以處理。因此,確定一個適當的解決方案

2023-10-30 10:16:42 149

149 頻繁地開關鎖相環芯片的電源會對鎖相環有何影響? 鎖相環(PLL)是一種被廣泛應用在現代電子技術中的集成電路,它是一種反饋控制系統,可以將輸入信號和本地參考信號同步。鎖相環可用于電子時鐘、數字信號處理

2023-10-30 10:16:40 267

267 Si314是一款具有自動靈敏度校準功能的14通道電容傳感器,其工作電壓范圍為1.8~5.5V。

Si314設置休眠模式來節省功耗,此時,功耗電流為10uA@3.3V。

Si314各個感應通道可實現

2023-10-29 23:38:49

Silicon Labs無線接收器Si4355可以同時支持傳輸速率為2.4/9.6Kbps的數據嗎?

2023-10-28 08:25:24

Silicon Labs時鐘芯片Si5332如何更改時鐘輸出頻率??

2023-10-28 07:28:03

Si1102檢測頻率最高可到多少Hz?

2023-10-27 07:09:26

芯片時鐘不穩定會怎么樣?芯片內部時鐘紊亂的原因? 芯片是電子設備中最重要的組成部分之一,因為它們負責控制電子設備的整個操作,并保證設備的穩定運行。在芯片中,時鐘是一個非常重要的元素,因為它控制整個

2023-10-25 15:07:59 1145

1145 了解鎖相環(PLL)瞬態響應 如何優化鎖相環(PLL)的瞬態響應? 鎖相環(PLL)是一種廣泛應用于數字通信、計算機網絡、無線傳輸等領域的重要電路。PLL主要用于時鐘恢復、頻率合成、時鐘同步等領域

2023-10-23 10:10:20 869

869 鎖相環(PLL)基本原理 當鎖相環無法鎖定時該怎么處理的呢? 鎖相環(Phase Locked Loop, PLL)是一種電路系統,它可以將輸入信號的相位鎖定到參考信號的相位。在鎖相環中,反饋回路

2023-10-23 10:10:15 1352

1352 ;SI5338Q-B-GMSi5338是一款高性能、低抖動的時鐘發生器,能夠在設備的四個輸出驅動器中的每一個上合成任何頻率。這個時間IC能夠更換多達四個不同頻率的

2023-10-17 17:02:33

Altera的FPGA中,只有從專用時鐘管腳(Dedicated clock)進去的信號,才能接片內鎖相環(PLL)嗎?? 在Altera的FPGA中,專用時鐘管腳是經過特殊處理的單獨管腳,其用途

2023-10-13 17:40:00 297

297 siumlink中三相鎖相環PLL的輸入怎么實現? siumlink中三相鎖相環PLL的輸入是通過輸入三相交流電壓來實現的。在交流電力系統中,多數情況下使用的是三相電壓,因此三相鎖相環(PLL

2023-10-13 17:39:56 482

482 什么是鎖相環?PLL和DLL都是鎖相環區別在哪里? 鎖相環(Phase Locked Loop,PLL)是一種基于反饋的控制系統,用于提供穩定的時鐘信號。它可以將參考信號的相位與輸出信號的相位進行

2023-10-13 17:39:53 665

665 時鐘發生器由哪些部分組成?鎖相環pll的特點是什么?如何用硬件配置pll? 時鐘發生器是指通過特定的電路設計產生適合各種電子設備使用的時鐘信號的器件。時鐘發生器由多個部分組成,其中最核心的是鎖相

2023-10-13 17:39:50 443

443 pll鎖相環的作用 pll鎖相環的三種配置模式? PLL鎖相環是現代電子技術中廣泛應用的一種電路,它的作用是將一個特定頻率的輸入信號轉換為固定頻率的輸出信號。PLL鎖相環的三種配置模式分別為

2023-10-13 17:39:48 1098

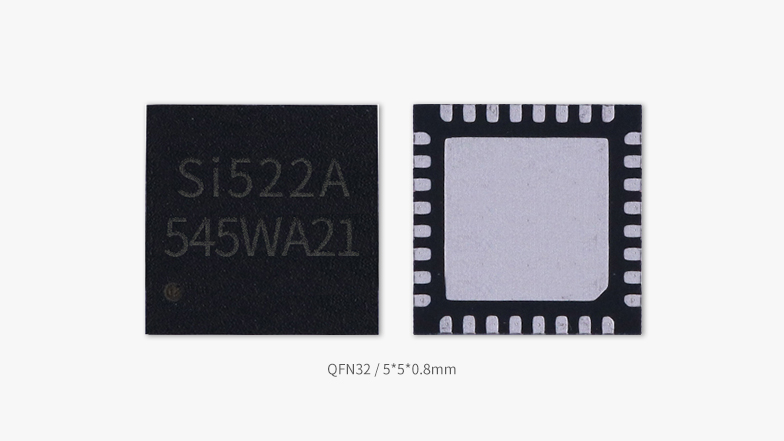

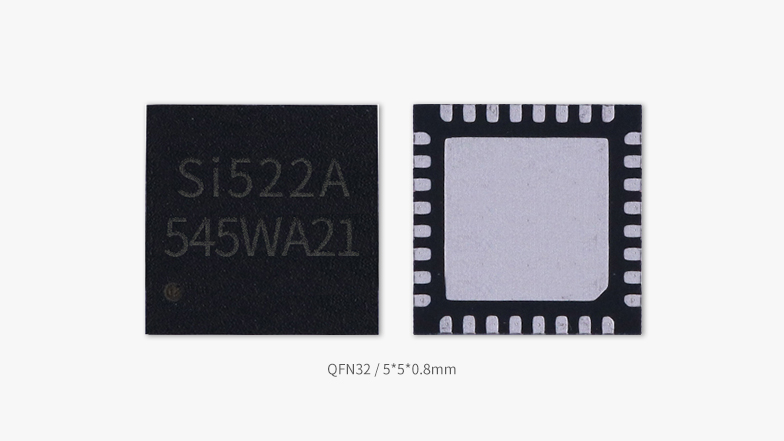

1098 Si522A是一個高度集成的,工作在13.56MHz的非接觸式讀寫器芯片,閱讀器支持ISO/IEC 14443 A/MIFARE,支持自動載波偵測功能(ACD)。 無需外圍其他電路,Si

2023-10-08 17:06:44 287

287

,該模式下功耗低至4.5UA。

相比國產芯片,其他國產芯片雖然也能兼容rc522,但是其整體功耗高于si522,同時有部分國產芯片并沒有加入低功耗自動尋卡功能,產品待機時間遠遠低于si

2023-10-08 09:28:53

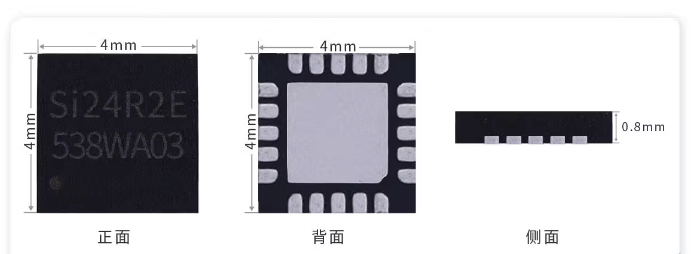

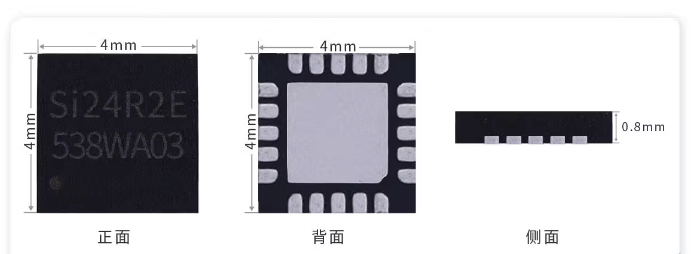

Si24R2E是國內一款針對有源RFID市場設計的低功耗、高性能的2.4GHz標簽系統的SoC單芯片,集成嵌入式2.45GHz無線射頻發射器模塊、128次可編程NVM存儲器模塊以及自動發射控制器模塊等。

2023-09-28 11:19:27 377

377

信號的上升時間越短,信號包含的高頻成分就越多,高頻分量和通道之間的相互作用就越可能導致信號畸變,從而產生SI問題。

2023-09-21 15:13:26 637

637

?Si24R2F+是針對IOT應用領域推出的新款超低功耗2.4G內置NVM單發射芯片。廣泛應用于2.4G有源活體動物耳標,帶實時測溫+計步功能。相較于Si24R2E,Si24R2F+增加了溫度監控

2023-09-05 14:48:00

NRF24L01P芯片兼容通信。從而被打上了國產NRF24L01P的標簽,更有甚者居然磨掉芯片原本的SI24R1的LOGO打成NRF24L01P,給很多客戶產生了很多不必要的損失。大家定向的理解

2023-09-05 14:35:21

景下的時序要求。尤其對于需要高速數據傳輸、信號采集處理等場景的數字信號處理系統而言,FPGA PLL的應用更是至關重要。本文將介紹FPGA鎖相環PLL的基本原理、設計流程、常見問題及解決方法,以及該技術在外圍芯片時鐘提供方面的應用實例。 一、FPGA鎖相環PLL基本原理 1.時鐘頻率的調

2023-09-02 15:12:34 1319

1319 鎖相環PLL和鎖頻環FLL的區別 鎖相環(PLL,Phase Locked Loop)和鎖頻環(FLL,Frequency Locked Loop)是兩種常用于信號調節和數據傳輸的控制回路。雖然它們

2023-09-02 15:06:39 4147

4147 PLL和DLL都是鎖相環,區別在哪里?? PLL和DLL都是常用的鎖相環(Phase Locked Loop)結構,在電路設計中具有廣泛的應用。它們的共同作用是將輸入信號和參考信號的相位差控制在一定

2023-09-02 15:06:31 1522

1522 pll鎖相環倍頻的原理? PLL鎖相環倍頻是一種重要的時鐘信號處理技術,廣泛應用于數字系統、通信系統、計算機等領域,具有高可靠性、高精度、快速跟蹤等優點。PLL鎖相環倍頻的原理涉及到鎖相環,倍頻器

2023-09-02 14:59:24 1503

1503 業界高端FPGA的卓越性能和高口碑聲譽都有哪些因素了?其中很重要的一個因素就是FPGA內部豐富的時鐘資源使得FPGA在處理復雜時鐘結構和時序要求的設計中具有很大優勢。設計師可以更好地控制和管理時鐘信號,提高時序性能、減少時鐘相關問題,并滿足設計的高性能和穩定性要求。

2023-08-31 10:44:01 530

530

I2CON |= STA;

I2CON |= SI;

while ((I2CONSI) != SI);

I2CON= ((~STA)(~SI)); //請問這是i2c清零的動作嗎??但是I2C清零不是要寫

2023-08-24 06:03:19

電子發燒友網站提供《SI Logic Scientific-Linux 5.5驅動程序.zip》資料免費下載

2023-08-11 09:52:53 0

0 電子發燒友網為你提供Maxim(Maxim)SI7661DJ相關產品參數、數據手冊,更有SI7661DJ的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SI7661DJ真值表,SI7661DJ管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-07-12 18:45:05

電子發燒友網為你提供Maxim(Maxim)SI7661CSA+相關產品參數、數據手冊,更有SI7661CSA+的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SI7661CSA+真值表,SI7661CSA+管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-07-10 18:36:26

本實驗活動介紹鎖相環(PLL)。PLL電路有一些重要的應用,例如信號調制/解調(主要是頻率和相位調制)、同步、時鐘和數據恢復,以及倍頻和頻率合成。在這項實驗中,您將建立一個簡單的PLL電路,讓您對PLL操作有基本的了解。

2023-07-10 10:22:24 789

789

鎖相環 (PLL) 是電子系統中最通用、最靈活和最有價值的電路配置之一,因此在許多應用中都有使用。它用于時鐘重定時和恢復,作為頻率合成器和可調諧振蕩器,僅舉幾個例子。因此,在包括無線電接收器和測試

2023-07-10 09:57:19 4206

4206

Si24R1

超低功耗高性能 2.4GHz GFSK 無線收發芯片

Si24R1是一顆工作在2.4GHz ISM頻段,專為低功耗無線場合設計,集成嵌入式ARQ基帶協議引擎的無線收發器芯片。工作頻率

2023-06-27 17:48:23

使用M031來驅動SI4463

2023-06-27 06:49:16

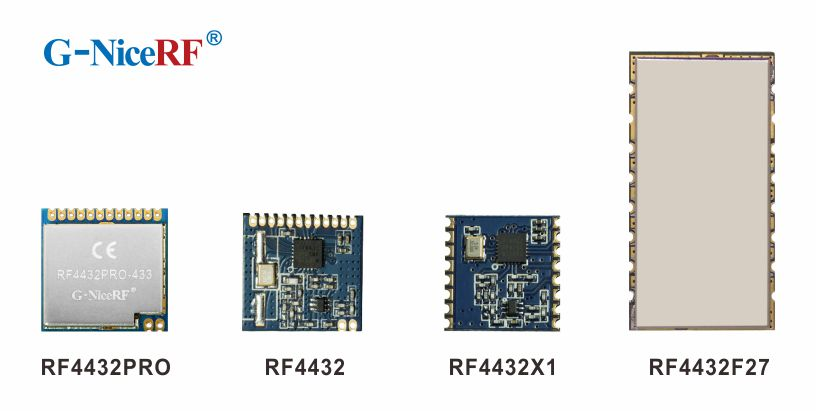

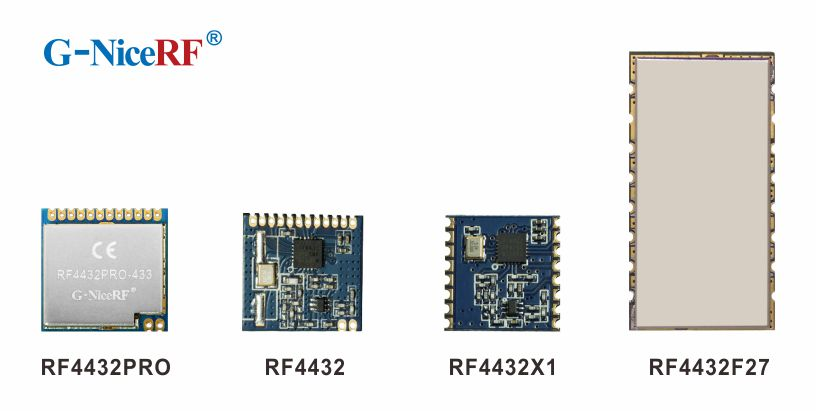

思為無線基于Silicon Lab的Si4432芯片開發出四款不同封裝尺寸的射頻模塊:RF4432PRO、RF4432、RF4432X1和RF4432F27,以便滿足不同客戶的需求。

2023-06-12 16:09:16 301

301

它是RC振蕩器,頻率可以達到8MHZ,可作為系統時鐘和PLL鎖相環的輸入。

2023-06-07 10:28:21 2593

2593

鎖相環(PLL),作為Analog基礎IP、混合信號IP、數字系統必備IP,廣泛存在于各類電子產品中。

2023-06-02 15:25:14 3548

3548

1.基本參數對比 以上圖片是成都億佰特科技有限公司基于SI4463、SI4438和SI4432三款芯片設計的相關產品,上述列表是基于三款產品的測試據。 2.功能簡述 SI4432 : SI

2023-05-31 15:54:43 0

0 Si4432是Silicon labs公司的射頻芯片,是一款高集成度、低功耗、多頻段的EZRadioPRO系列無線收發芯片。其工作電壓為1.9~3.6V,可工作

在315/433/868

2023-05-31 15:27:42 1

1 GaAs的靈敏度比Si材料高1個數量級、溫漂小1個數量級,是優異的線性磁傳感霍爾材料。芯片特征:● 砷化鎵+ Si混合可編程線性霍爾效應IC● 單電源:VDD 3

2023-05-31 10:02:47

PLL(Phase Locked Loop):為鎖相回路或鎖相環,用來統一整合時脈訊號,使內存能正確的存取資料。PLL用于振蕩器中的反饋技術。許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。

2023-05-29 09:51:32 442

442

它是RC振蕩器,頻率可以達到8MHZ,可作為系統時鐘和PLL鎖相環的輸入。

2023-04-28 11:32:00 1734

1734

鎖相環英文名稱PLL(Phase Locked Loop),中文名稱相位鎖栓回路,現在簡單介紹一下鎖相環的工作原理。

2023-04-28 09:57:31 4374

4374

R1LV0816ABG-5SI 7SI 數據表

2023-04-20 18:42:21 0

0 碳化硅(SiC)器件是一種新興的技術,具有傳統硅所缺乏的多種特性。SiC具有比Si更寬的帶隙,允許更高的電壓阻斷,并使其適用于高功率和高電壓應用。此外,SiC還具有比Si更低的熱阻,這意味著它可以更有效地散熱,具有更高的可靠性。

2023-04-13 11:01:16 1468

1468 適用于 S32G 的可用 IBIS 具有歸類為 NC 的所有 RGMII 信號。請與 RGMII 信號共享用于系統級 SI 仿真的 S32G IC 的更新或任何等效 IBIS。此外

2023-04-12 07:00:55

和其他的電子應用中。可以使用PLL產生穩定頻率的時鐘,從高噪聲的通信信道中恢復信號或者在設計中產生各種時鐘信號。鎖相環包括前置分頻模塊(N counter),鑒頻鑒相器(PFD),電荷泵(Charge

2023-04-06 16:04:21

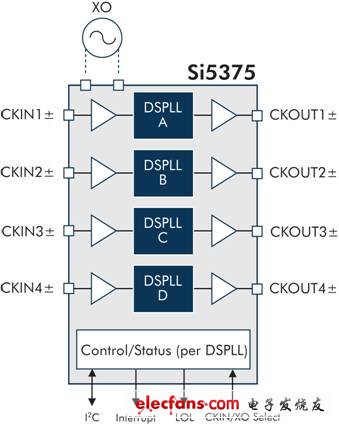

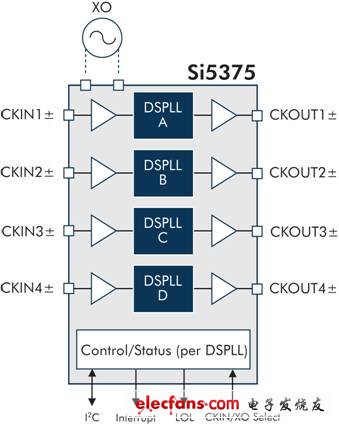

SI5375 - Timing, Clock Buffer / Driver / Receiver / Translator Evaluation Board

2023-03-30 11:42:23

Si8220, Si8233, Si8234, Si8235 - Interface, ISOdriver Evaluation Board

2023-03-29 22:54:44

Si8600, Si8605, Si8621, Si8655, Si8663 - Interface, Digital Isolator Evaluation Board

2023-03-29 22:54:23

Si51210, Si51211, Si51214 - Timing, Clock Generator Evaluation Board

2023-03-29 22:52:08

Si510/511, Si512/513, Si515/516, Si530/531, Si532/533, Si550/552, Si590/591 - Timing, Clock Oscillation Evaluation Board

2023-03-29 22:51:33

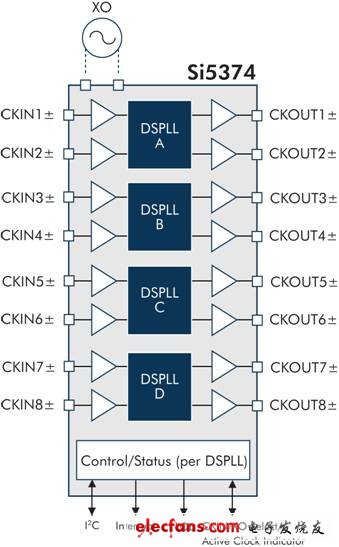

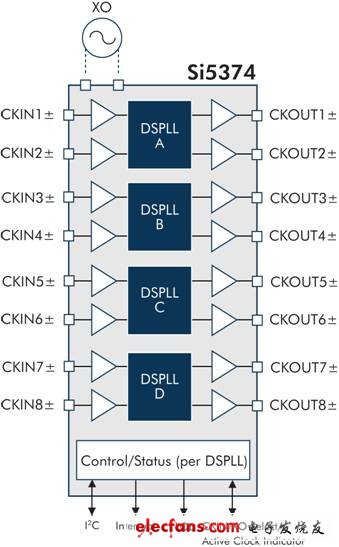

BOARD EVAL FOR SI5374

2023-03-29 22:50:38

SI24R2F+是針對IOT領域,電動車安全、電動車充電樁、冷鏈資產管理、畜牧業動物測溫標簽等市場推出的大功率2.4G射頻芯片,內置NVM可直接配置參數生成軟件。為有源RFID標簽提供在中長

2023-03-29 11:26:46

南京中科微Si24R1是一款通用型低功耗、高性能的2.4GHz無線射頻收發器芯片,專為低功耗無線場合設計,工作頻率范圍為2400MHz-2525MHz,支持2Mbps,1Mbps,250Kbps三種

2023-03-27 14:32:18

時鐘發生器代替。SI393可根據不同的應用場景對接收靈敏度進行調節,在保證接收靈敏度的情況下實現更長距離的通信。同時,自動調諧特性能確保芯片與期望的載波頻率完美匹配,極大簡化了天線調諧器。SI393可根據不同應用場景,通過切換曼徹斯特識別模式來達到方向定位和位置識別。

2023-03-27 11:08:45

高性能、低電流收發器

2023-03-24 14:49:11

電子發燒友App

電子發燒友App

硬聲App

硬聲App

397

397 146

146

161

161

0

0 520

520

240

240

196

196

386

386 303

303 545

545

232

232

486

486

1

1 683

683

191

191 662

662

510

510 149

149 267

267 1145

1145 869

869 1352

1352 297

297 482

482 665

665 443

443 1098

1098 287

287

377

377

1319

1319 4147

4147 1522

1522 1503

1503 530

530 0

0

789

789

4206

4206

301

301

0

0 1

1 442

442

1468

1468

評論