幾乎每個(gè)使用手機(jī)的人都會(huì)有過幾次通話中斷的經(jīng)歷。雖然這些產(chǎn)品以及其他消費(fèi)類產(chǎn)品的系統(tǒng)故障或者小毛病會(huì)帶來不方便,但它們不會(huì)造成災(zāi)難性的后果。然而,醫(yī)療電子設(shè)備的一次系統(tǒng)故障就會(huì)帶來生命威脅,這也是為什么醫(yī)療設(shè)備,以及這些系統(tǒng)中集成的器件和這些器件中運(yùn)行的軟件必須通過嚴(yán)格測試,并符合美國食品藥品監(jiān)督管理局(FDA)的嚴(yán)格要求。

為確保我們的新設(shè)計(jì)能夠發(fā)揮理想可靠的性能,順利通過FDA審批流程,我們采用了一種稱為“Scrum/Sprint開發(fā)流程”的高度結(jié)構(gòu)化的設(shè)計(jì)方法。此外,通過減少在軟件中實(shí)施的功能,還能夠降低軟件出錯(cuò)的幾率。我們已在賽靈思的FPGA中實(shí)施了這些功能。為了能夠更充分地理解這種方法,我們首先來分析一下醫(yī)療設(shè)備的設(shè)計(jì)流程。

三階段生命周期

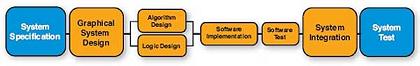

FDA針對醫(yī)療電子產(chǎn)品制定了嚴(yán)格的規(guī)定、要求和指導(dǎo)原則,旨在確保社會(huì)大眾的人身安全。在這些規(guī)定中,F(xiàn)DA對醫(yī)療設(shè)備(圖 1)的生命周期制定了嚴(yán)格的要求。一般情況下,電子產(chǎn)品公司必須在如下方面都符合上述規(guī)定的要求,其中包括醫(yī)療設(shè)備的所有元件、零部件或者配件,醫(yī)療設(shè)備生產(chǎn)過程中采用的任何軟件,以及設(shè)備制造商質(zhì)量系統(tǒng)使用的所有軟件,如可記錄并保持設(shè)備歷史記錄的程序等。

?

圖1、FDA定義的醫(yī)療設(shè)備設(shè)計(jì)整個(gè)生命周期圖.

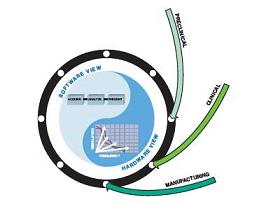

我們可將醫(yī)療設(shè)備整個(gè)生命周期劃分為三個(gè)主要階段。首先是產(chǎn)品整個(gè)生命周期的初期階段(圖2),該階段是所有三個(gè)階段中系統(tǒng)性最差的階段,期間企業(yè)主要側(cè)重于理論與構(gòu)思方面的研究和開發(fā)。該階段的持續(xù)時(shí)長從數(shù)星期到數(shù)年不等,這與企業(yè)準(zhǔn)備開發(fā)的系統(tǒng)的復(fù)雜程度息息相關(guān)。

?

圖2、在產(chǎn)品整個(gè)生命周期的初期階段應(yīng)用虛擬儀器和HEI設(shè)計(jì)方法,可以清晰地理解需要解決的問題。

產(chǎn)品整個(gè)生命周期初期階段的基本組成部分是數(shù)據(jù)采集與分析。通常情況下,研究人員與產(chǎn)品設(shè)計(jì)規(guī)范小組會(huì)使用多種工具來精簡流程。在這個(gè)階段,HEI通常會(huì)采用美國國家儀器(NI)公司的LabVIEW產(chǎn)品來調(diào)整 FPGA的I/O。一旦充分理解問題,我們就能設(shè)計(jì)出解決方案。對于器件開發(fā)及原型設(shè)計(jì),我們結(jié)合直觀的圖形編程,重復(fù)使用數(shù)學(xué)與信號(hào)處理功能來開發(fā)新的算法。然后,通過使用商用套裝硬件,我們對現(xiàn)實(shí)世界的數(shù)據(jù)進(jìn)行參考來對算法的性能進(jìn)行驗(yàn)證。在許多情況下,我們都能使用NI提供的基于FPGA的原型設(shè)計(jì)平臺(tái)來實(shí)現(xiàn)最終器件的實(shí)驗(yàn)原型。確切地說,我們能夠?qū)abVIEWReal-Time模塊和FPGA模塊同NI CompactRIO結(jié)合使用,以便在算法設(shè)計(jì)和器件原型階段之間迅速實(shí)現(xiàn)疊代。使用硬件套件進(jìn)行原型設(shè)計(jì),不僅能夠顯著縮短硬件開發(fā)與集成時(shí)間,而且還使我們能夠?qū)⒏嗑械浇桓豆δ軓?qiáng)大、性能可靠的軟件設(shè)計(jì)中。

?

圖3、軟件設(shè)計(jì)的審核與驗(yàn)證工作通常是在產(chǎn)品整個(gè)生命周期的中期完成。

可將醫(yī)療設(shè)備整個(gè)生命周期的第二階段稱為產(chǎn)品整個(gè)生命周期的中期(參見圖3),能夠充分滿足所設(shè)計(jì)的設(shè)備在產(chǎn)品化、驗(yàn)證、審核以及制造等方面的需求。該階段的重點(diǎn)是制定準(zhǔn)確定義的、清晰載明可量化要求的規(guī)范文檔。這些規(guī)范一經(jīng)定義,即可在規(guī)范文檔與實(shí)際的實(shí)施代碼之間建立明確的映射關(guān)系。

?

圖4、傳統(tǒng)的“瀑布式”開發(fā)流程在進(jìn)入到下一步前需完成每一階段的開發(fā)。

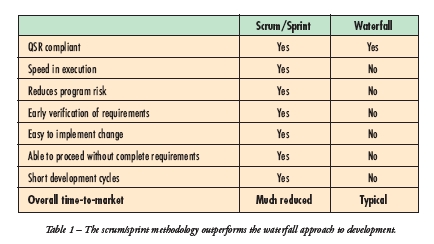

在當(dāng)今錯(cuò)綜復(fù)雜的醫(yī)療設(shè)備市場上,客戶必須加速上市,捷足先登。眾多公司紛紛采用傳統(tǒng)的“瀑布式”開發(fā)法來完成這項(xiàng)工作。“瀑布式”開發(fā)法中的設(shè)計(jì)小組在進(jìn)入下一步前,需要完成設(shè)計(jì)流程的每個(gè)步驟(圖4)。瀑布法高度依賴在項(xiàng)目展開之初就擁有完整準(zhǔn)確的規(guī)范。但是,在醫(yī)療設(shè)備市場,更多的時(shí)候需求會(huì)隨著產(chǎn)品的開發(fā)而不斷發(fā)展變化。這就需要能夠?qū)l(fā)展演進(jìn)也考慮周全的流程。HEI的Scrum/Sprint開發(fā)流程就是可充分解決這一問題的理想方案。

?

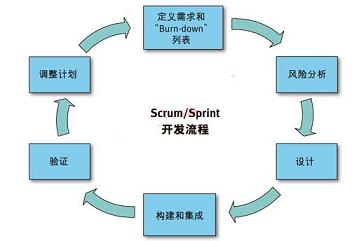

圖5? 在“Scrum/Sprint”流程中,啟動(dòng)項(xiàng)目只需要高級系統(tǒng)架構(gòu)和規(guī)范。

?

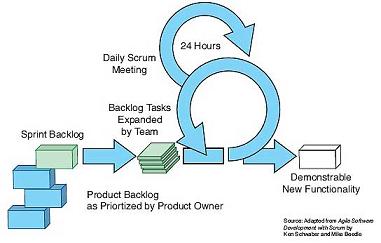

圖6——項(xiàng)目小組為循環(huán)周期中的每個(gè)“Sprint”確定“Sprint待辦事項(xiàng)”工作任務(wù),并對其進(jìn)行擴(kuò)展和分配。然后,項(xiàng)目小組在日常的”Scrum“會(huì)議上評估進(jìn)程,并消除相關(guān)障礙。小組在每個(gè)“Sprint”終止時(shí)向客戶交付產(chǎn)品功能。

在Scrum/Sprint流程中,我們僅要求高級系統(tǒng)架構(gòu)和規(guī)范即可啟動(dòng)項(xiàng)目。我們將項(xiàng)目細(xì)分為4~6個(gè)星期長的“Sprint”。在每個(gè) “Sprint”中,我們可確定我們認(rèn)為流程將會(huì)要求的所有任務(wù),并將其置于“燃盡”列表(burn-down list)中。圖5與圖6顯示了相關(guān)流程圖。HEI在全公司范圍內(nèi)使用Scrum/Sprint開發(fā)流程,不僅將我們的開發(fā)進(jìn)程加快了30%,而且還使我們提前數(shù)月完成了新產(chǎn)品的實(shí)施。表1對瀑布式開發(fā)與Scrum/Sprint開發(fā)方案進(jìn)行了比較。

醫(yī)療設(shè)備開發(fā)的第三階段,也是最后一個(gè)階段,屬于產(chǎn)品整個(gè)生命周期的后期(圖7)。這個(gè)階段要求的工程設(shè)計(jì)工作非常少,不過客戶反饋和市場成功將有助于推動(dòng)新一代產(chǎn)品的概念形成,這樣生命周期又進(jìn)入新的循環(huán)。

?

圖7—產(chǎn)品生命周期后期工作是將產(chǎn)品推向市場,獲取反饋,幫助確定新一代產(chǎn)品的功能。這樣就完成了本周期的工作,并將其帶入新的構(gòu)思階段。

采用Scrum/Sprint產(chǎn)品開發(fā)流程,再結(jié)合使用基于FPGA的套裝硬件以及涵蓋從研發(fā)到制造過程的高級FPGA軟件設(shè)計(jì)工具,HEI就能夠迅速地開發(fā)出未來產(chǎn)品的衍生技術(shù)。我們發(fā)現(xiàn)在眾多情況下都可以使用我們在多種產(chǎn)品開發(fā)中采用的通用內(nèi)核架構(gòu)。例如,可調(diào)整IV與輸液泵的泵控制器架構(gòu),同樣也能用于可控制電機(jī)以實(shí)現(xiàn)輸血管理的其它設(shè)計(jì)項(xiàng)目中。

為何硬件優(yōu)于軟件

為了有效地使用這種方法,并進(jìn)一步加快設(shè)計(jì)流程,就必須改變構(gòu)思設(shè)計(jì)的方式,即從以軟件為中心轉(zhuǎn)變?yōu)楦嗟匾杂布橹行摹U缛藗兯庾R(shí)到的,醫(yī)療設(shè)備的召回在2008年達(dá)到新高,比2007年上升43%。FDA專家認(rèn)為,發(fā)生召回問題的主要原因有兩個(gè):生產(chǎn)中采用的原材料存在缺陷;軟件開發(fā)工作存在問題。企業(yè)對原材料質(zhì)量的管理相對容易一些,不過解決軟件的質(zhì)量問題難度則要大得多。隨著設(shè)備軟件的代碼量迅速增加,問題只會(huì)日益嚴(yán)重。在FDA的消費(fèi)者健康安全部表示醫(yī)療設(shè)備設(shè)計(jì)方要承擔(dān)眾多安全責(zé)任后,這個(gè)問題尤為突出。

在HEI,我們認(rèn)為該問題具有一個(gè)潛在的解決方案,不過不是進(jìn)行更多的測試、代碼檢查和引入更多的流程,相反,我們僅是盡量少編寫軟件,將更多的邏輯交給諸如賽靈思FPGA這樣的硬件元件來執(zhí)行。讓我們來看看發(fā)生軟件故障的常見原因,以及我們將如何使用FPGA來解決這些問題。

消除死鎖

大多數(shù)現(xiàn)代化設(shè)備都需要能夠同時(shí)處理多個(gè)任務(wù),而大多數(shù)嵌入式處理器的處理內(nèi)核仍然只有一個(gè)。這意味著處理器每次只能執(zhí)行一個(gè)指令。同時(shí),并行處理也好不到那里去,因?yàn)樗麄內(nèi)匀槐仨毠蚕碇飨到y(tǒng)CPU。此外,諸如通信驅(qū)動(dòng)器、硬盤和用戶接口元件等其他共享資源也會(huì)引發(fā)死鎖——兩個(gè)或兩個(gè)以上的處理進(jìn)程相互等待對方釋放資源。

由于死鎖狀況經(jīng)常有賴于多個(gè)進(jìn)程,并且通常要求事件在順序上出現(xiàn)同步,因而死鎖非常難以復(fù)制和調(diào)試。僅僅進(jìn)行單元測試很難發(fā)現(xiàn)大多數(shù)死鎖問題。它們往往被代碼檢查人員、熟練的系統(tǒng)測試人員所發(fā)現(xiàn),甚至有時(shí)靠運(yùn)氣發(fā)現(xiàn)。

相比之下,采用FPGA,相互獨(dú)立的進(jìn)程擁有其自己的物理電路系統(tǒng),因而不存在共享資源。在每個(gè)時(shí)鐘信號(hào)報(bào)時(shí)的時(shí)候,組合邏輯不僅在每個(gè)電路中閉鎖,而且還會(huì)在獨(dú)立的寄存器中存儲(chǔ)相關(guān)值。由于進(jìn)程不依賴其他資源,因而也不會(huì)發(fā)生死鎖問題。這樣您就能更多地相信仿真和單元測試的結(jié)果,因?yàn)橹T如資源競爭這樣的未知因素不再是個(gè)問題。

互不兼容的中間件

在開發(fā)嵌入式軟件時(shí),您基本上無需從頭開始編寫每一行代碼。有許多工具都可幫助固件設(shè)計(jì)人員提升工作效率,如簡單的驅(qū)動(dòng)器、網(wǎng)絡(luò)協(xié)議棧、操作系統(tǒng)、乃至代碼生成工具等。雖然這些系統(tǒng)通常都進(jìn)行過全面的獨(dú)立測試,但軟件還是會(huì)存在缺陷。由于工具和庫的組合方式多種多樣,將組件以全新的方式組合在一起使用的可能性非常大。

基于此種原因,F(xiàn)DA要求對在醫(yī)療設(shè)備中使用的所有套裝軟件,企業(yè)必須根據(jù)其具體設(shè)計(jì)的具體使用情況對軟件協(xié)議棧進(jìn)行審驗(yàn)。這是什么意思呢?例如,若我們正在使用包含定點(diǎn)快速傅立葉變換的信號(hào)處理庫,并需要檢測是否存在特定的頻率組分,我們就無需驗(yàn)證對于所有可能的輸入,F(xiàn)FT是否都會(huì)返回正確的值。但是,我們需要驗(yàn)證的是,對于符合規(guī)范的所有有效輸入,F(xiàn)FT能否返回我們期望的值。例如,如果我們只檢測人耳能聽到的音調(diào),就沒有必要測試輸入超過 20KHz以上時(shí)返回的值是否正確。

不過,看上去相互獨(dú)立的軟件組件并不一定如此。因此,如果我們將軟件協(xié)議棧與SPI驅(qū)動(dòng)器結(jié)合起來使用,并配以實(shí)時(shí)操作系統(tǒng)(RTOS),我們就需要對所有這些組件進(jìn)行驗(yàn)證才能對FFT充滿信心。如果FFT將有效輸出傳遞到SPI驅(qū)動(dòng)器,但 SPI驅(qū)動(dòng)器出現(xiàn)系統(tǒng)性故障,那么問題顯然不可避免。然后,如果我們決定調(diào)整SPI驅(qū)動(dòng)器,就需要再次驗(yàn)證整個(gè)軟件協(xié)議棧。這非常麻煩,而且一個(gè)存在故障的組件會(huì)拖累整個(gè)系統(tǒng)的開發(fā)進(jìn)程。基于此原因,在HEI,我們盡可能多地重復(fù)利用經(jīng)檢驗(yàn)具備良好特性的中間件和RTOS驅(qū)動(dòng)器組合。例如,我們可使用NI 單板RIO平臺(tái)上的中間件驅(qū)動(dòng)器。

除了按照每種具體使用情況審驗(yàn)軟件以外,我們還需要審驗(yàn)我們在我們基于FPGA的設(shè)計(jì)中使用的所有第三方知識(shí)產(chǎn)權(quán)(IP)。不過,一旦我們完成我們所有使用情況的審驗(yàn)工作,我們就會(huì)深信不疑:IP在和其它組件集成后,工作情況會(huì)如同預(yù)期一樣。讓我們再來看看我們上面舉的FFT示例。如果我們使用FPGA,我們就可和使用軟件一樣,獲取或者生成FFTIP內(nèi)核,根據(jù)每個(gè)使用情況驗(yàn)證其數(shù)字的正確性。不過,間發(fā)故障的風(fēng)險(xiǎn)可大幅降低,因?yàn)槲覀儾恍枰攒浖橹行牡脑O(shè)計(jì)所需要的所有處理器中間件。這樣,RTOS及SPI驅(qū)動(dòng)器就不再是其自身IP內(nèi)核了,因?yàn)槠涔ぷ鞑粫?huì)直接影響FFT。另外,如果我們調(diào)整SPI驅(qū)動(dòng)器的實(shí)施,我們就不需要對系統(tǒng)未影響的部分再進(jìn)行審驗(yàn)。

緩沖器溢出管理

我們?nèi)绾问褂肍PGA來減少以軟件為中心的系統(tǒng)通常會(huì)產(chǎn)生的錯(cuò)誤的另一個(gè)示例就是緩沖器溢出管理。當(dāng)程序試圖存儲(chǔ)超過為其存儲(chǔ)分配的存儲(chǔ)器末端的數(shù)據(jù)時(shí),程序就會(huì)重復(fù)寫入本不該寫入的某些相鄰數(shù)據(jù),這樣就會(huì)產(chǎn)生緩沖器溢出。這是個(gè)很難察覺的缺陷,因?yàn)樵趯砣魏螘r(shí)候都可訪問被重寫的存儲(chǔ)器,而且這種情況可能會(huì)造成明顯的錯(cuò)誤,也可能不會(huì)。嵌入設(shè)計(jì)中一種比較常見的緩沖器溢出情況是某種高速通信造成的,或許來自網(wǎng)絡(luò)、磁盤或者 A/D轉(zhuǎn)換器。如果通信中斷時(shí)間過長,緩沖器就會(huì)溢出,因此我們需要解決這個(gè)問題來防止各種沖突。

我們可以以兩種方式采用 FPGA來管理緩沖器溢出。在第一種示例中,我們采用FPGA管理循環(huán)傳輸或者雙緩沖傳輸,這樣可卸載實(shí)時(shí)處理器的負(fù)荷。在這種情況下,F(xiàn)PGA可用作協(xié)處理器,降低主處理器的中斷負(fù)載。這是一種通用配置,特別是在高速A/D轉(zhuǎn)換器中。

在第二種示例中,我們將FPGA用作保護(hù)功能的安全保護(hù)層,讓針對病人的I/O在到達(dá)處理器之前,先通過FPGA。在這種情況下,您可以為FPGA增加額外的安全邏輯,這樣在處理器上的軟件崩潰時(shí),您可將所有的輸出置于已知的安全狀態(tài)下。FPGA可發(fā)揮看門狗的作用,其邏輯可以在軟件發(fā)生故障的時(shí)候保證對病人的風(fēng)險(xiǎn)降低到最低程度。通過在架構(gòu)設(shè)計(jì)中將FPGA引入設(shè)備的主信號(hào)鏈,您可以使用這兩種方法中的一種或者兩種來應(yīng)對緩沖器溢出,以便在發(fā)生狀況的時(shí)候能夠更好地處置。

事實(shí)上,越多地將軟、硬件總體系統(tǒng)功能移至FPGA中,就能越快地完成設(shè)計(jì)流程,并最終越快地完成我們的設(shè)計(jì)在客戶最終產(chǎn)品上的驗(yàn)證工作。如果我們能更快地驗(yàn)證我們設(shè)計(jì)方案在總體系統(tǒng)上運(yùn)行的可靠性,那么我們的客戶就能更快地驗(yàn)證整個(gè)最終產(chǎn)品,進(jìn)而將其交付FDA審批。這一過程意味著我們的客戶能夠顯著加速其產(chǎn)品的上市進(jìn)程,改善患者的生活質(zhì)量,甚至拯救生命。

如果我們采用ASIC工藝來實(shí)施設(shè)計(jì),我們需要為代工廠生產(chǎn)出硬件等上好幾個(gè)月。驗(yàn)證ASIC的物理設(shè)計(jì)、創(chuàng)建掩膜并將設(shè)計(jì)投產(chǎn)等額外的步驟會(huì)造成更多出錯(cuò)和出現(xiàn)缺陷的幾率。如果設(shè)計(jì)在任何這些步驟中出現(xiàn)錯(cuò)誤,結(jié)果都會(huì)導(dǎo)致產(chǎn)品上市時(shí)間被大大拖延。由于已生產(chǎn)出FPGA且經(jīng)過全面的測試,因此我們只需關(guān)心我們的設(shè)計(jì)和軟件,并確保設(shè)計(jì)能夠符合客戶的規(guī)范要求。全面結(jié)合 “Scrum/Sprint”方法、以硬件為中心的構(gòu)思、使用高度可靠的工具并在FPGA與ASIC中選擇FPGA,我們便能使客戶實(shí)現(xiàn)差異化,進(jìn)而也能為客戶的客戶,即患者帶來改變。

電子發(fā)燒友App

電子發(fā)燒友App

評論