EDA技術(shù)徹底改變了數(shù)字系統(tǒng)的設(shè)計(jì)方法和實(shí)現(xiàn)手段,借助于硬件描述語(yǔ)言的國(guó)際標(biāo)準(zhǔn)VHDL 和強(qiáng)大的EDA工具,可減少設(shè)計(jì)風(fēng)險(xiǎn)并縮短周期,隨著VHDL語(yǔ)言使用范圍的日益擴(kuò)大

2011-04-11 11:34:47 1842

1842

Xilinx公司XC95系列的XC95144PQ160,實(shí)驗(yàn)使用VHDL為設(shè)計(jì)語(yǔ)言,選用了XilinxISE7.1i作為實(shí)驗(yàn)軟件。2 設(shè)計(jì)實(shí)例——鍵盤接口設(shè)計(jì)下面以鍵盤接口設(shè)計(jì)為例,說(shuō)明EDA技術(shù)在微機(jī)接口技術(shù)

2008-06-25 09:53:51

Xilinx公司XC95系列的XC95144PQ160,實(shí)驗(yàn)使用VHDL為設(shè)計(jì)語(yǔ)言,選用了XilinxISE7.1i作為實(shí)驗(yàn)軟件。2 設(shè)計(jì)實(shí)例——鍵盤接口設(shè)計(jì)下面以鍵盤接口設(shè)計(jì)為例,說(shuō)明EDA技術(shù)在微機(jī)接口技術(shù)

2018-12-04 10:38:40

本帖最后由 xiaomi1991 于 2015-7-20 07:06 編輯

劉欲曉,黃宛寧出的書《EDA技術(shù)與VHDL電路開發(fā)應(yīng)用實(shí)踐》源文件和課后答案

2015-07-20 07:03:46

automation,電子設(shè)計(jì)自動(dòng)化)技術(shù)基于計(jì)算機(jī)輔助設(shè)計(jì),它融合了應(yīng)用電子技術(shù)、計(jì)算機(jī)技術(shù)、信息處理技術(shù)、智能化技術(shù)的最新成果,以實(shí)現(xiàn)電子產(chǎn)品的自動(dòng)設(shè)計(jì)。eda是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,在現(xiàn)代

2013-09-02 15:19:20

的自動(dòng)設(shè)計(jì)。EDA是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。FPGA(Field Programmable Gate Array,現(xiàn)場(chǎng)可編程門陣列)作為可編程邏輯器件的典型代表,它的出現(xiàn)

2008-06-11 10:26:29

設(shè)計(jì)電子系統(tǒng),從電路設(shè)計(jì)、性能分析直到IC版圖或PCB版圖生成的全過(guò)程均可在計(jì)算機(jī)上自動(dòng)完成。 EDA代表了當(dāng)今電子設(shè)計(jì)技術(shù)的最新發(fā)展方向,其基本特征是設(shè)計(jì)人員以計(jì)算機(jī)為工具,按照自頂向下的設(shè)計(jì)方法,對(duì)整個(gè)

2008-06-26 16:16:11

Automation,電子設(shè)計(jì)自動(dòng)化)技術(shù)基于計(jì)算機(jī)輔助設(shè)計(jì),它融合了應(yīng)用電子技術(shù)、計(jì)算機(jī)技術(shù)、信息處理技術(shù)、智能化技術(shù)的最新成果,以實(shí)現(xiàn)電子產(chǎn)品的自動(dòng)設(shè)計(jì)。EDA是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,在現(xiàn)代

2008-06-27 10:26:34

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,F(xiàn)PGA設(shè)計(jì)越來(lái)越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的EDA工具。本文詳細(xì)

2019-06-18 07:33:04

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,F(xiàn)PGA設(shè)計(jì)越來(lái)越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的EDA工具。本文詳細(xì)

2019-06-27 08:01:28

出來(lái)的一整套電子系統(tǒng)設(shè)計(jì)的軟件工具。在利用大規(guī)模可編程邏輯設(shè)計(jì)數(shù)字系統(tǒng)的應(yīng)用中,具體地講EDA技術(shù)就是以計(jì)算機(jī)為工具,在EDA軟件平臺(tái)上,利用硬件描述語(yǔ)言描述設(shè)計(jì)系統(tǒng),然后由EDA工具完成邏輯編譯

2019-02-21 09:41:58

及調(diào)試需要硬件電路的支持,在一定程度上增加了功能修改及系統(tǒng)調(diào)試的困難。因此在設(shè)計(jì)中采用EDA技術(shù)中的VHDL硬件描述語(yǔ)言,以MAX+plusII開發(fā)環(huán)境進(jìn)行綜合仿真,并下載到CPLD可編程邏輯器件中

2008-06-26 10:13:58

需要硬件電路的支持,在一定程度上增加了功能修改及系統(tǒng)調(diào)試的困難。因此在設(shè)計(jì)中采用EDA技術(shù)中的VHDL硬件描述語(yǔ)言,以MAX+plusII開發(fā)環(huán)境進(jìn)行綜合仿真,并下載到CPLD可編程邏輯器件中,完成

2008-06-24 13:47:25

需要硬件電路的支持,在一定程度上增加了功能修改及系統(tǒng)調(diào)試的困難。因此在設(shè)計(jì)中采用EDA技術(shù)中的VHDL硬件描述語(yǔ)言,以MAX+plusII開發(fā)環(huán)境進(jìn)行綜合仿真,并下載到CPLD可編程邏輯器件中,完成

2008-06-12 10:01:04

EDA技術(shù)實(shí)用教程第4版VHDL課件

2013-06-21 18:04:03

EDA技術(shù)是什么?EDA常用軟件有哪些?電子電路設(shè)計(jì)與仿真工具包括哪些呢?

2022-01-24 06:34:54

EDA代表了當(dāng)今電子設(shè)計(jì)技術(shù)的最新發(fā)展方向,它的基本特征是:設(shè)計(jì)人員按照“自頂向下”的設(shè)計(jì)方法,對(duì)整個(gè)系統(tǒng)進(jìn)行方案設(shè)計(jì)和功能劃分,系統(tǒng)的關(guān)鍵電路用一片或幾片專用集成電路(ASIC)實(shí)現(xiàn),然后采用硬件

2019-10-08 14:25:32

EDA技術(shù)的發(fā)展ESDA技術(shù)的基本特征是什么?EDA技術(shù)的基本設(shè)計(jì)方法有哪些?

2021-04-21 07:21:25

VHDL與其他傳統(tǒng)集成電路描述語(yǔ)言相比具有什么優(yōu)勢(shì)?VHDL語(yǔ)言為核心的EDA技術(shù)在醫(yī)學(xué)中的應(yīng)用

2021-05-07 06:38:41

VHDL與電子自動(dòng)化電子設(shè)計(jì)自動(dòng)化(Electronic Design Automation , 簡(jiǎn)稱EDA) 技術(shù)是在70 年代集成電路技術(shù)蓬勃發(fā)展中誕生的, 它的發(fā)展是同集成電路的復(fù)雜度緊密相關(guān)

2009-12-04 10:43:36

VHDL特點(diǎn)是什么VHDL語(yǔ)言在EDA仿真中的應(yīng)用

2021-04-29 06:01:15

eda 2 9個(gè)實(shí)驗(yàn)用VHDL語(yǔ)言

2013-06-18 22:40:54

有哪位大神知道eda里的QUARTURE II軟件下的VHDL語(yǔ)言設(shè)計(jì)能生成電路圖嗎?

2016-05-12 18:35:50

vhdl實(shí)用教程pdf下載本書比較系統(tǒng)地介紹了VHDL的基本語(yǔ)言現(xiàn)象和實(shí)用技術(shù)。全書以實(shí)用和可操作為基點(diǎn),介紹了VHDL基于EDA技術(shù)的理論與實(shí)踐方面的知識(shí)。包括VHDL語(yǔ)句語(yǔ)法基礎(chǔ)知識(shí)(第1章~第

2008-06-04 10:31:29

; 綜上所述,統(tǒng)計(jì)技術(shù)為我們在解決醫(yī)學(xué)研究中的問(wèn)題時(shí)提供了一個(gè)新思路、新方法,而在應(yīng)用統(tǒng)計(jì)技術(shù)時(shí),作為醫(yī)學(xué)工作者,不需要也沒(méi)有必要死記硬背一些繁雜的 數(shù)學(xué)公式和推導(dǎo)過(guò)程。至關(guān)重要的原則有兩個(gè):一是深入理解醫(yī)學(xué)

2009-09-17 14:53:07

[table][tr][td]習(xí)慣了自己發(fā)現(xiàn)一些小問(wèn)題,既然發(fā)現(xiàn)了,就記下來(lái)吧,不然又要忘了,這是多么悲痛的領(lǐng)悟。 今天在用vivado進(jìn)行塊設(shè)計(jì)時(shí)所生成的頂層模塊居然是用VHDL語(yǔ)言描述的,這時(shí)

2018-07-09 01:14:18

VHDL 和其他高級(jí)語(yǔ)言一樣,具有多種數(shù)據(jù)類型。對(duì)大多數(shù)數(shù)據(jù)類型的定義兩者是一致的(例如整數(shù)型),但是也有一些數(shù)據(jù)類型是 VHDL 所獨(dú)有的。表 2-2 所示為 VHDL 支持的數(shù)據(jù)類型和它的數(shù)據(jù)對(duì)象。

2018-09-10 10:09:12

參數(shù)。二、LED在皮膚科醫(yī)學(xué)中的應(yīng)用1.光子嫩膚(photorejuvenation)光子嫩膚技術(shù)被定義為使用連續(xù)的強(qiáng)脈沖光在低能量密度下進(jìn)行非剝脫方式的嫩膚治療。自2000年問(wèn)世以來(lái)短短幾年內(nèi),光子

2012-12-12 17:11:51

:電子技術(shù)設(shè)計(jì)的核心是EDA,目前,EDA技術(shù)的設(shè)計(jì)語(yǔ)言主要有VerilogHDL和VHDL兩種,相對(duì)來(lái)說(shuō)VerilogHDL語(yǔ)言相對(duì)簡(jiǎn)單,上手快,其語(yǔ)法風(fēng)格與C語(yǔ)言類似,據(jù)統(tǒng)計(jì),VerilogHDL

2018-05-04 12:06:12

,在實(shí)際的IC設(shè)計(jì)中作為輔助手段被廣泛采用講了perl語(yǔ)言在IC設(shè)計(jì)中的幾個(gè)應(yīng)用,主要在Verilog代碼擴(kuò)充和仿真測(cè)試等方面,對(duì)IC設(shè)計(jì)人員很有針對(duì)性,讓你能有目的性的學(xué)習(xí)腳本語(yǔ)言,適合入門領(lǐng)會(huì)。perl語(yǔ)言在IC設(shè)計(jì)中的應(yīng)用[hide][/hide]

2012-01-11 15:06:01

)和CAE(計(jì)算機(jī)輔助工程)的概念發(fā)展而來(lái)的。EDA技術(shù)是以計(jì)算機(jī)為工具,根據(jù)硬件描述語(yǔ)言HDL( Hardware Description language)完成的設(shè)計(jì)文件,自動(dòng)地完成邏輯編譯、化簡(jiǎn)

2019-07-30 06:20:05

單片機(jī)在醫(yī)學(xué)信號(hào)檢測(cè)儀中的應(yīng)用1 引 言 傳統(tǒng)的檢測(cè)儀器大多由硬件電路來(lái)完成,不僅功能單一,而且開發(fā)周期長(zhǎng),不易維護(hù)。隨著微電子技術(shù)和信息技術(shù)的高速發(fā)展,醫(yī)學(xué)檢測(cè)儀器正向組合式、多功能、智能化

2009-11-28 10:24:41

(專用集成電路)技術(shù)的不斷完善,EDA(電子設(shè)計(jì)自動(dòng)化)技術(shù)在現(xiàn)代數(shù)字系統(tǒng)和微電子技術(shù)應(yīng)用中顯示出了越來(lái)越重要的作用,而現(xiàn)代EDA技術(shù)的重要特征是采用了硬件描述語(yǔ)言,即VHDL描述。VHDL(Very High

2016-05-08 06:18:34

vhdl中編碼了我的設(shè)計(jì)。我可以使用核心生成器工具為MCB生成vhdl代碼嗎?2)就模擬模型而言,我可以在elpida網(wǎng)站上看到verilog中的模型。有些vhdl仿真模型在哪里?3)我是初學(xué)者,如果有

2019-06-13 06:57:41

(Electronic Design Automation)具有一定的代表性。EDA技術(shù)是一種基于芯片的現(xiàn)代電子系統(tǒng)設(shè)計(jì)方法。它的優(yōu)勢(shì)主要集中在能用HDL語(yǔ)言進(jìn)行輸入、進(jìn)行PEn(可編程器件)的設(shè)計(jì)與仿真等系統(tǒng)

2019-10-08 08:02:17

),在數(shù)字系統(tǒng)設(shè)計(jì)和控制電路中越來(lái)越受到重視。介紹了這種電路的基本結(jié)構(gòu)、性能特點(diǎn)、應(yīng)用領(lǐng)域及使用中的注意事項(xiàng)。對(duì)基于EDA技術(shù)的FPGA進(jìn)行了展望。指出EDA技術(shù)將是未來(lái)電子產(chǎn)品設(shè)計(jì)技術(shù)發(fā)展的主要方向。

2019-09-03 06:17:15

設(shè)計(jì)重用中的關(guān)鍵技術(shù)。如何保證IP核的高測(cè)試覆蓋率,如何保證IP核在集成到SoC中后的可測(cè)試性.是該階段分析的主要目標(biāo)。所以在IP核實(shí)現(xiàn)之前.要檢查IP核設(shè)計(jì)中是否違反了可測(cè)性設(shè)計(jì)規(guī)則; 低功耗分析

2021-09-01 19:32:45

成為描述、驗(yàn)證和設(shè)計(jì)數(shù)字系統(tǒng)中最重要的標(biāo)準(zhǔn)語(yǔ)言之一。由于VHDL在語(yǔ)法和風(fēng)格上類似于高級(jí)編程語(yǔ)言,可讀性好,描述能力強(qiáng),設(shè)計(jì)方法靈活,可移植性強(qiáng),因此它已成為廣大EDA工程師的首選。目前,使用VHDL

2019-06-18 07:45:03

大神分享哈! EDA微波爐VHDL程序 感謝!,課程需要。

2017-06-21 17:19:35

(PLD)的發(fā)展而發(fā)展起來(lái)的。它是一種面向設(shè)計(jì)、多層次的硬件描述語(yǔ)言,是集行為描述、RTL描述、門級(jí)描述功能為一體的語(yǔ)言,并已成為描述、驗(yàn)證和設(shè)計(jì)數(shù)字系統(tǒng)中最重要的標(biāo)準(zhǔn)語(yǔ)言之一。由于VHDL在語(yǔ)法和風(fēng)格上類似于高級(jí)編程語(yǔ)言,可讀性好,描述能力強(qiáng),設(shè)計(jì)方法靈活,可移植性強(qiáng),因此它已成為廣大EDA工程師的首選。

2019-08-28 08:05:46

在語(yǔ)法和風(fēng)格上類似于高級(jí)編程語(yǔ)言,可讀性好,描述能力強(qiáng),設(shè)計(jì)方法靈活,可移植性強(qiáng),因此它已成為廣大EDA工程師的首選。目前,使用VHDL語(yǔ)言進(jìn)行CPLD/FPGA設(shè)計(jì)開發(fā),Altera和Lattice

2019-08-08 07:08:00

`本書比較系統(tǒng)地介紹了VHDL的基本語(yǔ)言現(xiàn)象和實(shí)用技術(shù) 全書以實(shí)用和可操作為基點(diǎn) 簡(jiǎn)潔而又不失完整地介紹了 VHDL基于 EDA技術(shù)的理論與實(shí)踐方面的知識(shí)其中包括VHDL語(yǔ)句語(yǔ)法基礎(chǔ)知識(shí) 第1章 第

2012-02-27 13:52:50

,微電子技術(shù)的發(fā)展密切相關(guān),它吸收了計(jì)算機(jī)科學(xué)領(lǐng)域的大多數(shù)最新研究成果,以高性能的計(jì)算機(jī)作為工作平臺(tái),促進(jìn)了工程發(fā)展。EDA的一個(gè)重要特征就是使用硬件描述語(yǔ)言(HDL)來(lái)完成的設(shè)計(jì)文件,VHDL語(yǔ)言是經(jīng)IEEE

2021-07-29 09:24:20

VHDL硬件描述語(yǔ)言教學(xué):包括fpga講義,VHDL硬件描述語(yǔ)言基礎(chǔ),VHDL語(yǔ)言的層次化設(shè)計(jì)的教學(xué)幻燈片

2006-03-27 23:46:49 93

93 第1章 緒論 1.1 關(guān)于EDA 1.2 關(guān)于VHDL 1.3 關(guān)于自頂向下的系統(tǒng)設(shè)計(jì)方法 1.4 關(guān)于應(yīng)用 VHDL的 EDA過(guò)程 1.5 關(guān)于在系統(tǒng)編程技術(shù) 1.6 關(guān)于FPGA/CPLD的優(yōu)勢(shì) 1.7

2008-06-04 10:24:06 1679

1679

VHDL的定義和功能VHDL的發(fā)展概況程序編程語(yǔ)言和硬件描述語(yǔ)言的對(duì)比引入硬件描述語(yǔ)言對(duì)系統(tǒng)進(jìn)

2008-09-03 12:58:41 39

39 摘要:在簡(jiǎn)要介紹了EDA技術(shù)特點(diǎn)的基礎(chǔ)—L,用EDA技術(shù)作為開發(fā)手段,實(shí)現(xiàn)一個(gè)數(shù)字系統(tǒng)的設(shè)計(jì)。系統(tǒng)采用了頂層圖形設(shè)計(jì)思想,基于硬件描述語(yǔ)言AI扔L,以可編程器件為核心,具

2008-11-18 11:01:29 98

98 VHDL語(yǔ)言及其應(yīng)用是在作者歷時(shí)七年為通信與信息系統(tǒng)、信號(hào)與信息處理專業(yè)研究生講授VHDL語(yǔ)言及其應(yīng)用課程的教學(xué)實(shí)踐基礎(chǔ)上編寫而成的。全書共分15章,以教授完整的VHDL語(yǔ)言體

2009-02-12 09:41:38 172

172 EDA/VHDL講座主要內(nèi)容一、EDA、EDA技術(shù)及其應(yīng)用與發(fā)展二、硬件描述語(yǔ)言三、FPGA和CPLD四、EDA工具軟件五、電子設(shè)計(jì)競(jìng)賽幾個(gè)實(shí)際問(wèn)題的討論六、VHDL語(yǔ)言初步七

2009-03-08 10:54:10 39

39 VHDL語(yǔ)言及其應(yīng)用是在作者歷時(shí)七年為通信與信息系統(tǒng)、信號(hào)與信息處理專業(yè)研究生講授VHDL語(yǔ)言及其應(yīng)用課程的教學(xué)實(shí)踐基礎(chǔ)上編寫而成的。全書共分15章,以教授完整的VHDL語(yǔ)言體

2009-07-10 17:21:44 18

18 VHDL語(yǔ)言及其應(yīng)用的主要內(nèi)容:第一章 硬件模型概述第二章 基本的VHDL編程語(yǔ)言第三章 VHDL模型的組織第四章 VHDL綜合工具第五章 VHDL應(yīng)用樣例附錄A VHDL

2009-07-20 12:06:15 0

0 VHDL語(yǔ)言概述:本章主要內(nèi)容:硬件描述語(yǔ)言(HDL)VHDL語(yǔ)言的特點(diǎn)VHDL語(yǔ)言的開發(fā)流程

1.1 1.1 硬件描述語(yǔ)言( 硬件描述語(yǔ)言(HDL HDL)H

2009-08-09 23:13:20 47

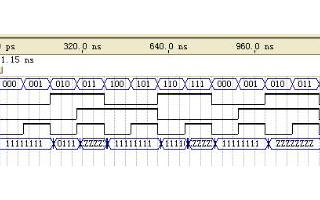

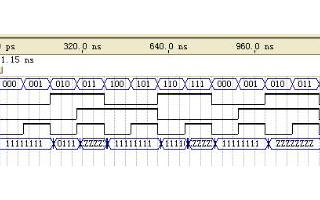

47 討論了 VHDL 語(yǔ)言在 EDA 中的諸多優(yōu)點(diǎn),結(jié)合定時(shí)/計(jì)數(shù)接口芯片的開發(fā)實(shí)例,討論了ISP技術(shù)在電子設(shè)計(jì)自動(dòng)化中的應(yīng)用。同時(shí)給出了實(shí)例的具體例程和時(shí)序仿真波形。在計(jì)算機(jī)控制

2009-08-11 08:20:14 20

20 VHDL語(yǔ)言描述數(shù)字系統(tǒng):本章介紹用 VHDL 描述硬件電路的一些基本手段和基本方法。 VHDL 語(yǔ)言是美國(guó)國(guó)防部在 20 世紀(jì) 80 年代初為實(shí)現(xiàn)其高速集成電路計(jì)劃(VHSIC)而提出的

2009-09-01 09:02:40 37

37 結(jié)合應(yīng)用MaxplusⅡ軟件進(jìn)行VHDL 語(yǔ)言代碼編寫的經(jīng)驗(yàn),闡述使用VHDL 語(yǔ)言的過(guò)程中比較常見的幾個(gè)問(wèn)題。

2009-09-10 16:19:24 25

25 VHDL 語(yǔ)言程序的元素:本章主要內(nèi)容:VHDL語(yǔ)言的對(duì)象VHDL語(yǔ)言的數(shù)據(jù)類型VHDL語(yǔ)言的運(yùn)算符VHDL語(yǔ)言的標(biāo)識(shí)符VHDL語(yǔ)言的詞法單元

2009-09-28 14:32:21 41

41 vhdl數(shù)字系統(tǒng)設(shè)計(jì)是數(shù)字電路自動(dòng)化設(shè)計(jì)(EDA)入門的工具書。其內(nèi)容主要包括:用VHDL語(yǔ)言設(shè)計(jì)的基本組合電路、時(shí)序電路、數(shù)字綜合電路、電路圖輸入法要領(lǐng)概述、實(shí)用VHDL語(yǔ)句

2009-10-08 21:54:01 0

0 EDA技術(shù)培訓(xùn)與VHDL之實(shí)用電路模塊設(shè)計(jì)

2009-12-05 16:31:14 95

95 數(shù)字電池EDA入門之VHDL程序?qū)崿F(xiàn)集

2009-12-07 14:14:57 0

0 EDA技術(shù)及應(yīng)用教學(xué)課件:第1章 緒論 第2章 大規(guī)模可編程邏輯器件 第3章 VHDL編程基礎(chǔ) 第4章 常用EDA工具軟件操作指南 第5章 EDA實(shí)驗(yàn)開發(fā)系統(tǒng) 第6章

2009-12-08 16:25:20 0

0 五個(gè)ARM處理器核心verilog/VHDL源代碼

有幾中編程語(yǔ)言。.net.vbh...

2010-02-09 11:32:13 138

138 EDA技術(shù)復(fù)習(xí)精華

VHDL部分EDA:電子設(shè)計(jì)自動(dòng)化(Electronic Design Automation)EDA技術(shù)包含4個(gè)基本條件:1.大規(guī)

2010-02-23 16:40:23 0

0 本文介紹一種利用 EDA技術(shù) 和VHDL 語(yǔ)言 ,在MAX+PLUSⅡ環(huán)境下,設(shè)計(jì)了一種新型的智能密碼鎖。它體積小、功耗低、價(jià)格便宜、安全可靠,維護(hù)和升級(jí)都十分方便,具有較好的應(yīng)用前景。

2010-08-03 16:51:43 0

0 實(shí)驗(yàn)八、VHDL語(yǔ)言的組合電路設(shè)計(jì)一? 實(shí)驗(yàn)?zāi)康?掌握VHDL語(yǔ)言的基本結(jié)構(gòu)及設(shè)計(jì)的輸入方法。2掌握VHDL語(yǔ)言的組合電路設(shè)計(jì)方法。二? 實(shí)驗(yàn)設(shè)備與儀器

2009-03-13 19:26:58 2368

2368 【摘 要】 通過(guò)設(shè)計(jì)實(shí)例詳細(xì)介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語(yǔ)言開發(fā)FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語(yǔ)言相比,使用VHDL語(yǔ)言的優(yōu)越性。

2009-05-10 19:47:30 1111

1111

基于VHDL語(yǔ)言的智能撥號(hào)報(bào)警器的設(shè)計(jì)

介紹了以EDA技術(shù)作為開發(fā)手段的智能撥號(hào)報(bào)警系統(tǒng)的實(shí)現(xiàn)。本系統(tǒng)基于VHDL語(yǔ)言,采用FPGA作為控制核心,實(shí)現(xiàn)了遠(yuǎn)程防盜報(bào)警。該

2009-10-12 19:08:43 1167

1167

本書比較系統(tǒng)地介紹了VHDL 的基本語(yǔ)言現(xiàn)象和實(shí)用技術(shù)全書以實(shí)用和可操作 為基點(diǎn)簡(jiǎn)潔而又不失完整地介紹了VHDL 基于EDA 技術(shù)的理論與實(shí)踐方面的知識(shí) 其中包括VHDL 語(yǔ)句語(yǔ)法基礎(chǔ)知識(shí)第1 章第7 章邏輯綜合與編程技術(shù)第9 章 有限狀態(tài)機(jī)及其設(shè)計(jì)第10 章基于FPGA

2011-03-03 15:47:13 0

0 摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,F(xiàn)PGA設(shè)計(jì)越來(lái)越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的E

2011-05-27 10:50:58 2731

2731 介紹了EDA(電子設(shè)計(jì)自動(dòng)化)技術(shù)的發(fā)展過(guò)程和基本特征,然后以EDA技術(shù)作為開發(fā)手段,基于硬件描述語(yǔ)言VHDL,以可編程邏輯器件CPLD為核心,實(shí)現(xiàn)了一個(gè)數(shù)字系統(tǒng)的設(shè)計(jì)。

2012-02-16 16:21:03 33

33 第1章-EDA設(shè)計(jì)導(dǎo)論 第2章-可編程邏輯器件設(shè)計(jì)方法 第3章-VHDL語(yǔ)言基礎(chǔ) 第4章-數(shù)字邏輯單元設(shè)計(jì) 第5章-VHDL高級(jí)設(shè)計(jì)技術(shù) 第6章-基于HDL和原理圖的設(shè)計(jì)輸入 第7章-設(shè)計(jì)綜合和行為仿真 第8章

2012-09-18 11:35:36 550

550 第1章 數(shù)字系統(tǒng)EDA設(shè)計(jì)概論 第2章 可編程邏輯器件設(shè)計(jì)方法 第3章 VHDL語(yǔ)言基礎(chǔ) 第4章 數(shù)字邏輯單元設(shè)計(jì) 第5章 數(shù)字系統(tǒng)高級(jí)設(shè)計(jì)技術(shù)(*) 第6章 基于HDL設(shè)計(jì)輸入 第7章 基于原理圖設(shè)計(jì)輸

2012-09-18 13:38:46 163

163 本文介紹一種利用 EDA 技術(shù) 和 VHDL 語(yǔ)言 ,在 MAX+PLUSⅡ環(huán)境下,設(shè)計(jì)了一種新型的智能密碼鎖。它體積小、功耗低、價(jià)格便宜、安全可靠,維護(hù)和升級(jí)都十分方便,具有較好的應(yīng)用前景。

2013-01-10 14:40:03 2246

2246 電子發(fā)燒友網(wǎng)站提供《VHDl實(shí)用教程(潘松_王國(guó)棟編著)_EDA技術(shù)叢書.txt》資料免費(fèi)下載

2015-03-11 11:46:57 0

0 VHDL語(yǔ)言(修改)有需要的朋友下來(lái)看看

2016-08-05 17:32:53 24

24 VHDL語(yǔ)言編程學(xué)習(xí)之VHDL硬件描述語(yǔ)言

2016-09-01 15:27:27 0

0 硬件描述語(yǔ)言VHDL的學(xué)習(xí)文檔,詳細(xì)的介紹了VHDL

2016-09-02 17:00:53 12

12 VHDL語(yǔ)言要素,大學(xué)EDA課程必備資料,在實(shí)際的應(yīng)用中,VHDL仿真器講INTEGER類型的數(shù)據(jù)作為有符號(hào)數(shù)處理,而綜合器將INTEGER作為無(wú)符號(hào)數(shù)處理. VHDL綜合器要求利用RANGE子句

2016-11-21 15:40:34 0

0 VHDL入門--EDA資料,大學(xué)EDA課程必備資料,感興趣的小伙伴們可以瞧一瞧。

2016-11-21 15:40:34 0

0 到一塊集成電路中是現(xiàn)在數(shù)字電子技術(shù)教學(xué)的重要內(nèi)容。 要讓同學(xué)學(xué)會(huì)VHDL,教師首先應(yīng)該自己先學(xué)會(huì),但是學(xué)習(xí)VHDL語(yǔ)言需要能提供文件輸入,邏輯綜合、編譯和仿真的語(yǔ)言環(huán)境,現(xiàn)在向各位推薦一個(gè)語(yǔ)言環(huán)境ALTERA公司的Max+plusⅡ軟件,該軟件可以以圖形方式、文

2017-12-05 09:00:31 20

20 在世界范圍內(nèi),關(guān)于VHDL在多個(gè)領(lǐng)域尤其在芯片,系統(tǒng)設(shè)計(jì)方面的應(yīng)用研究已經(jīng)取得眾多矚目成果。而將VHDL與醫(yī)學(xué)相結(jié)合,勢(shì)必成為電子自動(dòng)化設(shè)計(jì)(EDA)一個(gè)全新的研究方向,本文主要研究將EDA通過(guò)VHDL應(yīng)用于醫(yī)學(xué),以對(duì)脈搏的測(cè)量為例,以實(shí)現(xiàn)數(shù)字系統(tǒng)對(duì)人體多種生理活動(dòng)及生理反應(yīng)的直觀精確測(cè)量。

2018-05-23 11:17:00 1729

1729

VHDL語(yǔ)言是一種在EDA設(shè)計(jì)中廣泛流行的硬件描述語(yǔ)言,主要用于描述數(shù)字系統(tǒng)的結(jié)構(gòu)、行為、功能和接口。除了含有許多具有硬件特征的語(yǔ)句外,VHDL語(yǔ)言的句法、語(yǔ)言形式和描述風(fēng)格十分類似于一般的計(jì)算機(jī)高級(jí)語(yǔ)言,是目前硬件描述語(yǔ)言中應(yīng)用最為廣泛的一種。

2018-03-30 16:04:27 21

21 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之使用VHDL進(jìn)行電子設(shè)計(jì)所需的所有資料包括了:VHDL設(shè)計(jì)基礎(chǔ)知識(shí),VHDL并行語(yǔ)句,VHDL程序?qū)嶓w,VHDL入門,VHDL語(yǔ)言要素,EDA設(shè)計(jì)流程及其工具,IA64 應(yīng)用程序寄存器,LCD液晶顯示漢字字符集表,OCMJ 系列液晶顯示器控制命令集表等

2018-09-25 08:00:00 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之VHDL語(yǔ)言元素的詳細(xì)資料概述一內(nèi)容包括了:1. VHDL語(yǔ)言的客體2 VHDL語(yǔ)言的數(shù)據(jù)類型3 VHDL數(shù)據(jù)類型轉(zhuǎn)換4 VHDL詞法規(guī)則與標(biāo)識(shí)符

2018-11-05 08:00:00 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是EDA教程之VHDL語(yǔ)法補(bǔ)充說(shuō)明詳細(xì)資料說(shuō)明主要內(nèi)容是:1、VHDL庫(kù) 2、子程序調(diào)用 3、VHDL編程的結(jié)構(gòu) 4、 VHDL文字規(guī)則 5、數(shù)據(jù)類型 6、基本語(yǔ)句

2018-11-09 08:00:00 0

0 VHDL是一種用來(lái)描述數(shù)字邏輯系統(tǒng)的“編程語(yǔ)言”。它通過(guò)對(duì)硬件行為的直接描述來(lái)實(shí)現(xiàn)對(duì)硬件的物理實(shí)現(xiàn),代表了當(dāng)今硬件設(shè)計(jì)的發(fā)展方向。VHDL是為了滿足邏輯設(shè)計(jì)過(guò)程中的各種需求而設(shè)計(jì)的。

2020-04-23 15:51:03 2362

2362

什么是vhdl語(yǔ)言 VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述語(yǔ)言)。VHSIC是Very High Speed

2020-04-23 15:58:49 10243

10243 EDA技術(shù)的核心并不是仿真,仿真只是EDA技術(shù)的一個(gè)重要環(huán)節(jié)。EDA技術(shù)的核心是利用計(jì)算機(jī)輔助設(shè)計(jì)(CAD)工具,將電路設(shè)計(jì)自動(dòng)化,實(shí)現(xiàn)從電路設(shè)計(jì)到制造的全流程自動(dòng)化。仿真只是在這一流程中的重要一環(huán),用于驗(yàn)證設(shè)計(jì)的正確性、可靠性和穩(wěn)定性等方面。

2023-04-24 18:22:15 1876

1876 EDA技術(shù)和VHDL是緊密相連的。在EDA設(shè)計(jì)中,VHDL通常用于描述數(shù)字電路的功能和行為,并通過(guò)邏輯分析器、仿真器等工具進(jìn)行仿真、分析和驗(yàn)證。EDA技術(shù)則提供通用的集成設(shè)計(jì)平臺(tái)和工具來(lái)支持VHDL的設(shè)計(jì)、仿真、綜合和布局等流程。

2023-08-09 12:41:00 1105

1105

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論