在單片機的學習中,不光是單片機程序的編寫,還有電路的設計。有些公司可能會把單片機開發分成兩塊:電路設計、程序設計。然后負責電路設計的人只負責電路設計,不用考慮單片機編程;程序設計的人只管單片機編程,不設計電路。

不過我個人認為,只搞電路設計的人可以不用關心單片機是怎么編程的,但是搞單片機程序設計的人,卻必須要對電路很熟悉,你可以不用親自設計電路,但是必須對單片機項目中各種電路的原理足夠了解,這樣才能確保設計出來的程序穩定、健壯。

舉個例子來說吧,假如一個單片機系統中用到了EEPROM存儲芯片,EEPROM芯片的SCL和SDA是開漏輸出的,需要外接上拉電阻,假設電路板上的EEPROM芯片的SCL和SDA的上拉電阻忘記焊上或者壞掉了,這時候調試EEPROM是調不通的,如果這時候電路設計人員不在,而單片機程序設計人員又對EEPROM的原理不熟悉,就會陷入到麻煩中:因為對電路不熟悉,就會一遍一遍的查找程序的原因。可是程序明明沒有問題啊,這個程序在別的項目中一直都是正常的,為什么在這個板子上就不行了呢?

還有一點,一般帶有微控制器的電路板,電路功能是否正常,是需要編寫一定的驗證程序來測試電路板的性能的,單靠電路設計人員使用萬用表、示波器等工具是無法驗證電路的好壞的。

綜上所述,單片機程序設計人員一定要對電路的原理熟悉,這樣才能設計出正確的程序。

從本篇文章開始,我們就來簡單學習一下單片機開發中常用的電路。

當然,由于本人水平有限,關于這些電路的講解只限于簡單原理的講解。如果有錯誤,歡迎批評指正。

1. 單片機常用電路1-晶振電路

早期的單片機(比如經典的51單片機)系統,外接晶振是必須的(當然也可以外接時鐘脈沖,但是很少用),因為單片機的運行必須依賴于穩定的時鐘脈沖。但是隨著技術的發展,現在很多單片機都已經集成了內部時鐘,所以在一般的應用場合,可以不用外接晶振電路了。不過由于內部時鐘容易受外界干擾,所以在要求嚴格的場合,晶振電路還是很有必要的。

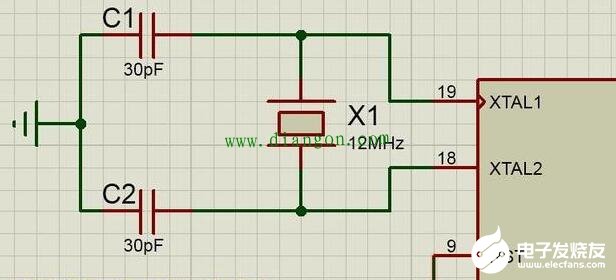

圖1是典型的單片機外接晶振電路。

圖1 單片機晶振電路

該電路不只是有一個晶振,還有兩個電容,這兩個電容有什么作用呢?

這兩個電容一般稱為“匹配電容”或者“負載電容”、“諧振電容”。晶振電路中加這兩個電容是為了滿足諧振條件。一般外接電容,是為了使晶振兩端的等效電容等于或接近負載電容。只有連接合適的電容才能滿足晶振的起振要求,晶振才能正常工作。

負載電容的值由如下公式計算:

負載電容無法滿足的話一般會使晶體頻率產生偏差,嚴重的話晶體無法起振。電路設計中要盡量滿足晶體的負載電容需求,從而使晶體工作在最佳狀態。負載電容計算公式如下:

CL = C1*C2 / (C1+C2) + CS

CL為晶振的負載電容值,一般通過查詢晶振的數據手冊獲得。CS為電路板的寄生電容,一般取 3~5pF,取C1 = C2,那么公式可以簡化成如下:

CL = C1 / 2 + CS

一般情況下,增大負載電容的值會使振蕩頻率下降,減小負載電容的值,會使振蕩頻率上升。

晶振電路2

我們有時候還會看到如圖2所示的晶振電路。

圖2 不帶并聯電阻和帶并聯電阻的晶振電路

該電路中晶振上又并了一個電阻,這是為什么呢?

這個電阻實際上是反饋電阻,是為了方便晶振起振的。對于COMS而言,這個電阻的阻值可以是1M以上,對于TTL則是需要視情況而定。最好的辦法是看看芯片的數據手冊,確認芯片晶振電路內部是否有電阻,如果沒有,電路設計時最好加上。

晶振電路3

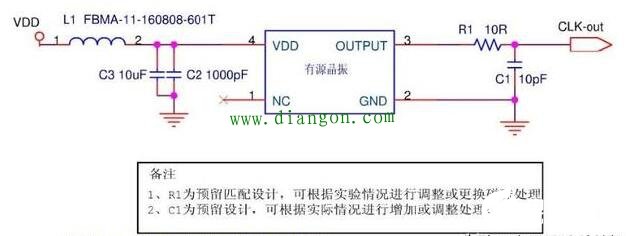

圖3是有源晶振電路。

圖3 有源晶振電路

有源晶振通常的用法:一腳懸空,二腳接地,三腳接輸出,四腳接電壓。有源晶振不需要CPU的內部振蕩器,連接方式相對簡單(主要是做好電源濾波,通常使用一個電容和電感構成的PI型濾波網絡,輸出端用一個小阻值的電阻過濾信號即可),不需要復雜的配置電路。相對于無源晶體,有源晶振的缺陷是其信號電平是固定的,需要選擇好合適輸出電平,靈活性較差,而且價格高。