最近在芯片設計和制造方面的技術進步已經成就了第二代數字電容隔離器,其高性能給低功耗和高可靠性定義了新的標準。本文將介紹其功能原理和內部結構,并討論其電流消耗和預計壽命。

功能原理

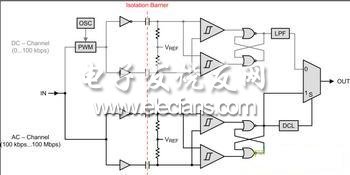

圖 1 顯示了一款數字電容隔離器?(DCI) 的內部結構圖。該隔離器輸入分為兩個差分信號路徑:一條為高數據速率通道(稱作 AC-通道),另一條為低數據速率通道(稱作 DC-通道)。AC-通道傳輸介于 100 kbps 和 100 Mbps 之間的信號,而DC-通道則涵蓋了從 100 kbps 到 DC 的范圍。

?

圖 1 數字電容隔離器的內部結構圖

高速信號由 AC 通道來處理,信號在通道中首先從單端模式轉換為差分模式,然后被隔離層的電容-電阻網絡差分為許多瞬態。后面的比較器再將這些瞬態轉換為差分脈沖,從而設置和重置一個“或非”門觸發器。相當于原始輸入信號的觸發器輸出饋至判定邏輯(DCL) 和輸出多路復用器。DCL 包括一個看門狗定時器,該定時器用于測量信號轉換之間的持續時間。如果兩個連續轉換之間的持續時間超出定時窗口(如低頻信號的情況下),則 DCL 則指示輸出多路復用器從 AC-通道切換到 DC-通道。

由于低頻信號要求大容量電容器,而這種電容器使片上集成變得很困難,因此DC-通道的輸入要有脈寬調制器(PWM)。該調制器利用一個內部振蕩器 (OSC) 的高頻載波對低頻輸入信號進行調制。在 AC-通道中對調制后信號的處理過程與高頻信號相同。然而,在向輸出多路復用器提交該信號以前,需通過一個最終低通濾波器 (LPF) 濾除高頻 PWM 載波,以恢復原始、低頻輸入信號。

相比其他隔離器技術,電容隔離器的一個主要優點是其 DC-通道在上電和信號丟失 (LOS) 事件期間隔離器輸出端擁有正確的輸入極性。缺少這些特性的其他隔離器技術通常會在上電期間出現輸出突波,或者在信號丟失以前一直保持在最后一個輸入極性。

內部結構

圖 2 顯示了一個單通道、電容隔離器的內部結構簡化結構圖。從內部來看,隔離器由兩顆芯片組成:一個發送器和一個接收機芯片。實際隔離層由接收機芯片上的高壓電容器來提供。

由于 AC-通道和 DC-通道均使用一種差分信號技術在數據傳輸期間提供高噪聲抗擾度,因此必需要有 4 個隔離電容器來形成一條單隔離數據通道。

?

圖 2 單通道電容隔離器的內部結構

圖 2 的右側顯示了一個高壓電容器的橫截面。從發送器芯片出來的接合線連接到接收機端電容器鋁頂板。底板(也為鋁質)連接到接收機邏輯。板之間是夾層電介質,其為 16-μm 厚的二氧化硅 (SiO2)層。

使用 SiO2 作為夾層電介質有兩個好處:一、它是具有最小老化效應且最穩定的隔離材料之一,因此電容隔離器的預計壽命遠遠超過其他技術;二、使用標準半導體制造技術就可以處理 SiO2,從而大大降低了生產成本。

電容隔離的另外一個優點是每個電容 123 毫微微法拉 (123 x 10 -15 F) 的超低容量,從而允許極高的數據速率傳輸并實現多通道隔離器的微電容幾何尺寸。

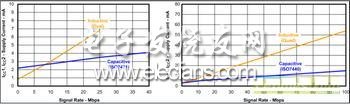

電流消耗

隔離器電流消耗高度依賴于內部結構。相比雙通道隔離器,電感型隔離器似乎具有最低的 DC 電源電流(請參見圖 3)。這是因為該器件只包含 2 條信號通道。但是,電容隔離器包含 4 條通道:2 條 AC 通道和 2 條 DC 通道。因此,其 DC 的電流消耗更高,而且其可靠性也更高,因為在輸入信號丟失的情況下其可確保正確的輸出極性。

系統空閑時就會出現 DC 電流。幸運的是,工業數據獲取系統、PLC 和數字模擬 I/O 模塊并非針對系統空閑而設計,其目的是將數據從傳感器傳輸到控制單元,并從控制單元傳輸到傳動器。這些工作的完成必須是快速、可靠和持續的。

一般而言,雙通道隔離器用于隔離式 CAN 和 RS-485 總線節點,其中只有 2 條數據線路(發送和接收)要求隔離。例如,RS-485 收發器必須能夠在一些極端共模狀態下提供高達 ± 70mA 的驅動力才能達到標準。這樣,即使在低數據速率條件下,DC 電流之間的差異也可以忽略不計。

?

圖 3 電容和電感隔離器的電流消耗(左圖為雙通 道隔離器,右圖為四通道隔離器)

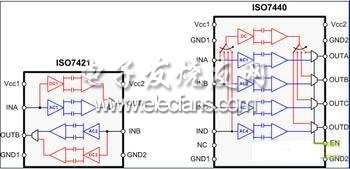

相比四通道隔離器,圖示結果有所改善。通道數為原來的兩倍,因此電感隔離器的電流消耗也增加了一倍,然而相比雙通道隔離器,四通道電容隔離器的通道數僅增加了一條。出現這種結果的原因是,僅使用了一條 DC-通道,其在四條 AC-通道之間得到多路傳輸(請參見圖 4)。DC 通道仍然擁有高可靠性的同時,總電流消耗維持在最低水平,從而比雙通道版本僅有最低限度的增加。

?

圖 4 雙通道及四通道電容隔離器的通道結構

四通道隔離器用于隔離包括數據和控制線路的接口(例如:SPI),其數據速率一般可達 20 到 80 Mbps。電感和電容隔離器之間的電流消耗在 30 Mbps 下時已經有 10mA 以上的差別,在如 100 Mbps 等更高數據速率下時這一差別可高達 40mA。

因此,它其實并非重要的 DC 電流,而是數據速率的電流增加,即斜率 Δi/Δf。

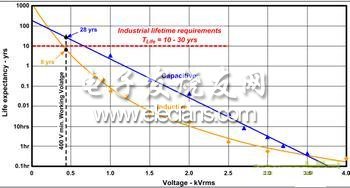

預計使用壽命

隔離器的預計使用壽命由經時擊穿 (TDDB) 決定,其為一種二氧化硅等電介質材料的重要故障模式。由于制造帶來的雜質和不完整性缺陷,電介質會隨時間而退化。這種退化會由于電介質上施加的電場及其溫度的上升而加快。

預計使用壽命的確定是基于 TDDB E 模型,其為一種廣受認可的電介質擊穿模型。

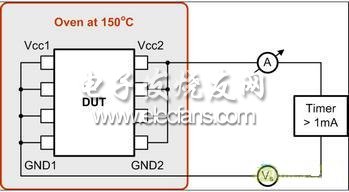

實際上,周圍溫度維持在 150oC 時,TDDB 由隔離器的施加應力電壓決定(請參見圖 5)。測試之初便激活一個計時器,其在隔離器電流超出 1 mA 時停止,表明電介質擊穿。記錄每個測試電壓的故障時間,并根據理論 E 模型曲線進行繪圖。

?

圖 5 TDDB 測試方法

圖 6 所示的 TDDB 曲線表明,電容隔離器的測試數據(時間為 5 年)完全匹配 E模型預測,從而得出在 400 Vrms (560 Vpk) 工作電壓下 28 年的預計使用壽命,而相同電壓下電感隔離器的預計使用壽命則小于 10 年。TDDB 曲線還表明,在 700 V 和 2.5 kV 之間電容隔離器的壽命比電感隔離器長約 10 倍。

?

圖 6 電容和電感隔離器的預計使用壽命

若要達到 10 到 30 年的工業預計使用壽命,使用 SiO2 電介質的電容隔離器是實現這個目標唯一可行的解決方案。