用在退耦電路中的電容稱為退耦電容也叫去耦電容,退耦電容并接于電路正負極之間,可防止電路通過電源形成的正反饋通路而引起的寄生振蕩。所謂退耦,即防止前后電路電流大小變化時,在供電電路中所形成的電流波動對電路的正常工作產生影響,換言之,退耦電路能夠有效地消除電路之間的寄生耦合。

電容的擺放

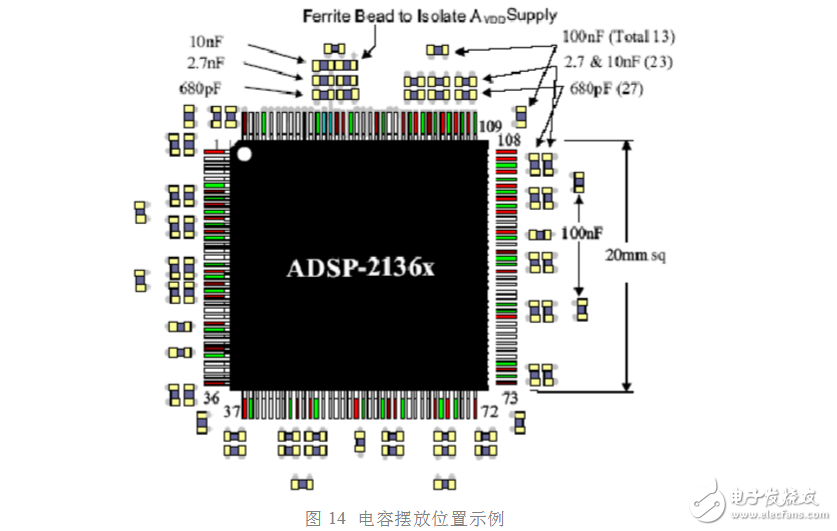

對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍遠,最外層放置容值最大的。但是,所有對該芯片去耦的電容都盡量靠近芯片。下面的圖14就是一個擺放位置的例子。本例中的電容等級大致遵循10倍等級關系。

還有一點要注意,在放置時,最好均勻分布在芯片的四周,對每一個容值等級都要這樣。通常芯片在設計的時候就考慮到了電源和地引腳的排列位置,一般都是均勻分布在芯片的四個邊上的。因此,電壓擾動在芯片的四周都存在,去耦也必須對整個芯片所在區域均勻去耦。如果把上圖中的680pF電容都放在芯片的上部,由于存在去耦半徑問題,那么就不能對芯片下部的電壓擾動很好的去耦。

退耦電容的布置和布線

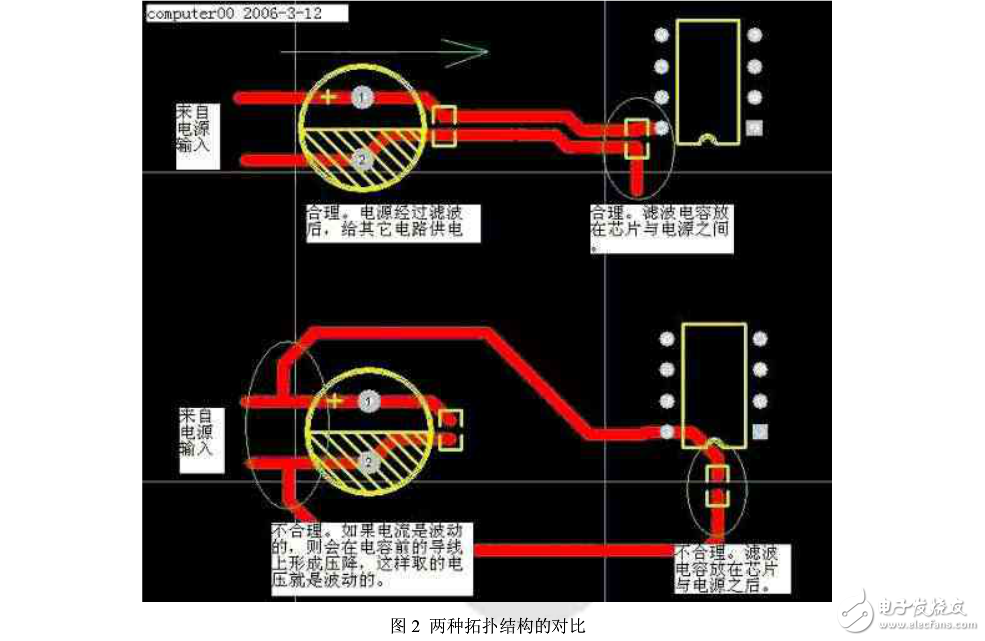

去耦電容放置在負載器件的電源和地之間,主要有兩個作用:一方面是作為負載器件的蓄能電容,避免由于電流的突變而使電壓降,相當于濾除紋波; 另一方面旁路掉該器件的高頻噪聲。在很多設計中,去耦電容通常使用容量相差一個數量級以上的兩個甚至更多的電容并聯,為的是提高電源供應電路從高到低頻的瞬態響應。

理論上電容越大,低頻的通過性越好,濾波效果也越好,但電容器的原理和結構也決定了大如等效電感和等效電阻都明顯高于小電容,同時PCB走線也存在一定的分容量電容的分布參數,布參數。只是這些分布參數的在低頻時表現并不明顯,所以布局安排上可以將大容量電容放得遠離有源器件一些。

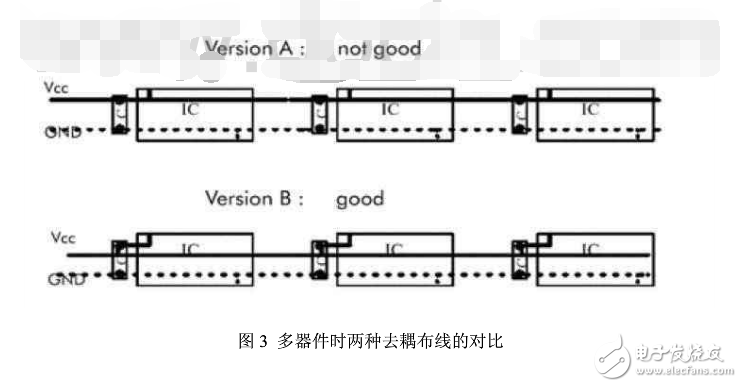

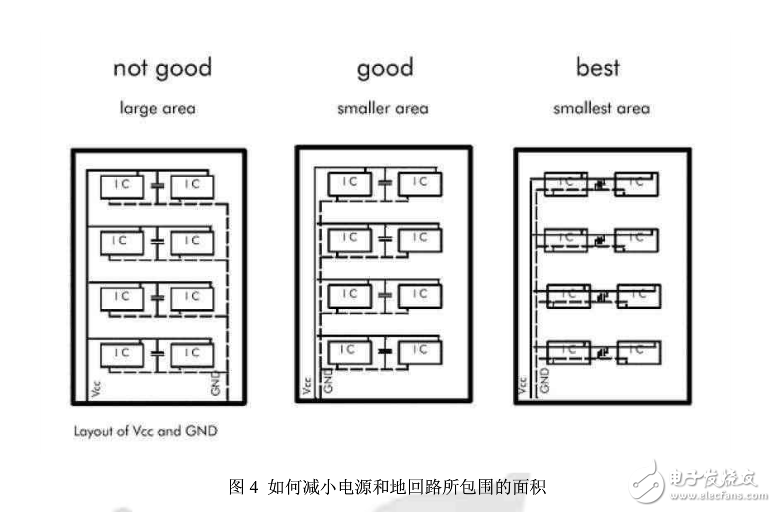

隨著工作頻率升高,濾波器件的感抗和PCB線路感抗開始呈現,且頻率越高感抗越大,對供電回路的紋波影響越明顯,因此需要選用感抗小的小容量電容提供良好的去耦。同時還應縮短濾波電容兩端到負載的電源與地的距離,盡可能將去耦電容和負載器件放置同一層。為降低EMI,也應盡量減小電源線和地回路之間包圍的面積。

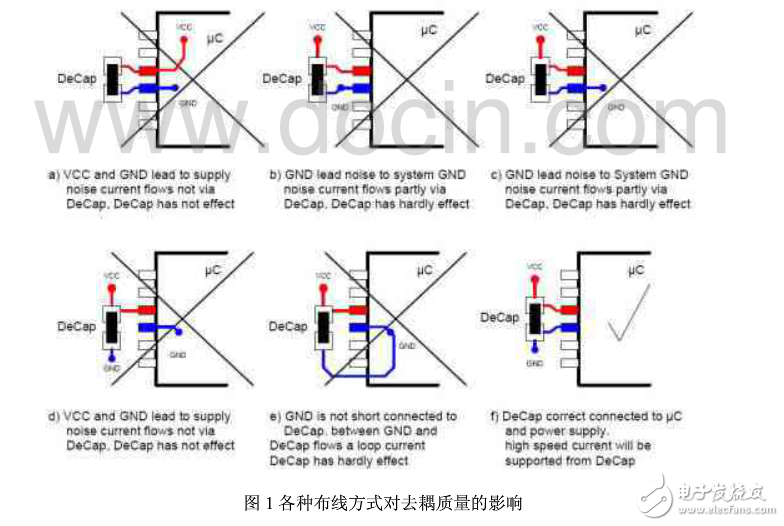

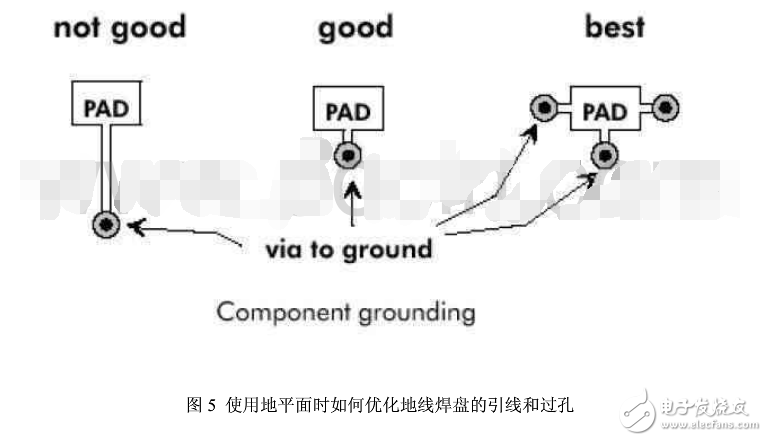

以下圖例都是說明如何設計良好的去耦電路拓撲結構和布線策略。