從電路來說,總是存在驅動的源和被驅動的負載。如果負載電容比較大,驅動電路要把電容充電、放電,才能完成信號的跳變,在上升沿比較陡峭的時候,電流比較大,這樣驅動的電流就會吸收很大的電源電流,由于電路中的電感,電阻(特別是芯片管腳上的電感,會產生反彈),這種電流相對于正常情況來說實際上就是一種噪聲,會影響前級的正常工作。這就是耦合。

去藕電容就是起到一個電池的作用,滿足驅動電路電流的變化,避免相互間的耦合干擾。

旁路電容實際也是去藕合的,只是旁路電容一般是指高頻旁路,也就是給高頻的開關噪聲提高一條低阻抗泄防途徑。高頻旁路電容一般比較小,根據諧振頻率一般是0.1u,0.01u等,而去耦合電容一般比較大,是10u或者更大,依據電路中分布參數,以及驅動電流的變化大小來確定。

旁路是把輸入信號中的干擾作為濾除對象,而去耦是把輸出信號的干擾作為濾除對象,防止干擾信號返回電源。這應該是他們的本質區別。

交流耦合電容

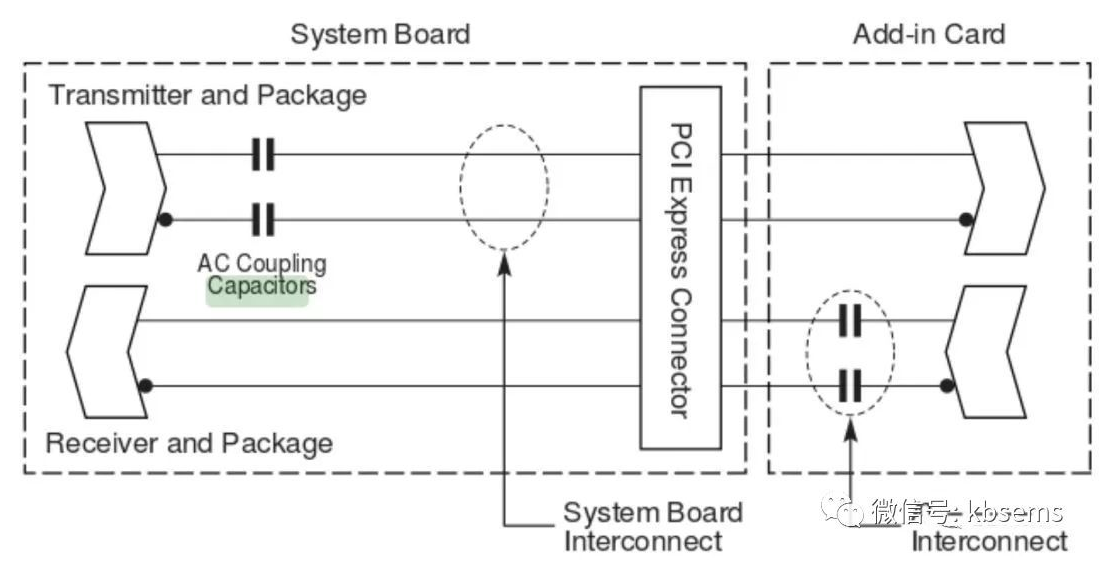

我們在處理高速差分信號的時候,經常使用交流耦合,也會使用直流耦合, 比如PCI Express我們看到的是交流耦合, 早期光模塊和芯片之間的LVPECL則更多地使用直流耦合, 這篇文章我們不打算討論什么情況下使用交流耦合,什么情況下使用直流耦合,我們要討論的是使用交流耦合時需要解決的問題。

很簡單的一個問題, 交流耦合的電容需要選擇多大?我們最常見的有0.1uF和0.01uF, 可是我們有想過為什么嗎?為什么不選更大或者更小的?今天我們試圖來用最簡單的方式來解釋,我們先使用頻域的方式。

頻域

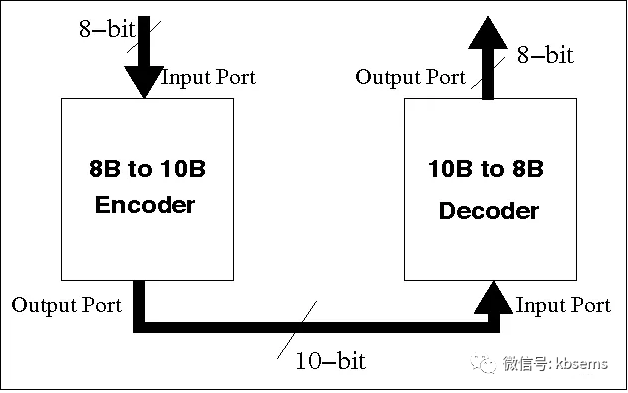

以PCIE為例, 我們知道PCIE內含8b/10b編碼,并且我們知道它的所謂2.5Gbps (PCIE1.0), 5Gbps (PCIE2.0),8Gbps (PCIE3.0)速率指的包含了8b/10b后的速率,也就波特率,這一點和以太網不一樣,千兆以太網的SGMII接口速率其實1.25Gbps,去除8b/10b后比特率是1000M,所以這里的千兆指的payload速率,而且PCIE的速率指的是加上開銷以后的速率。

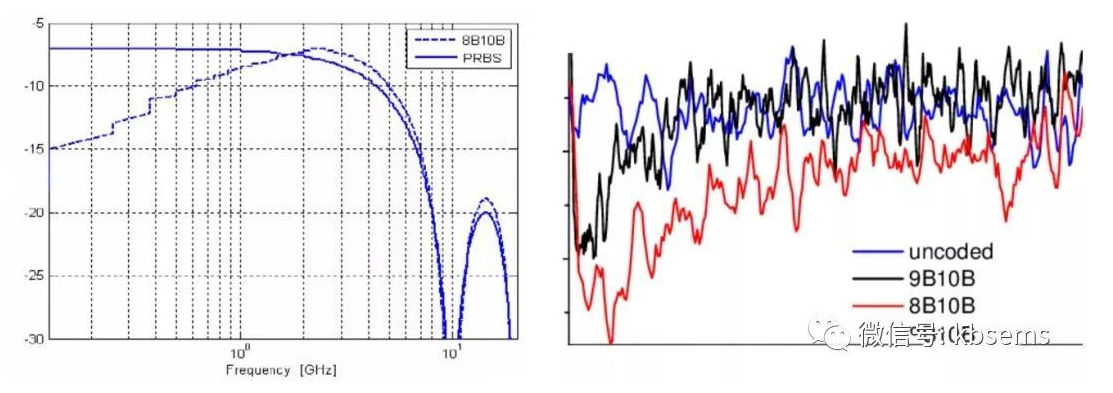

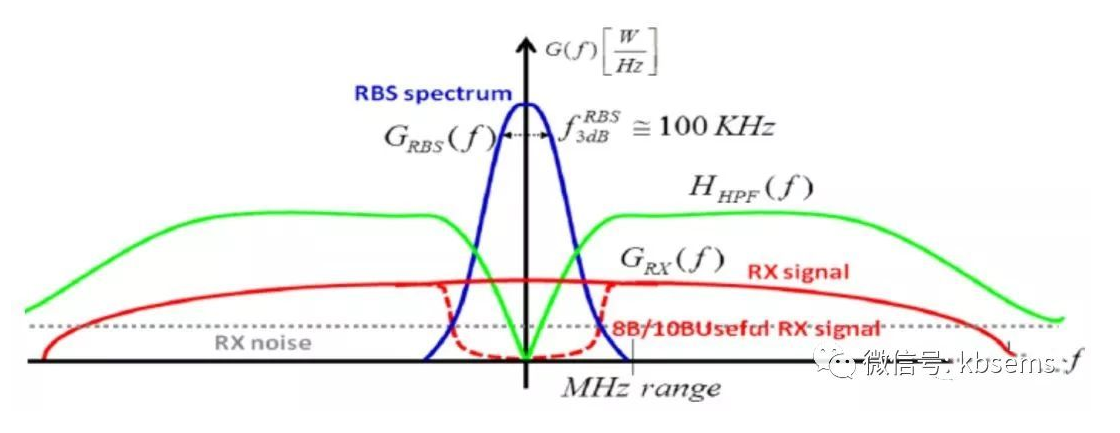

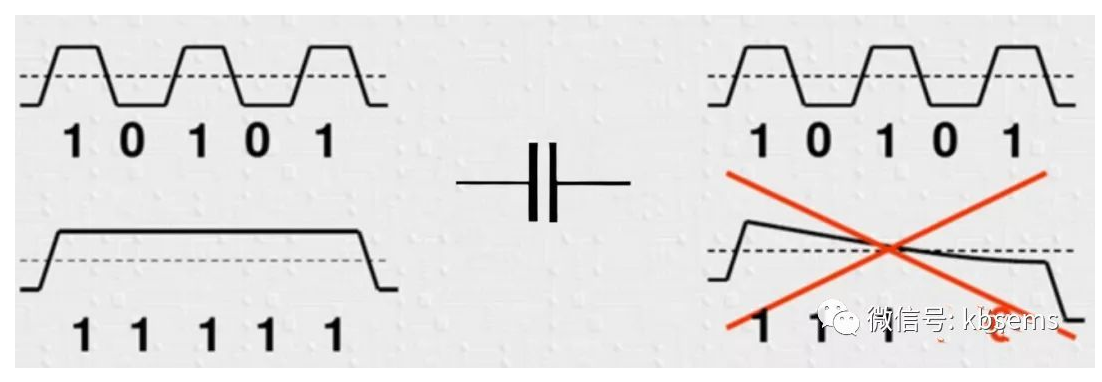

題外話不多說, 我們知道8b/10b作用是確保0和1的平衡,使得信號不會出現很長0和很長的1,防止接收端的CDR失鎖,也就是去除了信號的低頻部分,使得信號的頻譜保持在某個頻率以上。如圖所示經過8b/10b編碼后信號的頻譜在低頻段衰減了8dB。

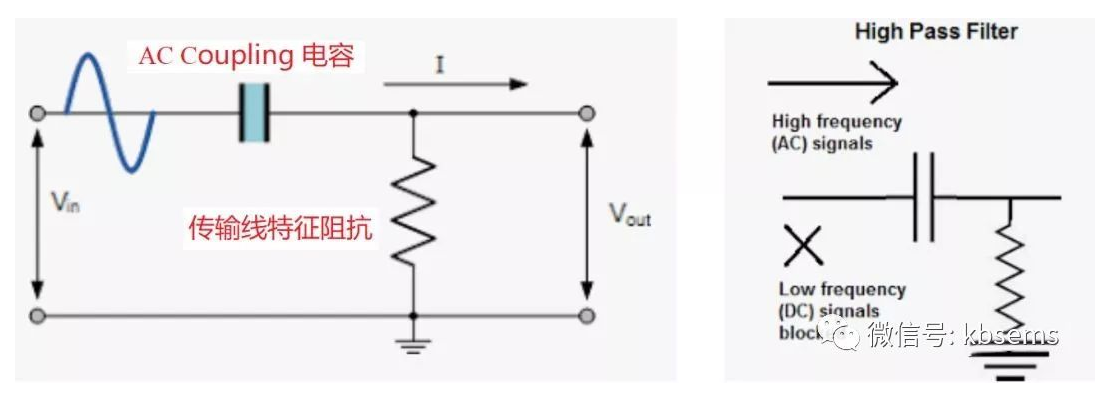

那么我們怎么去除?為什么我們要去除低頻,保留高頻呢?這還得從AC耦合的結構原理說起:

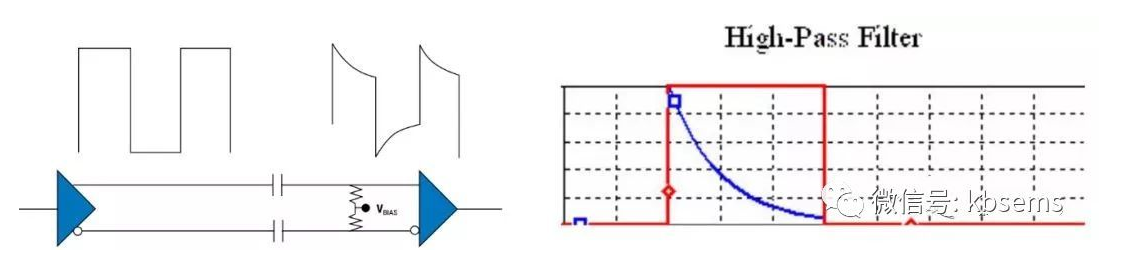

根據上圖,我們進一步細化一下模型如下:

我們看到耦合電容和傳輸線的特征阻抗組成了一個高通的濾波器, 如下面的圖所示我們需要確保此High pass filter的截止頻率(綠色線)要低于信號經過8b/10b后的頻譜的最低點(紅色線),因為只有這樣才能確保信號的能量完整的通過。

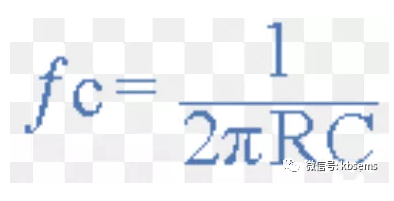

下面我們來計算一下:

1. 傳輸線特征阻抗Zr=50;

2. AC coupling電容值為C;

3. PCIE信號經過8b/10b后的信號頻譜也是已知的,用頻譜儀測一下或者簡單用速率(比如PCIE2.0的5Gbps)除以4簡單估算一下, 因為8b/10b最長0或者1只有4位了;

下面我們就來計算電容的值:

我們很容易就能得出C的值了,簡單吧。

時域

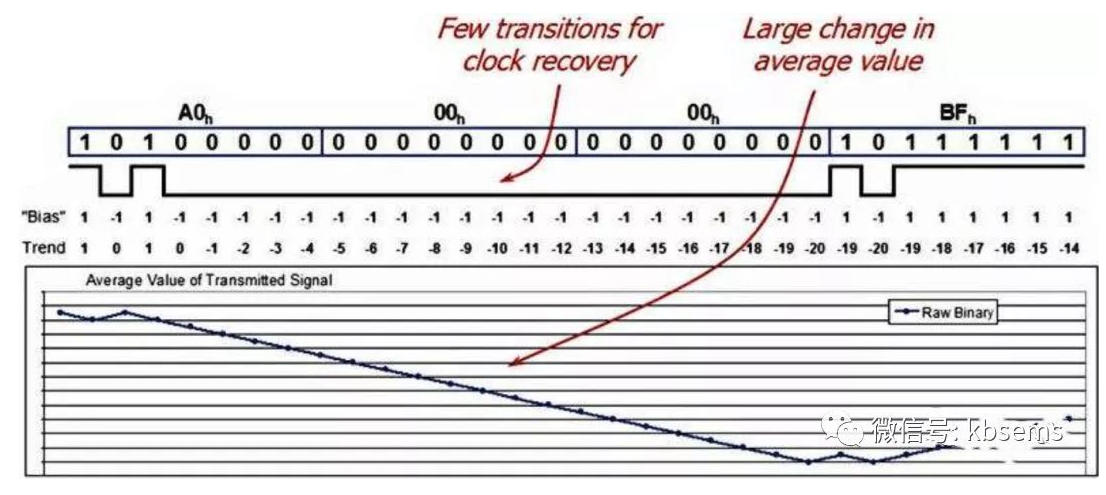

從時域來解釋, 如果不用8b/10b的話,問題有兩個,請看下面這段英文的精妙論述:AC coupled data signals would have DC drifts depending on the data content. A long sequence of 1′s will lead into positive drift and many 0′s will drift toward negative voltage. 意思是說如果沒有8b/10b的話,信號的長0和長1會使得信號本身發生直流漂移。

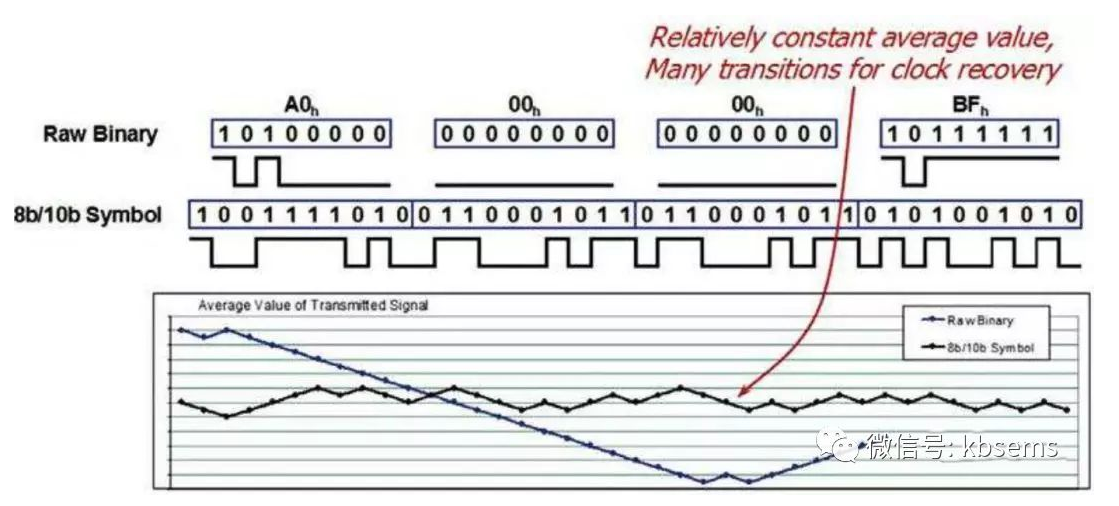

而加了8b/10b以后, CDR和恢復和信號直流漂移問題解決,下面這張圖我們再來看, 所謂的“constant average value”已經趨于水平而不會上下搖擺。

我們繼續闡述8b/10b在時域的作用,信號經過了ac coupling電容之后,相當于經過了一個高通的濾波器,會產生的問題如下,高頻跳變的能量可以順利通過, 而低頻的長0和長1則不能通過, 低頻信號發生了畸變,而經過了8b/10b后,信號的低頻部分被消除,也不會有畸變的事情發生了。

那么是不是說加了8b/10b后,使用ac coupling就什么問題都沒有了呢? 不是, 我們需要仔細考慮計算我們的ac coupling電容的大小。我們先來看看經過high pass后時域信號發生的變化:

我們看到仍然有部分低頻部分被去除,這可能是由于電容選擇不合理,我們先來看看電容取值如果太小會怎么樣?

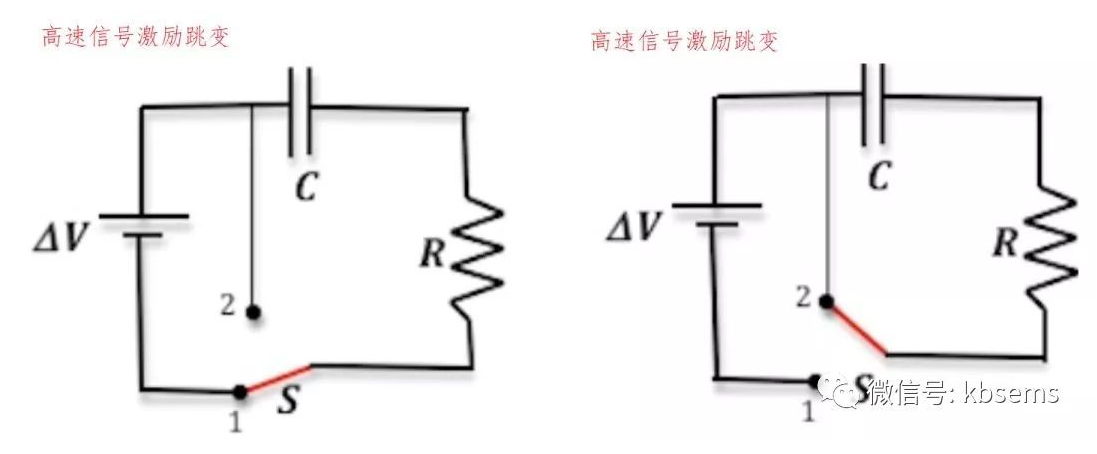

電容如果取值太小,高速信號在充放電的時候,很顯然容易飽和,我們知道電容一旦飽和,阻抗就會變得很大,抵抗外面的高速信號的變化,為什么小電容容易飽和呢? 我們想象一下, 電容的正負極板其實是隨著信號跳變也在不停地做充放電,這樣極板兩邊的極性才會隨著信號的高低而變化,如果是小電容再加上長0長1的低頻部分到來,一下就充滿了。一旦充滿,最終導致信號的有效低頻部分被去除,如下如所示,連續三個1就會導致電容飽和,我們仔細看一下變化的步驟:

1) 開關打到1;

2) 電容阻抗無窮小,電阻分壓最大;

3) 隨著電容充電,電容的阻抗在變大,如果飽和了,阻抗就變得無窮大,阻礙外部的交流變化,而且電阻上的分壓變得很小,導致直流漂移;

4) 開關打到2;

5) 電容開始放電,如此周而復始。

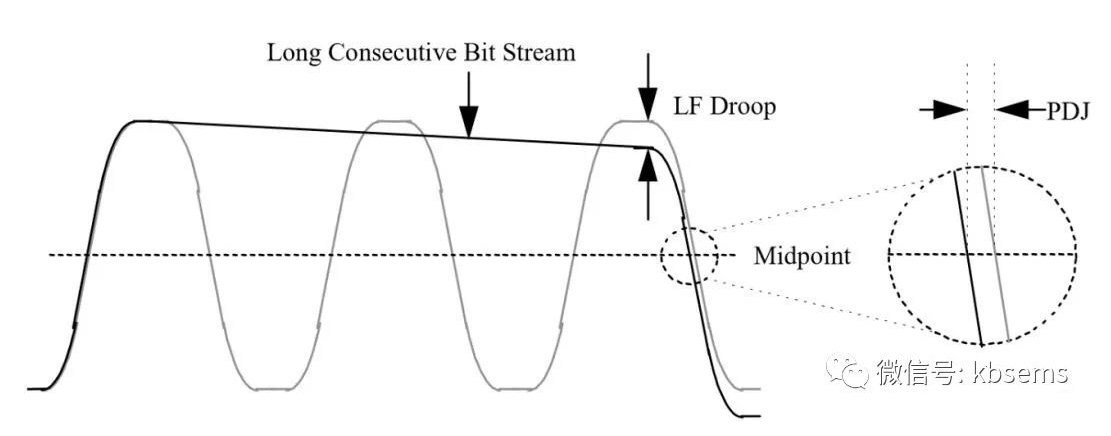

我們可以看到直流電平緩慢下降的直流漂移會帶來什么, 會帶來抖動,這種特殊的抖動叫PDJ。

我們看到出現1110的數據時,就會在1到0轉變的邊沿偏離,產生抖動,產生的原因很簡單,就是因為直流電平的起點低了,導致下降沿比正常的周期跳變信號提前了, 這種抖動是我們不喜歡的,一方面信號變形,另外一方面CDR需要跟蹤并且修復這種抖動, 是的眼圖質量裂化,誤碼率升高。

那么電容選太大會怎么樣? 當然很容易想明白,不能選太大的電容,因為大電容含有ESL/ESR,也會對信號有衰減。

所以從時域和頻域的兩個角度,我們知道高速信號的ac coupling的電容選擇需要仔細計算和考量, 不能隨意。