一則CMOS電路設計問題

這次遇到的問題是這樣的,由于LDO的電源輸出能力有限,同時也是保證可靠性,某些保護電路必須直接電源上,這里需要注釋的是,LIMP HOME“跛行回家”即使我們的5V系統出現了問題,我們也必須保證部分重要的功能能繼續工作,因此為了滿足這個條件,關鍵信號的供電只能是直接接電池。

這次第一個出問題的是一個CMOS的與門(HE4000B系列的)。

我們的控制信號出自MCU(5V的系統),而與門的系統供電是12V的,因此兩個電平不兼容,導致了MCU的高低電平統一被與門CMOS芯片識別成低電平。

我們在設計轉換電平的時候,有兩個問題需要我們去注意

1.要相同的邏輯,不能做成反邏輯

2.在正常狀態下,不能允許大的電流(為了符合靜態電流的要求)這里設計的是低有效電路,因此在輸出高的時候不能出現大的靜態電流。

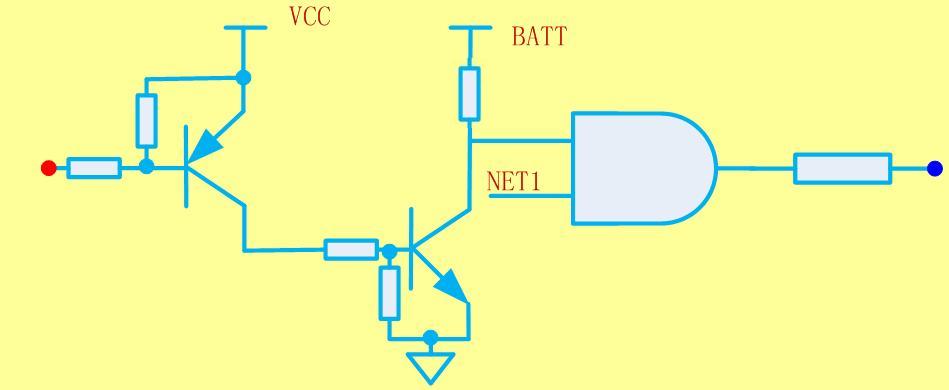

可行的改進設計為:

不過一波未平一波又起,由于ISO16750的規定

而我們的與門能夠承受的電壓為18~20V,這也是所有CMOS的IC的極限電壓,因此該芯片華麗的燒毀了(在我們做1分鐘的Jump Start實驗的時候)

我們的解決方案,加個齊納管15V鉗位

此電阻需要仔細斟酌,因為在24V的時候,有7V的電壓在電阻上面,要限制齊納管的電流防止其過熱,同時又要保證CMOS的正常工作電流下,電壓不會下降的太厲害。

V.CMOS=V.BATT-R.limit×I.AND

I.zener_max=(24-15)/R.limit

以上需要綜合考慮。