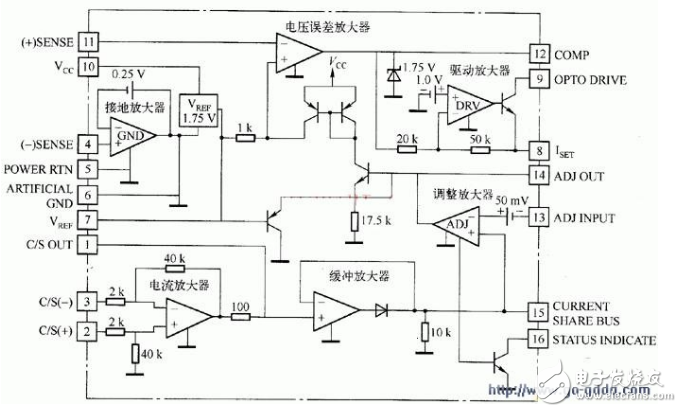

UC3907集成電路芯片的內部結構原理,工作電源V∝(10腳)的電壓范圍為4.5~35V;芯片內有一個基準電壓源VREF,其值相對于ARTIFICIALGND(6腳)為1.15V,也可以從VREF(7腳)輸出;ARTIFICIALGND是芯片的低阻地(參考地),它比(—)SENSE(4腳)的電位高0.25V,這一電壓偏置為接地放大器的工作電流提供回路,而使電壓采樣負端(—)SENSE(即接地放大器的反相輸人端)為高輸入阻抗。

工作原理:電流采相信號由C/S(+)(2腳)和C/S(—)(3腳)差動輸人到電流放大器,電流放大器是一個增益固定為20的低通差分放大器,允許共模輸人電壓范圍為:最低值為功率返回線POWERRTN(5腳)電位,最高值為Ugp-2V,允許差模輸人電壓范圍為50~500mV。電流放大器的輸出,一方面經過緩沖放大器連接到均流母線CURRENTSHAREBUS(15腳);另一方面與均流信號一起,經過調整放大器生成環流信號,還可以通過STATUSINDICATE(16腳),輸出主模塊狀態指示信號。

緩沖放大器輸出到均流母線(15腳),各個并聯電源模塊與均流母線相連,以實現均流。均流母線對地短路或電位高于50 V時,保護電路動作,因此均流母線開路或短路,都不會影響各電源模塊的獨立工作。

輸出電壓采樣信號由(+)SENSE(11腳)和(—)SENSE(4腳)差動輸入到電壓誤差放大器,以實現電壓放大和系統頻率特性校正,電壓環補償網絡跨接在電壓放大器的反相輸人端(11腳)和輸出端COMP(12腳)。

驅動放大器是一個反相緩沖器,接在電壓放大器之后,它的增益固定為2.5倍,通常驅動外接光耦將電壓誤差信號耦合到電源模塊的PWM控制器,具體來說,UC3907的OPTODRIVE(9腳)接外部光耦的發光二極管負端(其正端接UCC),如圖11- l6所示。吸人電流由接在ISET(8腳)與地之間的電流設定電阻決定,該電流最大允許值為20 mA。這時的調節極性是:光耦電流隨著模塊輸出電壓的上升而增大。在非隔離應用場合,可以直接利用8腳輸出的電壓信號(0.25~4.1 V),相應地調節極性是:8腳電位隨著模塊的輸出電壓上升而變高。

UC3907的5腳,一般接分流器的負端,該點的電位是最低的,它允許比(—)SENSE腳低0~5 V。

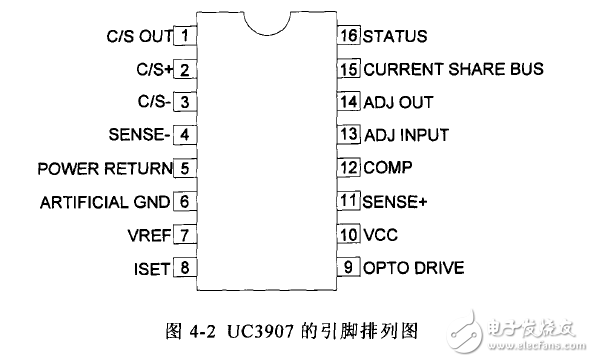

UC3907采用雙列直插16腳封裝,引腳賠禮如圖所示,各引腳功能如表格所示: