PCI總線支持突發傳送,多處理器和并發工作,廣泛應用于各種平臺設計。基于PCI9054的接口板也廣泛地應用于各種高速、大數據量的處理系統。由于PCI9054橋接有PCI總線和本地總線,開發者不必過多考慮復雜的PCI總線規范,從而能有更多精力開發硬件和驅動程序設計。

這里以PCI9054為例,給出了接口板的硬件和軟件設計,詳細論述了該系統設計的原理圖和用VHDL語言編寫的部分邏輯源程序,以供相關開發人員參考。

1 PCI9054簡介

PCI9054是PLX公司推出的一種32位33 MHz的PCI總線主控I/O加速器,它采用PLX在業界領先的數據流水線框架,包含DMA引擎,可編程的PCI起始器和目標數據傳輸模式以及PCI信息傳輸功能。遵循PCI2.2版規范,可獲得最高可達132 MB/s的突發傳輸速度。它使復雜的PCI接口應用設計變得相對簡單,目前已成為主流的PCI接口器件之一。

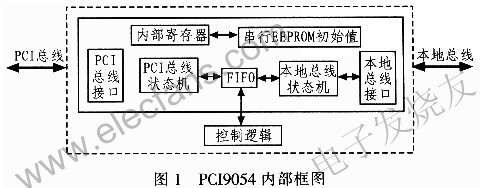

PCI9054數據傳輸有3種方式:主模式、從模式和DMA方式。其內部具有2個DMA數據通道,每個通道均支持塊Scatter/Gather的DMA方式,雙向數據通路上各有6個FIF0進行數據緩沖,可同時進行高速的數據接收和發送,8個32位Mailbox寄存器可為雙向數據通路提供消息傳送,PCI9054內部框圖,如圖1所示。

PCI9054的本地總線有M、C、J 3種工作模式,可通過模式選擇引腳MODE[1:0]進行控制,其中C模式能夠滿足絕大多數的應用需求,而且C模式的本地總線操作時序最為簡單,邏輯控制相對容易,其開發難度相對較低。C模式下PCI9054通過片內邏輯控制將PCI的地址線和數據線分開,很方便地為本地工作時序提供各種工作方式,一般較廣泛應用于系統設計中。因此,如無特殊需求,建議采用C模式,這也是本接口卡所采用的模式,同時PCI9054的本地總線時鐘可由外部提供,該時鐘可和PCI時鐘異步。

2 接口卡硬件設計

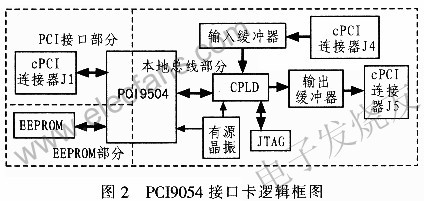

接口卡主要功能是:對外設裝置進行工作模式和狀態檢測,控制端對檢測結果進行相應的數據接收或發送操作。其工作流程是:由控制端提出請求,根據進入接口卡的信號對外部設備進行工作模式和狀態檢測并決定是否對進入外設的信號進行接收或發送。機械特性方面,接口卡遵從Eurocard工業標準,采用6U(233.35 mmxl60 mm)結構。接口卡的邏輯框圖如圖2所示。

由圖2可知,接口卡分為3個部分:PCI總線接口、本地總線接口和串行EEPROM接口。

2.1 PCI9054與PCI總線接口

PCI9054與PCI總線接口的連接實際上是PCI9054與cPCI連接器Jl的連接,即PCI9054的PCI端信號線通過10Ω的端接電阻與PCI插槽的相應信號線對應連接。PCI總線接口信號包括地址數據復用信號線、接口控制信號線、中斷信號線等。PCB設計時,為了滿足反射條件,需注意PCI總線信號的布線及長度,普通信號長度,從連接器到PCI橋器件間距應不大于1.5英寸(3.81 cm),PCI_CLK信號布線長度為2.5±0.1英寸,否則會導致信號不穩定甚至總線沖突,無法開機。PCI9054內部有可編程的FIF0,實現零等待突發傳輸及本地總線與PCI總線之間的異步操作,本地總線時鐘由外部提供,該時鐘可以和PCI時鐘(33 MHz)異步,本地總線選擇工作在50 MHz,由頻率為50 MHz的晶振OSCl產生,同時

送往PCI9054本地端的時鐘信號LCLK與送往CPLD的時鐘信號CCLK要等長,以保持它們同步。

2.2 PCI9054與本地總線接口

本接口卡中的CPLD采用Xilinx公司生產的XC95288XL,實現對接口卡的邏輯控制。C模式下PCI9054通過片內邏輯控制將PCI的地址線和數據線分開,然后與CPLD相對應的引腳連接,能方便為本地工作時序提供各種工作方式,一般廣泛應用于系統設計。

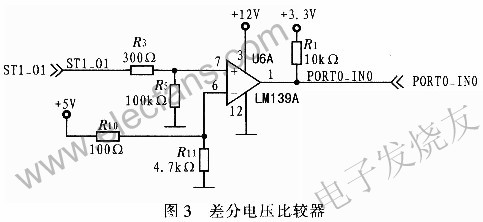

本地總線部分中的INPUT_BUFFER部分主要由差分電壓比較器組成,如圖3所示。當從J4進入的信號電壓(引腳7)大于基準電壓(引腳6)時,輸出高電平(引腳1)并進入CPLD,控制器通過PCI9054讀入。0UT_BUFFER部分主要是實現控制器對外設接收或發送數據的控制。

2.3 PCI9054與EEPROM接口

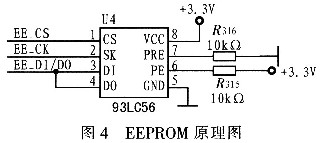

PCI9054提供4個引腳EEDI,EED0,EESK,EECS與串行EEPROM-93LC56的4個引腳DI、D0、SK、CS相連,此外93LC56的VCC引腳需要接+3.3 V電源,GND接地。因為需要對串行EEPROM進行寫操作,串行EEPROM需處于可編程而且非保護狀態,所以PE通過10 kΩ的電阻上拉后接高電平3.3 V電壓,而PRE通過10 kΩ的電阻下拉后接地。EEPROM原理圖如圖4所示。

連接好PCI9054與PCI總線接口、本地總線接口和串行EEPROM接口后,還需對寄存器進行配置,配置時需借助于Windriver工具,寄存器的配置包括PCI配置寄存器的配置、本地配置寄存器的配置及對EEPROM初始化。

配置PCI配置寄存器主要是填寫生產商ID號、器件ID號、子系統生產商ID號和類碼子系統ID號。對于PCI9054,其生廠商ID號,器件ID號,子系統號,子系統ID號等是固定的,可以在PCI9054數據手冊中查到。

本地配置寄存器的配置是對本地地址空間及本地總線屬性的配置,這種配置根據實際開發需要進行,配置完成后,在主機CPU要訪問本地地址空間時,可能給出對應的PCI總線地址。

PCI9054在加電啟動時,從外部EEPROM讀取初始化數據來配置PCI9054的內部寄存器,在板卡加電自檢期間,PCI總線的RST#信號復位,PCI9054內部寄存器的默認值作為回應。PCI9054出本地LRESET#信號并檢測串行EEPROM。

如果串行EEPROM中的前33位不全為1,那么PCI9054確定串行EEPROM非空,用戶可通過向PCI9054的寄存器CNTRL的29位寫1,來加載EEPROM的內容到PCI9054的內部寄存器,配置的信息可以在P1xSdk的PLXMON下對EEPROM進行配置。

3 接口卡軟件設計

3.1 CPLD邏輯設計

PC39054通過本地總線與本地總線設備進行通信,PCI9054提供2種訪問方式,即單周期訪問和突發方式訪問。

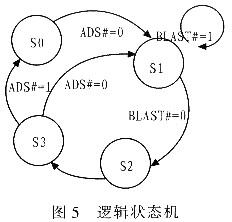

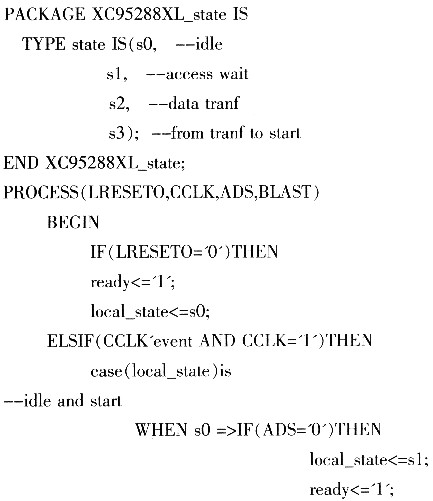

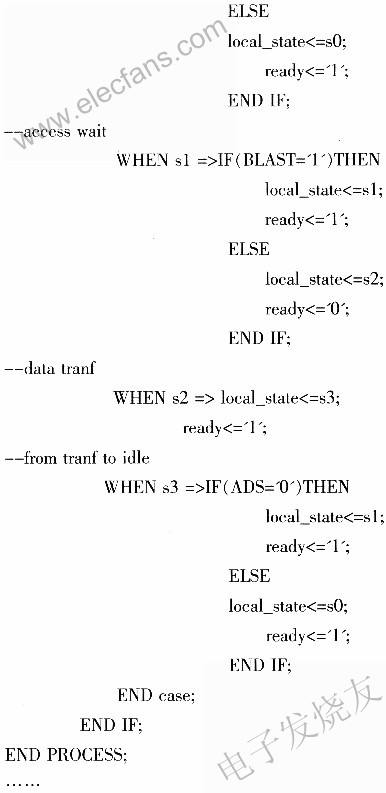

其中單周期訪問本地總線采用狀態機實現本地總線接口的控制,其狀態圖如圖5所示。狀態SO為空閑狀態,當ADS#為0時,如經本地總線譯碼邏輯譯碼后表明需要訪問本地空間時則轉到狀態S1,否則留在狀態SO;狀態S1為單周期訪問開始狀態,當BLAST#為1時,停留在狀態S1,否則轉到狀態S2:狀態S2為訪問等待狀態,在此狀態下數據在本地總線保持,然后直接轉到狀態S3;狀態S3數據傳送狀態,在此狀態下數據從本地總線上取走(如果需要可以加一個狀態來延長數據讀取時間);當ADS#為0時,經本地總線譯碼邏輯譯碼后,表明還需要訪問本地空間,轉到狀態S1,否則轉為SO,本周期訪問結束完成數據傳送。

將以上狀態機用VHDL語言在可編程器件中實現,部分源程序代碼如下:

……

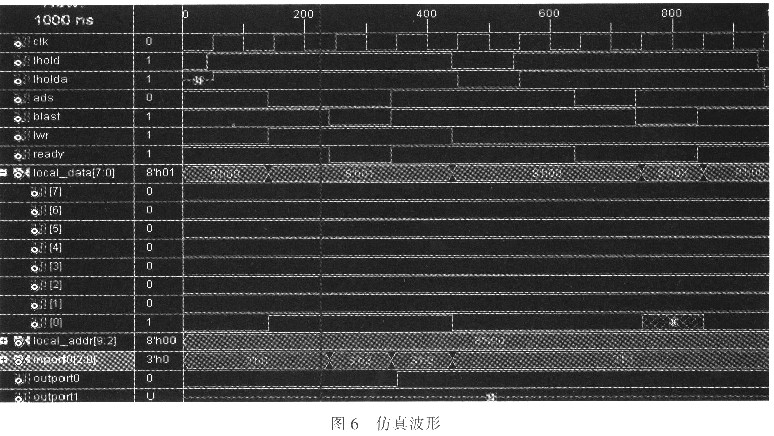

圖6是借助于Xilinx ISE 9.1i仿真工具對在C模式下的8位本地總線寬度的本地邏輯控制的傳輸時序仿真結果舉例。由圖6可知:在寫周期,是把PCI總線端的地址local_adrr[9:2]為8'h00的數據寫到輸出端outport0;在讀周期,是把地址為8'h00的數據從inportO[2;0]讀入到local_data[0]。

3.2 驅動程序設計

Windriver是Jungo公司生產的一個設備驅動程序開發組件,開發者不需熟悉操作系統內核即可利用Windriver開發設備驅動程序。整個驅動程序中的所有函數都是在用戶態下運行的,通過與Windriver的.Vxd或者.Sys文件交互來達到驅動硬件的目的,大大提高了PCI設備驅動程序開發。

用Windriver開發驅動程序的過程大致如下:首先,打開Windriver設備,查找所要訪問的PCI設備;然后是枚舉該設備的資源(包括內存、I/O、中斷)并鎖定該設備的資源,不能被其他程序訪問;在訪問板上的資源之后是解鎖資源;最后是關閉Windriver設備。這個過程是用C語言在VC++6.0開發環境下借助于Windriver本身自帶函數(安裝Windriver之后,在其“Help”中可找出相關函數說明)實現對PCI9054的

初始化。設備打開,訪問硬件資源,調用函數庫,設備關閉等操作后。再對源代碼進行編譯,鏈接和運行成功后,找出產生的5個文件:wdr-eg.exe,plx9054.inf,windrvr6.sys,plx9054.lib和plx9054.dll,這5個文件組成了所需的驅動文件。在板卡成功插入插槽后點擊wdreg.exe成功安裝驅動程序。

4 結束語

本文以性價比較高的PCI9054作為PCI橋路器,給出了橋路器的部分功能介紹、電路設計時需注意的問題及本地總線數據傳輸的接口邏輯設計。本設計降低了PCI總線的復雜性,輕松實現了PCI總線端的控制器對本地總線和本地總線外部設備的工作模式和狀態的有效檢測,具有極大的應用價值。