摘要

本文從總體上介紹HPI(Host Peripheral Interface)接口的工作模式,與上位主機的連接方式,主機訪問的操作流程;歸納了應用當中常見問題,并提供了分析解決辦法。

?

簡介

HPI 接口是TI 為處理器之間直接互連通訊定義的一種異步接口,大多數TI DSP 芯片上都有HPI 接口。HPI 接口是從(Slave)端口,接在主機的擴展內存總線上,DSP 不能通過HPI 向主機(Host)的訪問,只能被主機讀寫。兩個DSP 的HPI 接口之間不能通訊。兩個DSP 之間互連,可以將一個DSP(從)的HPI 接到另一個DSP(主)的擴展內存接口(EMIF)上[1]。

1. HPI工作模式

不同系列DSP 上的HPI 接口版本有所不同,區別體現在DSP 對HPI 的控制上,如C6727 上的UHPI 可通過寄存器使能與關閉HPI 接口,對主機訪問DSP 內存空間的控制,以及對HPI 接口信號的功能復用上。但從主機訪問的角度,HPI 的工作模式分為:復用模式(Multiplexed-Mode)和非復用模式(Non-multiplexed-Mode)。

復用模式下沒有地址線,主機訪問DSP 的地址信息是以數據方式送到HPIA(HPI 地址寄存)。從硬件信號的角度,地址,數據信號是由同一組數據線傳遞,所以稱為復用模式。

非復用模式的數據線與地址線是分開的,與內存接口連接相似。非復用模式不需要操作HPIA 寄存器,主機訪問的地址信息通過地址總線直接送給HPI。

所有的HPI 接口都支持復用模式,但不是所有芯片的HPI 接口都支持非復用模式(參考相應的芯片手冊確定是否支持)。除了有無HPIA 的操作區別外,兩種模式的操作沒有區別。因為非復用模式的操作是復用模式操作的子集,為方便起見,本文以復用模式展開討論。

2. HPI硬件信號連接

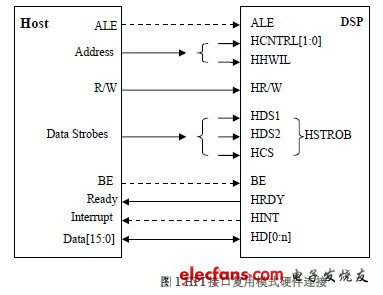

HPI 接口復用模式連線如圖1 所示,根據在應用當中的必要性分為:必要的,和可選的兩組信號。可選的信號

以虛線表示。

?

l? 數據線HD[0:n]:在復用模式下,數據線的寬度一般為CPU 位寬的一半,一個HPI 訪問分為高低半字的兩次訪問,如C5000 是16-bit CPU,HPI 數據線為8 位,C6000 是32-bit CPU,其HPI 數據線為16 位。C64x 系列的HPI 支持32 位,在32 位模式下一個HPI 訪問不需要分為高低半字兩次訪問組成一個完整的訪問。

l? HCNTL0/1,HWIL:HCNTL0/1 選擇要訪問的HPI 寄存器,HWIL 控制訪問寄存器的高低半字,必須先高后低。一個寄存器的高低半字的兩次訪問一定要連續完成,中間不能插入其它的HPI 操作。只有HPIC 可以只訪問半個字。

l? HR/W:指示對HPI 寄存器進行讀,還是寫操作。如果主機的讀,寫信號是分開的,可以利用其中一個信號,但要注意做上拉或下拉處理以控制其在三態時的電平。

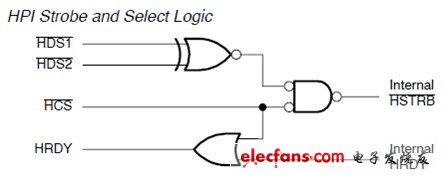

l? HCS,HDS1/2:這三個信號根據圖2 的邏輯產生內部HSTROBE 信號,其邏輯關系是要求HDS1 和HDS2信號相反,HCS 低有效。HSTROB 下降沿的時間點反應的是三個信號中最后跳變的信號。HPI 在HSTROB的下降沿采樣控制信號HR/W,HCNTL0/1,HWIL 以判斷主機要對哪個寄存器進行讀,或者寫操作命令。

?

注意控制信號在HSTROBE 的下降沿之前需要最少5ns 的setup 穩定時間,而HDS1/2 和HCS 到HSTROBE信號內部門電路的延時是皮秒級的,所以控制信號的setup 時間需要外部時序保證。

圖2 HSTROBE信號產生邏輯

?

l? HRDY:HPI 的輸出信號,指示當前操作狀態,用做硬件流量控制握手信號。

l? HINT:通過HPI,主機與DSP 之間可以互發中斷。HINT 是HPI 送給主機的中斷信號,DSP 對HPIC[HINT]位寫1,HINT 信號線上送出高電平信號,主機可利用此信號做為中斷信號輸入。DSP 不能清除HPIC[HINT]狀態,主機在響應中斷后,需要對HPIC[HINT]位寫1 清除狀態,DSP 才能再次對HPIC[HINT]置位發中斷。主機通過寫HPIC[DSPINT]置1 給DSP 產生中斷,DSP 在響應中斷后,需要對HPIC[DSPINT]寫1 清除狀態,主機才能繼續操作HPIC[DSPINT]給DSP 發中斷。通過HPI 傳輸數據,結合互發中斷做為軟件層的握手信號,可有效提高通訊的效率與靈活性。

l? ALE:存在于地址,數據線復用的主機上用來指示地址信號周期,這種總線復用的主機很少見,所以通常將ALE 固定上拉處理,只用HSTROBE 采樣控制信號。

l? BE:Byte Enable 信號,這個信號只出現在32 位的C6000 DSP 上。因為應用當中通常都是對整個32-bit 字進行訪問,所以直接做上拉使能處理。

3. HPI寄存器地址映射

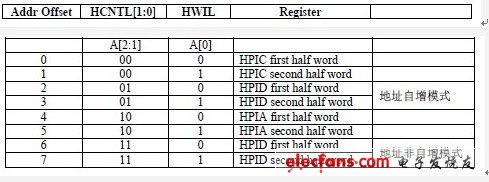

HPI 口提供給主機端訪問的寄存器只有4個,通過HCNTL[1:0]選擇.

表1 HPI寄存器訪問選擇

由于在復用模式下數據線通常只有寄存器寬度的一半,所以一個完整的數據訪問由高低半字兩次訪問組成,由HWIL 信號控制,HWIL 信號必須是先低后高。通常將HWIL 和HCNTL[1:0]接在主機的地址線上,將4 個寄存器映射為主機端的8 個內存單元,下表中的地址線連接方法將8 半字寄存器映射到主機的8 個連續的內存單元。這里的地址線是用來選擇HPI 的寄存器,與非復用模式下的地址線直接訪問DSP 的內存空間是完全不同的作用。

?

表2 HPI寄存器地址映射

4. HPI寄存器功能說明

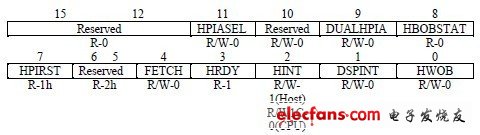

HPIC (HPI Control Register)

HPI 控制寄存器HPIC 的位圖如表3 所示,C6000 系列DSP 的HPI 寄存器是32 位的,也只有低16 位有效,與C5000 系列DSP 的HPIC 寄存器定義的功能保持一致。不同版本的HPI 接口的HPIC 位定義的主要不同之處在于軟件握手HRDY 位的有無,其它位名稱可能存在細小差異,但功能定義都是一樣的。

表3 HPI Control Register

主機在對HPI 進行訪問前可以通過HPIC 配置字節序(HWOB)和地址寄存器模式(DUALHPIA)。默認的配置為HWOB=0,即先訪問高半;DUALHPIA=0,即單地址寄存器模式,讀和寫操作使用同一個HPIA;通常都采用默認的HPIC 寄存器配置。

HWOB 與硬件信號HWIL 是沒有聯系的,HWIL 信號必須保證先低后高分別訪問兩個半字單元。至于先訪問一個字當中的高或低半字,是由HWOB 控制的。

?

HPIA (HPI Address Register)

物理上存在HPIAR,HPIAW 兩個地址寄存器。HPIAR 是讀操作地址寄存器;HPIAW 是寫操作地址寄存器。由HPIC 的DUALHPIA 位來決定是采用雙地址寄存器模式還是單地址寄存器模式。如果采用雙地址寄存器模式,在對HPIA 操作之前,通過設置HPIC 的HPISEL 位選擇下一個要訪問的HPIA。通常為了簡化在讀寫操作轉換時對HPIC 的操作,選用單地址寄存器模式。

HPIA 的地址信息在不同系列DSP 上有所不同:

在C5000 上,數據空間,I/O 空間只能按16 位字尋址,程序空間按字節尋址。HPI 的DMA 訪問屬于I/O 空間,HPIA 的值代表16 位字地址。如主機端要訪問DSP 內存字節地址0x100, 則要往HPIA 寫的地址值是0x80。在用HPI 啟動時,要注意DSP 代碼是按字節地址鏈接的,即代碼段的地址是字節地址,主機端要將代碼段的地址信息除以2 再送到HPIA。

在C64 上,HPIA 的值代表字節地址,但是HPI 訪問的數據是32 位的,所以HPI 會忽略HPIA 地址值的低兩位。

在C64+的DSP 上,HPIA 代表32 位字地址,HPI 會將字地址左移兩位轉換成字節地址,主機若要訪問DSP 字節地址0x100,則要賦值HPIA 為0x40。

?

HPID (HPI Data Register)

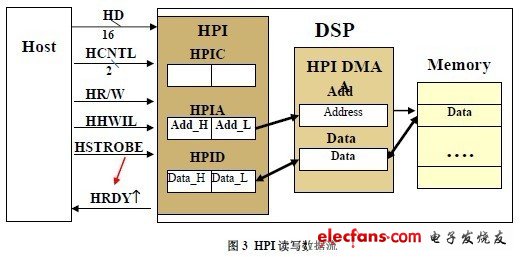

主機通過HPI 對DSP 的內存訪問是間接訪問,主機只能訪問HPID,HPID 與DSP 內存之間是通過HPI 專屬的DMA 進行數據搬運的。如圖3 所示。

HPID 的訪問分為自增模式和非自增模式。在自增模式下,訪問HPID 后,HPIA 會自動增加指向下一個字地址,在連續訪問時,自增模式因為減少了主機對HPIA 的操作,可以增加HPI 數據訪問的吞吐率。非自增模式下訪問HPID 后,HPIA 的值保持不變,主機需要更新HPIA 來訪問下一個地址。

在寫操作時,主機把數據寫到HPID,HPI 將第二個半字的數據通過HSTROBE 的上升沿鎖存到HPID 后,將HRDY 置為忙狀態,并啟動HPI DMA 將HPID 的內容搬到HPIA 所指向的內存單元,然后清除HRDY 指示可以進行下一次操作。

在讀操作時,在第一個HSTROBE 的下降沿,HPI 采樣到HR/W為讀命令,則將HRDY 置為忙狀態,啟動HPIDMA 將HPIA 指向的內存單元的數據搬到HPID,清除HRDY 忙狀態,主機端方可結束總線訪問周期,鎖存數據線上的有效數據。

5. HPI操作流程

主機對HPI 的一次總線訪問周期為分三個階段:主機發起訪問,HPI 響應,主機結束訪問周期。

A.??? 主機發起訪問:即對HPI 寄存器的讀,或者寫命令。主機送出的硬件信號為HSTROBE(由HCS, HDS1/2產生),HR/W,HCNTL0/1,HWIL,以及HD[0:n]。HPI 在HSTROBE 的下降沿采樣控制信號HR/W,HCNTL0/1,HWIL 判斷主機的操作命令。

B.??? HPI 響應:HPI 在HSTROBE 的下降沿采樣控制信號,根據控制信號做出相應的響應。如果是寫(HR/W為低)命令,則在HSTROBE 的上升沿將數據線上的信號鎖存到HCNTL0/1 和HWIL 指向的寄存器。如果是讀命令(HR/W 為高),如果是讀HPIC,或者HPIA 寄存器,HPI 將寄存器的值直接送到數據總線上;如果讀HPID,HPI 先將HRDY 置為忙狀態,HPI DMA 將數據從HPIA 指向的內存單元讀到HPID,再送到數據線上,并清除HRDY 忙狀態,在讀HPID 后半字時,數據從寄存器直接送到數據總線上,不會出現HRDY 信號忙狀態。

C.??? 主機結束訪問周期:對于寫操作,主機將數據送出后,只要滿足芯片手冊中HPI 對HCS 的最小寬度要求,即可結束訪問周期。對于讀HPID 操作,要等HRDY 信號由忙變為不忙,主機才能結束訪問周期。兩次連續的HPI 操作的間隔,在芯片手冊的HPI 時序參數表里有要求,最小間隔為兩個HPI 功能模塊時鐘周期。

6. HPI常見故障案例分析

在HPI 應用調試過程中,常遇到的問題分為:寫數據不成功,讀數據不正確,HRDY 常高。這些問題通常都是由于時序不正確造成的,下面結合實際應用當中的案例進行分析。

1.1寫數據不成功

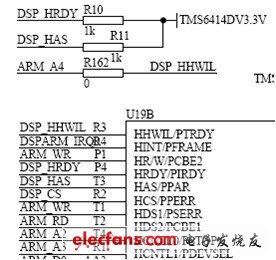

案例的硬件連接如下:

首先關注核心信號HSTROBE 由DSP_CS,ARM_WR(HDS1),ARM_RD(HDS2)產生,從下面時序圖可以看出ARM_WR 的下降沿是最后產生的,所以寫操作時HSTROBE 的下降沿反應的是ARM_WR 的下降沿。

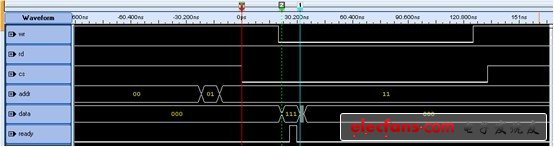

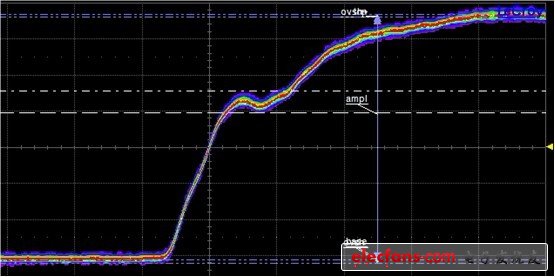

寫HPIC 的時序截圖如下:

寫HPID 的時序截圖如下:

兩個時序圖顯示主機送出的數據111b 在HSTROBE(ARM_WR)的下降沿后,很快被改變成其它值000b。在寫HPID 的時序截圖中,第一個HSTROBE 的下降后,HPI 送出HRDY 信號,然后數據線被改變,首先判斷HPI 對主機的命令做出了響應,通過HRDY 信號的出現時機,說明HPI 判斷這是一個讀操作,可以判斷為HSTROBE 的下降沿采樣HR/W信號不正確。

從硬件連接來看,HSTROBE(HR/W)要采樣HR/W,HCNTL0/1 來判斷主機命令, HR/W的與HSTROBE 為同一信號源,且同為下降沿,HR/W與HSTROBE 的下降沿之間的setup 時間不夠,采樣HR/W的電平狀態出現誤判,認為是高電平讀命令,HPI 對讀命令的響應則是在第一個HSTROBE 的下降沿之后送出HRDY 信號,并在HRDY 之后,HPI 送出數據到總線上。

對于該問題,需要對參與HSTROBE 邏輯譯碼的HR/W信號的下降沿做延時處理,可在邏輯電路如CPLD 或 FPGA 里實現,以確保HSTROBE 的下降沿采樣到穩定的HR/W電平。

?

1.2讀數據不正確

通常表現為讀讀HPIC,HPIA 正常,但讀HPID 不正常,前半字為0,后半字正確,對同一個地址讀兩次,第二次的數據完全正確。

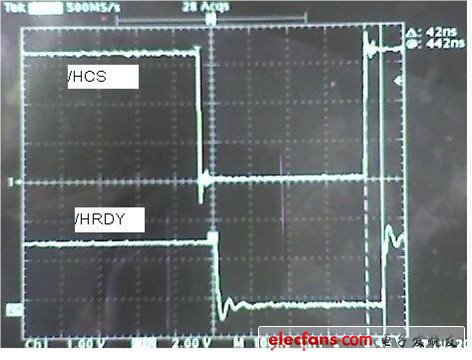

在案例中,用示波器觀察HCS 與HRDY 之間的時序關系,發現HCS 的上升沿在HRDY 的上升沿之前,即主機在HPI 數據有效之前結束了訪問周期。HRDY 的上升沿其實是因為HCS 的結束而拉高的,并非數據真正有效。

用戶由于沒有在硬件上將HRDY 與主機PowerPC 的TA 信號互連,沒有硬件握手機制,于是從軟件配置上加大主機的總線訪問周期,即增加HCS 的寬度,故障現象沒有變化。

原因分析:讀HPID 與HPIC,HPIA 時序不同,讀HPID 操作需要HPI DMA 從HPIA 所指向的地址讀數據到 HPID,會有時間上的延時。而讀HPIC 和HPIA 直接從寄存器讀數據,沒有延時,所以讀HPIC,HPIA 是正確的。在讀HPID 時,HPI 會在第一個HSTROBE 的下降沿后將HRDY 置位,指示數據未準備好的忙狀態,主機應當在總線上插入等待周期,數據準備好后HPI 清除HRDY,主機才可以結束總線周期,通過HCS 的上升沿將有效數據鎖存。

HSTROBE 的下降沿到數據有效之間的延時與芯片及HPI 接口的工作頻率相關,以C5502,C5501 為例,在芯片手冊中,這個延時參數H1 在SYSCLK1 與CPU 時鐘的分頻為4 時,最大延時為12*2H+20(ns),H=SYSCLK1/2,在HPI 啟動期間,PLL 沒有倍頻,處于旁通狀態,系統輸入時鐘就是CPU 的工作時鐘,SYSCLK1默認分頻為CPU 時鐘的4 分頻,以輸入時鐘為25MHz 為例,最大延時為:

這個時間長度通常超出了主機端總線周期的軟件配置范圍,所以通過軟件配置增加HCS 的寬度不一定能滿足 HRDY 的最大延時要求。在有的DSP 芯片手冊上只提供了HRDY 的最小延時,最大延時與芯片的優先級設置,及系統配置相關而不確定,比如與系統中其它主模塊如EDMA 同時訪問DDR,那么延時與HPI 的優先級,EDMA 的優先級,EDMA 的burst 長度,以及DDR 的命令排序等配置相關,這樣通過延長主機的總線訪問周期,更加不可靠。

解決辦法:在硬件設計之初,一定要利用HRDY 硬件握手信號[2][3]。雖然有的芯片HPIC 寄存器提供了HRDY 軟件握手方式,只能做為彌補硬件設計之初遺漏HRDY 硬件握手信號的權宜之計,軟件輪循HRDY 的辦法會帶來額外的開銷,降低HPI 總線的吞吐率,增加主機軟件實現的復雜度。而且有的芯片HPI 不支持HRDY 軟件查詢方法,只能通過硬件HRDY 保證數據的有效性。

?

1.3 HRDY常高

有的系統在長時間運行中偶爾出現HRDY 常高,導致主機端總線訪問異常,需要重新上電才能恢復HPI 的正常操作。這種故障是由于HPI 狀態機出現異常。

從實際故障定位中總結出以下幾點原因:

A.??? HPI 的高低半字訪問的順序訪問被其它HPI 訪問打斷:在復用模式下,一個完整的HPI 訪問是由高低半字兩次訪問組成,需要嚴格保證,否則會破壞HPI 的狀態機,從而導致不可預期的后果。

B.??? 主機通過HPI 訪問了DSP 內部的保留空間,或者破壞了DSP 的程序,數據空間,導致DSP 運行異常,進而導致HPI 狀態機異常。

C.??? 主機的HSTROBE 信號有毛刺,或者信號完整性不好,如下圖中HCS(些案例HSTROBE 是由HCS 控制)的上升沿的回勾,都會導致HPI 誤判斷為主機的新的訪問的開始,從而打亂了高低半字的訪問順序要求,導致HPI 狀態機的錯亂。

7.總結

HPI 是一種簡單的異步接口,只要設計中滿足了時序要求,即可穩定工作。在開發當中遇到數據讀寫不正確,從HSTROBE 信號入手檢查與之相關的信號的時序關系,便可以找出問題原因。另外,信號完整性是任何系統穩定工作的前提。

關于特定芯片上HPI 接口的特有功能本文沒有針對討論,如C6727 的字地址模式和字節地址模式可通過HPIC配置;C6727 在HPI 啟動后ROM bootloader 將HPI 關閉,需要軟件重新使能才能使用等;以及不同芯片的HPI 啟動模式下的跳轉方式不同,請參考相應芯片的HPI 手冊及bootloader 應用手冊。