0、引言

CD4017C集成電路應用非常廣泛,但大多資料對其內部電路邏輯功能的推導卻是輕描淡寫,甚至不乏錯誤之處,文中通過約翰遜計數器32種隨機輸出碼狀態轉換的邏輯計算和分析,對CD4017C集成電路內部邏輯電路的結構、原理作了深入詳細的闡述。

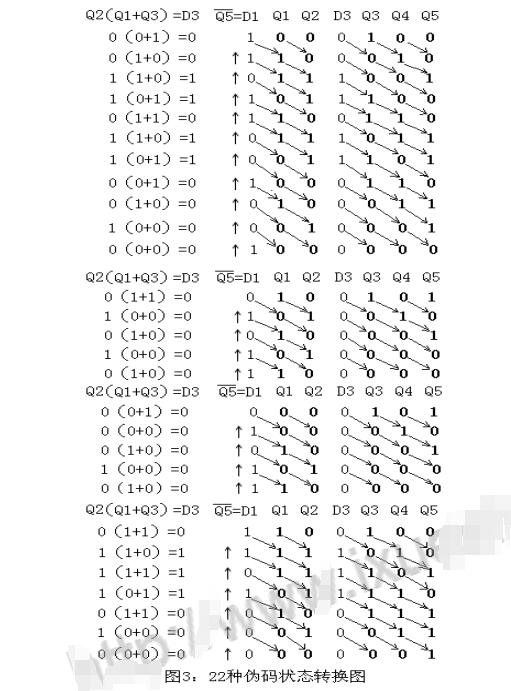

1、CD4017C集成電路的引腳功能(見圖1)

CD4017C集成電路共有11個輸出端:3腳(Y0)、2腳(Y1)、4腳(Y2)、7腳(Y3)、10腳(Y4)、1腳(Y5)、5腳(Y6)、6腳(Y7)、9腳(Y8)、11腳(Y9)分別為第0~第9輸出端;12腳(Qco)為級聯進位輸出端。3個輸入端:13腳(EN)為時鐘脈沖輸入端,下降沿計數有效;14腳(CP)為時鐘脈沖輸入端,上升沿計數有效;15腳(R)為復位清零輸入端,加高電平或正脈沖時計數器清零。2個供電端:8腳(Vss)為電源負端;16腳(VDD)為電源正端3~18V。

2、十進制約翰遜計數器電路分析(見圖1)

十進制約翰遜計數器實質上是一種串行移位寄存器,由D觸發器Fl~F5構成,除了第3個觸發器是通過組合邏輯電路作用于F3的D3端以外,其余各級均是將前一級觸發器的輸出端Q連接到后一級觸發器的輸入端D的,計數器最后—級F5的 端連接到第一級的D1端。當加上清零脈沖后,Q1~Q5均為“0”,由于Q1的數據輸入端D1是Q5輸出的反碼

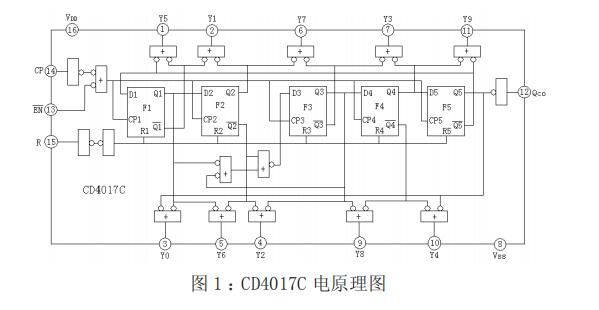

端連接到第一級的D1端。當加上清零脈沖后,Q1~Q5均為“0”,由于Q1的數據輸入端D1是Q5輸出的反碼 ,因此,輸入第—個時鐘脈沖后,Q1即為“l”,這時Q2-Q5均依次進行移位輸出,Ql的輸出移至Q2,Q2的輸出需經組合邏輯電路轉化成D3后才能移至Q3,Q3的輸出移至Q4,Q4的輸出移至Q5,Q5的輸出被移出(溢出),如果繼續輸入脈沖,則Q1為新的

,因此,輸入第—個時鐘脈沖后,Q1即為“l”,這時Q2-Q5均依次進行移位輸出,Ql的輸出移至Q2,Q2的輸出需經組合邏輯電路轉化成D3后才能移至Q3,Q3的輸出移至Q4,Q4的輸出移至Q5,Q5的輸出被移出(溢出),如果繼續輸入脈沖,則Q1為新的 ,Q2~Q5仍然依次按上述規律移位輸出,從而導出十進制計數循環狀態(見圖2),這就是我們所需十進制計數循環的10種狀態。

,Q2~Q5仍然依次按上述規律移位輸出,從而導出十進制計數循環狀態(見圖2),這就是我們所需十進制計數循環的10種狀態。

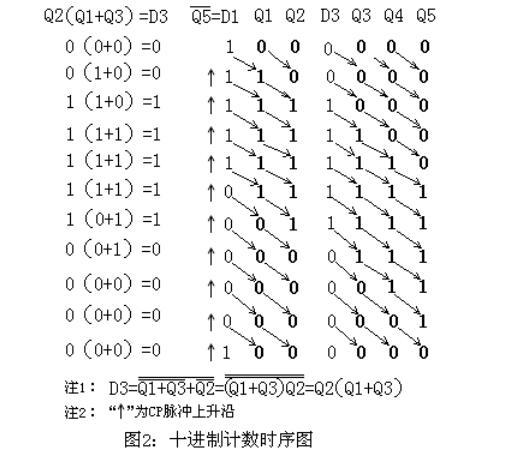

然而由五級計數單元組成的約翰遜計數器,其輸出端可以有 =32種組合狀態,而構成十進制計數器只需10種計數狀態,因此,當電路接通電源之后,有可能進入我們所不需要的22種偽碼狀態中的任一狀態,并伴隨觸發脈沖上升沿的出現自動進行移位寄存(見圖3)

=32種組合狀態,而構成十進制計數器只需10種計數狀態,因此,當電路接通電源之后,有可能進入我們所不需要的22種偽碼狀態中的任一狀態,并伴隨觸發脈沖上升沿的出現自動進行移位寄存(見圖3)