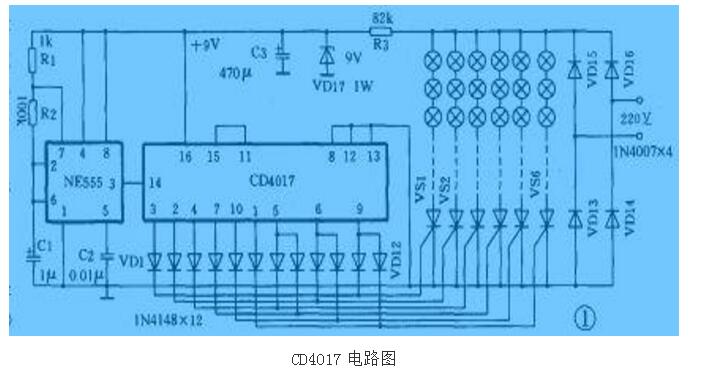

CD4017內部結構圖 - cd4017工作原理詳解(cd4017引腳圖及功能_內部結構及應用電路圖)

CD4017內部結構圖

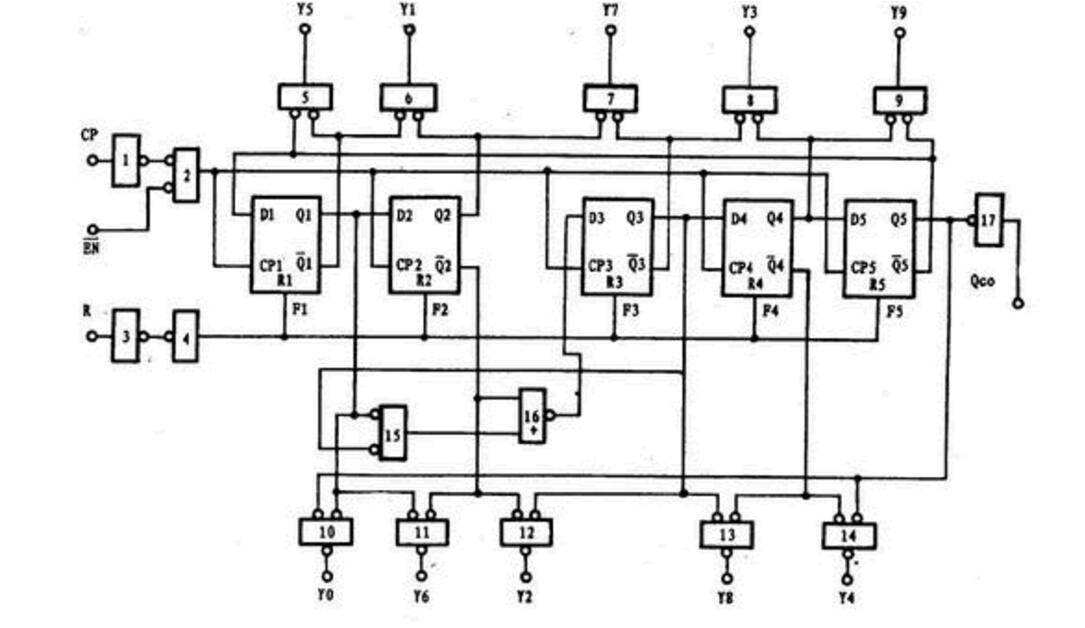

圖 2 CD4017 內部邏輯電原理圖

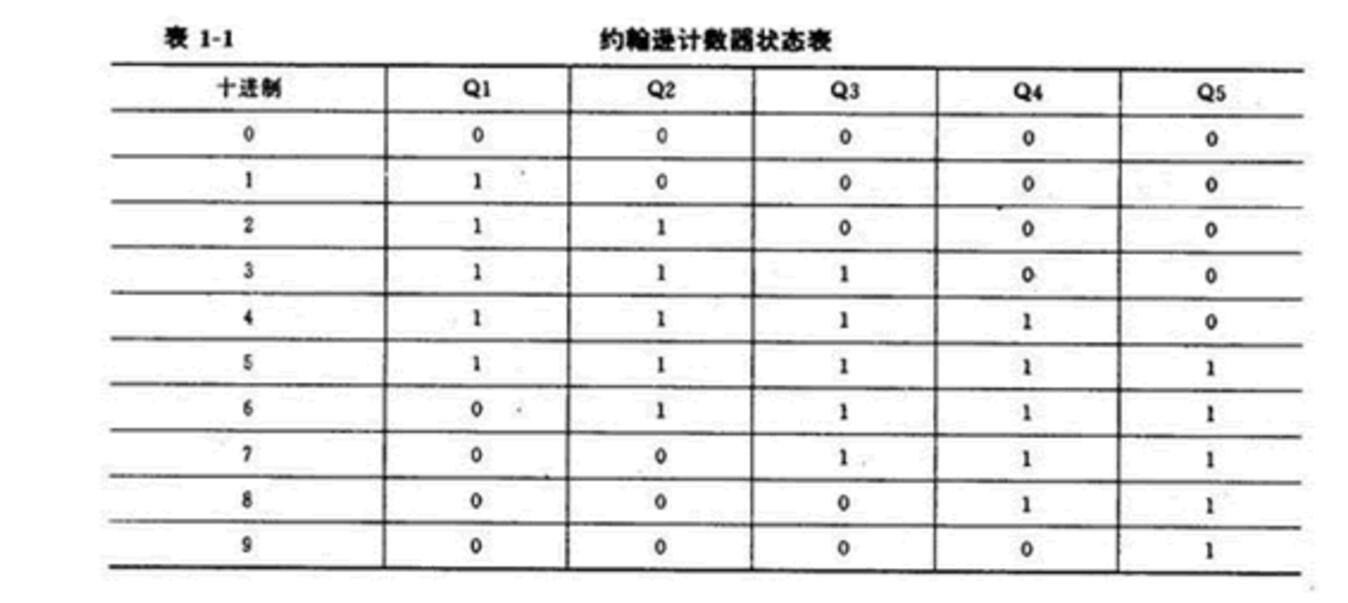

CD4017內部邏輯電原理圖如圖2所示。它是由十進制計數器電路和時序譯碼電路兩部分組成。其中的D觸發器Fl~F5構成了十進制約翰遜計數器,門電路5~14 構成了時序譯碼電路。約翰遜計數器的結構比較簡單.它實質上是一種串行移位寄存器。除了第3個觸發器是通過門電路15、16構成的組合邏輯電路作用于F3的D3端以外,其余各級均是將前一級觸發器的輸出端連接到后一級觸發器的輸入端D的,計數器最后—級的Q5端連接到第一級的D1端。這種計數器具有編碼可靠,工作速度快、譯碼簡單,只需由二輸入瑞的與門即可譯碼,且譯碼輸出無過渡脈沖干擾等特點。通常只有譯碼選中的那個輸出端為高電平,其余輸出端均為低電平。約翰遜計數器狀態如表1-1所示。

當加上清零脈沖后,Q1~Q5均“0”,由于Q1的數據輸入端D1是Q5輸出的反碼,因此,輸入第—個時鐘脈沖后,Q1即為“l”,這時Q2-Q5均依次進行移位輸出,Ql的輸出移至Q2,Q2的輸出移至Q3……。如果繼續輸入脈沖,則Q1為新的Q5,Q2~Q5仍然依次移位輸出,這樣就得到了表l~l的狀態及圖l~3的波形

由五級計數單元組成的約翰遜計數器,其輸出端可以有32種組合狀態,而構成十進制計數器只需10種計數狀態,因此,當電路接通電源之后,有可能進入我們所不需要的22種偽碼狀態。

為了使電路能迅速進入表1~l所列狀態,就在第三級計數單元的數據輸入端上加接了兩級組合邏輯門,使Q2不直接連接D3,而使03由下列關系決定:

D3=Q2(Ql+Q3)

這樣做,當電源接通后,不管計數單元出現哪種隨機組合,最多經過8個時鐘脈沖輸入之后,都會自動進入表l~l所列狀態。

CD4017有3個輸入端:復位清零端R,當在R端加高電平或正脈沖時,計數器清零,在所有輸出中,只有對應“0”狀態的Q0輸出高電平,其余輸出均為低電平:時鐘輸入端CP和CE,其中CP端用于上升沿計數,CE端用于下降沿計數,這兩個輸入端的內部邏輯電路如圖2所示。由圖2可見,CP和CE還有互鎖的關系,即利用CP計數時,CE端要接低電平:利用CE計數時,CP端要接高電平。反之則形成互鎖。

在“R”端加上高電平或正脈沖日子,計數器中各計數單元F1~F5均被置零,計數器為“00000”狀態。

CD4017有10個譯碼輸出端Q0~Q9,它仍隨時鐘脈沖的輸入而依次出現高電平,見圖3。此外,為了級聯方便,還設有進位輸出端QC,每輸入10個時鐘脈沖,就可得到一個進位輸出脈沖,所以QC可作為下一級計數器的時鐘信號。

從上述分析中可以看出,CD4017(它的基本功能是對“CP”端輸入脈沖的個數進行十進制計數,并按照輸入脈沖的個數順序將脈沖分配在Yo—Y9這十個輸出端,計滿十個數后計數器復零,同時輸出—個進位脈沖。我們只要掌握了這些基本功能就能設計出千姿百態的應用電路來。

- 第 1 頁:cd4017工作原理詳解(cd4017引腳圖及功能_內部結構及應用電路圖)

- 第 2 頁:CD4017內部結構圖

- 第 3 頁:用三個CD4O17彩燈電路圖

本文導航

非常好我支持^.^

(911) 93.3%

不好我反對

(65) 6.7%

相關閱讀:

- [電子說] 使用NE555和CD4017制作一個迪斯科LED燈電路 2023-07-05

- [電子說] 基于IC555和CD4017的雙色迪斯科燈電路 2023-07-02

- [電子說] 基于CD4017的電子骰子電路 2023-06-29

- [電子說] 基于CD4017構建的簡單密碼鎖電路 2023-06-29

- [電子說] 怎么去設計一種基于模擬電路的跑馬燈電路呢? 2023-06-11

- [電子說] 如何使用LDR和CD4017制作無線網絡 2022-11-22

- [電子說] 基于555定時器和CD4017的分頻器電路 2022-11-22

- [電子說] CD4017十進制計數器的基本概念及應用電路 2022-10-31

( 發表人:姚遠香 )