8086概述

Intel8086擁有四個16位的通用寄存器,也能夠當(dāng)作八個8位寄存器來存取,以及四個16位索引寄存器(包含了堆棧指標(biāo))。資料寄存器通常由指令隱含地使用,針對暫存值需要復(fù)雜的寄存器配置。它提供64K8位元的輸出輸入(或32K16位元),以及固定的向量中斷。大部分的指令只能夠存取一個內(nèi)存位址,所以其中一個操作數(shù)必須是一個寄存器。運算結(jié)果會儲存在操作數(shù)中的一個寄存器。

Intel8086有四個內(nèi)存區(qū)段(segment)寄存器,可以從索引寄存器來設(shè)定。區(qū)段寄存器可以讓CPU利用特殊的方式存取1MB內(nèi)存。8086把段地址左移4位然后把它加上偏移地址。大部分的人都認(rèn)為這是一個很不好的設(shè)計,因為這樣的結(jié)果是會讓各分段有重疊。盡管這樣對組合語言而言大部分被接受(也甚至有用),可以完全地控制分段,使在編程中使用指針(如C編程語言)變得困難。它導(dǎo)致指針的高效率表示變得困難,且有可能產(chǎn)生兩個指向同一個地方的指針擁有不同的地址。更壞的是,這種方式產(chǎn)生要讓內(nèi)存擴(kuò)充到大于1MB的困難。而8086的尋址方式改變讓內(nèi)存擴(kuò)充較有效率。

8086處理器的時鐘頻率介于4.77MHz(在原先的IBMPC頻率)和10MHz之間。8086沒有包含浮點指令部分(FPU),但是可以通過外接數(shù)學(xué)輔助處理器來增強(qiáng)浮點計算能力。Intel8087是標(biāo)準(zhǔn)版本。

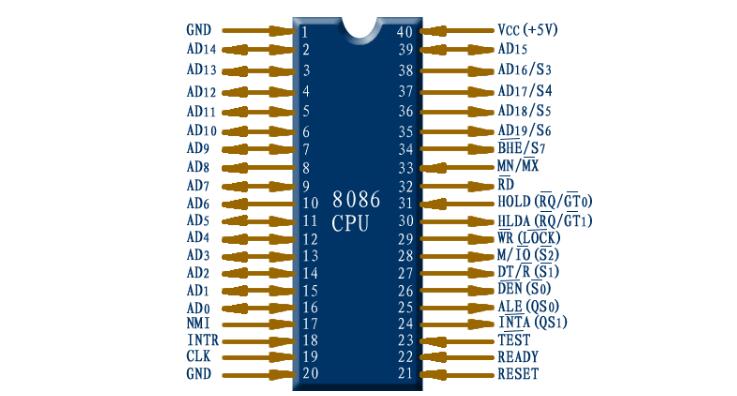

8086引腳圖及功能

⑴AD15~AD0(addressdatabus):地址/數(shù)據(jù)總線,雙向,三態(tài)。

這是一組采用分時的方法傳送地址或數(shù)據(jù)的復(fù)用引腳。根據(jù)不同時鐘周期的要求,決定當(dāng)前是傳送要訪問的存儲單元或I/O端口的低16位地址,還是傳送16位數(shù)據(jù),或是處于高阻狀態(tài)。

⑵A19/S6~A16/S3(address/status):地址/狀態(tài)信號,輸出,三態(tài)。

這是采用分時的方法傳送地址或狀態(tài)的復(fù)用引腳。其中A19~A16為20位地址總線的高4位地址,S6~S3是狀態(tài)信號。S6表示CPU與總線連接的情況,S5指示當(dāng)前中斷允許標(biāo)志IF的狀態(tài)。S4,S3的代碼組合用來指明當(dāng)前正在使用的段寄存器。S4,S3的代碼組合及對應(yīng)段寄存器的情況。

⑶BHE(低)/S7(bushighenable/status):允許總線高8位數(shù)據(jù)傳送/狀態(tài)信號,輸出,三態(tài)。

為總線高8位數(shù)據(jù)允許信號,當(dāng)?shù)碗娖接行r,表明在高8位數(shù)據(jù)總線D15~D8上傳送1個字節(jié)的數(shù)據(jù)。S7為設(shè)備的狀態(tài)信號。

⑷RD/(read):讀信號,輸出,三態(tài),低電平有效。

信號低電平有效時,表示CPU正在進(jìn)行讀存儲器或讀I/O端口的操作。

⑸READY(ready):準(zhǔn)備就緒信號,輸入,高電平有效。

READY信號用來實現(xiàn)CPU與存儲器或I/O端口之間的時序匹配。當(dāng)READY信號高電平有效時,表示CPU要訪問的存儲器或I/O端口已經(jīng)作好了輸入/輸出數(shù)據(jù)的準(zhǔn)備工作,CPU可以進(jìn)行讀/寫操作。當(dāng)READY信號為低電平時,則表示存儲器或I/O端口還未準(zhǔn)備就緒,CPU需要插入若干個“TW狀態(tài)”進(jìn)行等待。

⑹INTR(interruptrequest):可屏蔽中斷請求信號,輸入,高電平有效。

8086CPU在每條指令執(zhí)行到最后一個時鐘周期時,都要檢測INTR引腳信號。INTR為高電平時,表明有I/O設(shè)備向CPU申請中斷,若IF=1,CPU則會響應(yīng)中斷,停止當(dāng)前的操作,為申請中斷的I/O設(shè)備服務(wù)。

⑺TEST/(test):等待測試控制信號,輸入,低電平有效。

信號用來支持構(gòu)成多處理器系統(tǒng),實現(xiàn)8086CPU與協(xié)處理器之間同步協(xié)調(diào)的功能,只有當(dāng)CPU執(zhí)行WAIT指令時才使用。

⑻N(yùn)MI(non-maskableinterrupt):非屏蔽中斷請求信號,輸入,高電平有效。

當(dāng)NMI引腳上有一個上升沿有效的觸發(fā)信號時,表明CPU內(nèi)部或I/O設(shè)備提出了非屏蔽的中斷請求,CPU會在結(jié)束當(dāng)前所執(zhí)行的指令后,立即響應(yīng)中斷請求。

⑼RESET(reset):復(fù)位信號,輸入,高電平有效。

RESET信號有效時,CPU立即結(jié)束現(xiàn)行操作,處于復(fù)位狀態(tài),初始化所有的內(nèi)部寄存器。復(fù)位后各內(nèi)部寄存器的狀態(tài),當(dāng)RESET信號由高電平變?yōu)榈碗娖綍r,CPU從FFFF0H地址開始重新啟動執(zhí)行程序。

⑽CLK(clock):時鐘信號,輸入。

CLK為CPU提供基本的定時脈沖信號。8086CPU一般使用時鐘發(fā)生器8284A來產(chǎn)生時鐘信號,時鐘頻率為5MHz~8MHz,占空比為1:3。

⑾VCC電源輸入引腳。

8086CPU采用單一+5V電源供電。

⑿GND:接地引腳。

⒀MN/MX/(minimum/maximum):最小/最大模式輸入控制信號。

引腳用來設(shè)置8086CPU的工作模式。當(dāng)為高電平(接+5V)時,CPU工作在最小模式;當(dāng)為低電平(接地)時,CPU工作在最大模式。

CPU工作于最小模式時使用的引腳信號

當(dāng)引腳接高電平時,CPU工作于最小模式。此時,引腳信號24~31的含義及其功能如下。

⑴M/IO/(memoryI/Oselect):存儲器、I/O端口選擇控制信號。

信號指明當(dāng)前CPU是選擇訪問存儲器還是訪問I/O端口。為高電平時,訪問存儲器,表示當(dāng)前要進(jìn)行CPU與存儲器之間的數(shù)據(jù)傳送。為低電平時,訪問I/O端口,表示當(dāng)前要進(jìn)行CPU與I/O端口之間的數(shù)據(jù)傳送。

⑵WR/(write):寫信號,輸出,低電平有效。

信號有效時,表明CPU正在執(zhí)行寫總線周期,同時由信號決定是對存儲器還是對I/O端口執(zhí)行寫操作。

⑶INTA/(interruptacknowledge):可屏蔽中斷響應(yīng)信號,輸出,低電平有效。

CPU通過信號對外設(shè)提出的可屏蔽中斷請求做出響應(yīng)。為低電平時,表示CPU已經(jīng)響應(yīng)外設(shè)的中斷請求,即將執(zhí)行中斷服務(wù)程序。

⑷ALE(addresslockenable):地址鎖存允許信號,輸出,高電平有效。

CPU利用ALE信號可以把AD15~AD0地址/數(shù)據(jù)、A19/S6~A16/S3地址/狀態(tài)線上的地址信息鎖存在地址鎖存器中。

⑸DT/(datatransmitorreceive):數(shù)據(jù)發(fā)送/接收信號,輸出,三態(tài)。

DT/信號用來控制數(shù)據(jù)傳送的方向。DT/為高電平時,CPU發(fā)送數(shù)據(jù)到存儲器或I/O端口;DT/為低電平時,CPU接收來自存儲器或I/O端口的數(shù)據(jù)。⑹DEN/(dataenable):數(shù)據(jù)允許控制信號,輸出,三態(tài),低電平有效。

信號用作總線收發(fā)器的選通控制信號。當(dāng)為低電平時,表明CPU進(jìn)行數(shù)據(jù)的讀/寫操作。

⑺HOLD(busholdrequest):總線保持請求信號,輸入,高電平有效。

在DMA數(shù)據(jù)傳送方式中,由總線控制器8237A發(fā)出一個高電平有效的總線請求信號,通過HOLD引腳輸入到CPU,請求CPU讓出總線控制權(quán)。

⑻HLDA(holdacknowledge):總線保持響應(yīng)信號,輸出,高電平有效。

HLDA是與HOLD配合使用的聯(lián)絡(luò)信號。在HLDA有效期間,HLDA引腳輸出一個高電平有效的響應(yīng)信號,同時總線將處于浮空狀態(tài),CPU讓出對總線的控制權(quán),將其交付給申請使用總線的8237A控制器使用,總線使用完后,會使HOLD信號變?yōu)榈碗娖剑珻PU又重新獲得對總線的控制權(quán)。

CPU工作于最大模式時使用的引腳信號

當(dāng)引腳接低電平時,CPU工作于最大模式。此時,引腳信號24~31的含義及其功能如下。

⑴S2,S1,S0(statussignals):總線周期狀態(tài)信號,輸出,低電平有效。

⑵RQ/,GT/(request/grant):總線請求允許信號輸入/總線請求允許輸出信號,雙向,低電平有效。

該信號用以取代最小模式時的HOLD/HLDA兩個信號的功能,是特意為多處理器系統(tǒng)而設(shè)計的。當(dāng)系統(tǒng)中某一部件要求獲得總線控制權(quán)時,就通過此信號線向8086CPU發(fā)出總線請求信號,若CPU響應(yīng)總線請求,就通過同一引腳發(fā)回響應(yīng)信號,允許總線請求,表明8086CPU已放棄對總線的控制權(quán),將總線控制權(quán)交給提出總線請求的部件使用。RQ/GT0優(yōu)先級高于RQ/GT1。

⑶LOCK/(lock)總線封鎖信號,輸出,低電平有效。

信號有效時,表示此時8086CPU不允許其他總線部件占用總線。

⑷QS1,QS0(queuestatus):指令隊列狀態(tài)信號,輸出。

QS1和QS0信號的組合可以指示總線接口部件BIU中指令隊列的狀態(tài),以便其他處理器監(jiān)視、跟蹤指令隊列的狀態(tài)。