74LS273是8位數(shù)據(jù)/地址鎖存器,它是一種帶清除功能的8D觸發(fā)器,D0~D7為數(shù)據(jù)輸入端,Q0~Q7為數(shù)據(jù)輸出端,正脈沖觸發(fā),低電平清除,常用作數(shù)據(jù)鎖存器,地址鎖存器。

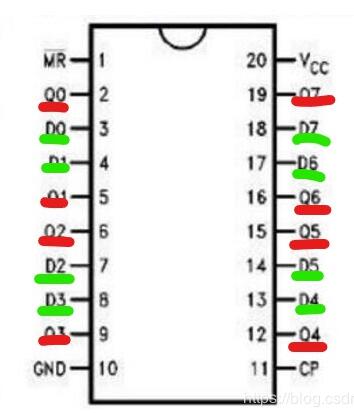

(1)1腳是復位/MR,低電平有效,當1腳是低電平時,輸出腳2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部輸出0,即全部復位。

(2)當1腳為高電平時,11(CP)腳是鎖存控制端,并且是上升沿觸發(fā)鎖存。。當11腳有一個上升沿,立即鎖存輸入腳3、4、7、8、13、14、17、18的電平狀態(tài),并且立即呈現(xiàn)在在輸出腳2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)上。

(3)74ls273其它管腳功能:1D~8D為數(shù)據(jù)輸入端,1Q~8Q為數(shù)據(jù)輸出端,正脈沖觸發(fā),低電平清除,常用作8位地址鎖存器。

74LS273的工作原理

1腳是復位端,11腳是時鐘(脈沖)輸入端;當1腳為L電平時,無論有無脈沖,數(shù)據(jù)端(D端)是H或L電平,輸出端(Q端)都為L電平;僅當1腳為高電平(H)時,“D”端的數(shù)據(jù)在脈沖的上升期間被傳送到“Q”端。

第一腳WR:主清除端,低電平觸發(fā),即當為低電平時,芯片被清除,輸出全為0(低電平);

CP(CLK):觸發(fā)端,上升沿觸發(fā),即當CP從低到高電平時,D0~D7的數(shù)據(jù)通過芯片;為0時將數(shù)據(jù)鎖存,D0~D7的數(shù)據(jù)不變。