為簡化和加速復雜IC的開發(fā),Cadence 設計系統(tǒng)公司 (NASDAQ:CDNS) 今天推出Tempus? 時序簽收解決方案。這是一款新的靜態(tài)時序分析與收斂工具,旨在幫助系統(tǒng)級芯片 (SoC) 開發(fā)者加速時序收斂,將芯片設計快速轉化為可制造的產(chǎn)品。

2013-05-21 15:37:37 2929

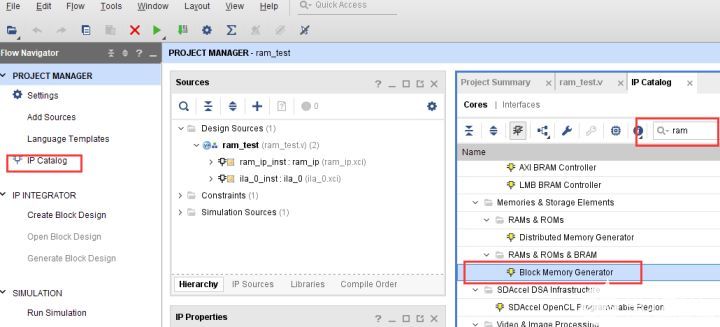

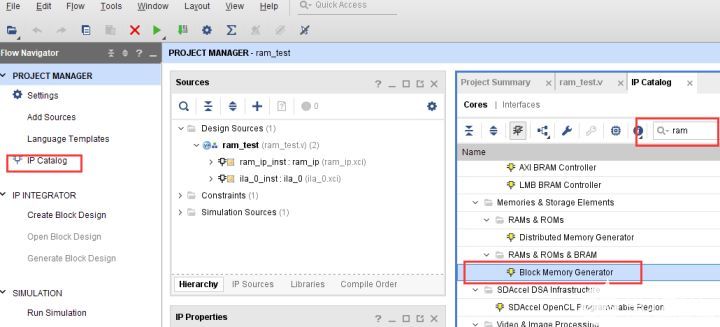

2929 RAM是FPGA中常用的基礎模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎。本實驗將為大家介紹如何使用FPGA內(nèi)部的RAM以及程序對該RAM的數(shù)據(jù)讀寫操作。

2021-01-22 09:43:11 4794

4794

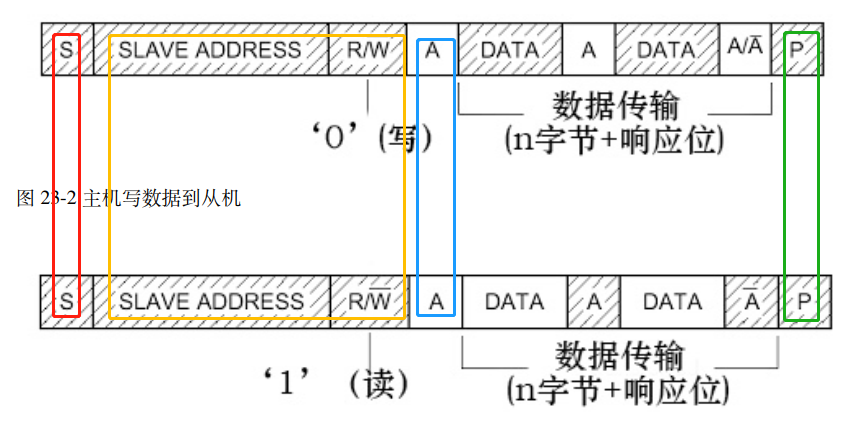

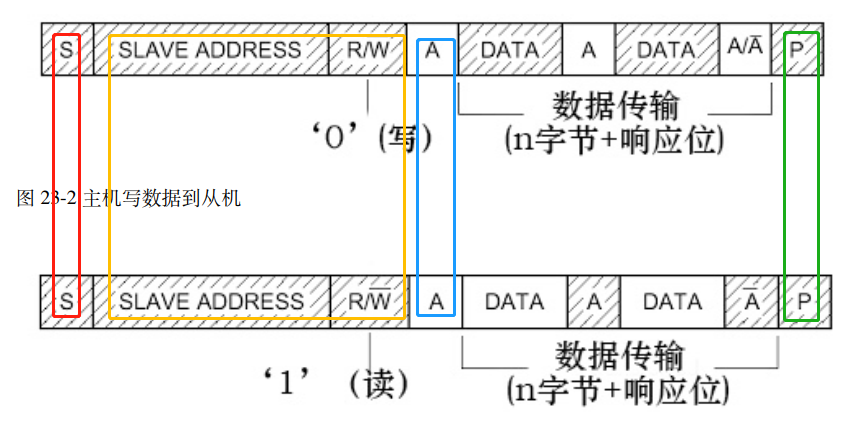

上篇推文對I2C總線的特性進行了介紹和描述。對于開發(fā)者而言,最重要的是編碼I2C的讀寫時序驅動。本篇推文主要總結和分享I2C總線主機端通信的編程實現(xiàn)思路,并不對應特定MCU的硬件I2C外設,此處需要加以區(qū)分。

2023-10-01 16:54:00 328

328

WebAssembly (Wasm) 正在成為一個廣受歡迎的編譯目標,幫助開發(fā)者構建可遷移平臺的應用。最近 Greptime 和 WasmEdge 協(xié)作,支持了在 WasmEdge 平臺上的 Wasm 應用通過 MySQL 協(xié)議讀寫 GreptimeDB 中的時序數(shù)據(jù)。

2023-12-22 11:03:26 425

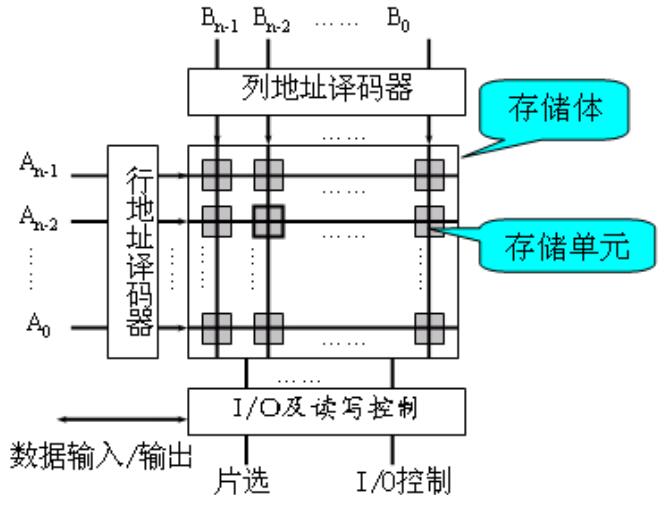

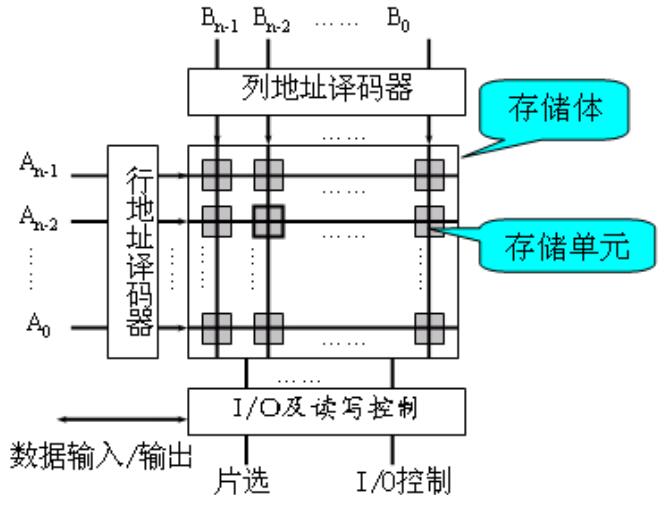

425 ram也叫主存,是與cpu直接交換數(shù)據(jù)的內(nèi)部存儲器。它可以隨時讀寫(刷新時除外)且速度很快,通常作為操作系統(tǒng)或其他正在運行中的程序的臨時數(shù)據(jù)存儲介質(zhì)。ram工作時可以隨時從任何一個指定的地址寫入

2020-12-16 06:29:16

ram也叫主存,是與CPU直接交換數(shù)據(jù)的內(nèi)部存儲器。它可以隨時讀寫(刷新時除外)且速度很快,通常作為操作系統(tǒng)或其他正在運行中的程序的臨時數(shù)據(jù)存儲介質(zhì)。ram工作時可以隨時從任何一個指定的地址寫入

2020-12-10 15:50:38

ram也叫主存,是與CPU直接交換數(shù)據(jù)的內(nèi)部存儲器。它可以隨時讀寫(刷新時除外)且速度很快,通常作為操作系統(tǒng)或其他正在運行中的程序的臨時數(shù)據(jù)存儲介質(zhì)。ram工作時可以隨時從任何一個指定的地址寫入

2020-12-31 06:18:55

最近在調(diào)試AD7616芯片,采用的方案是軟件并行模式,使用STM32F429+FMC轉換并讀取ad7616采樣數(shù)據(jù),目前在ad7616的讀寫時序配置上出現(xiàn)了一些問題,根據(jù)ad7616數(shù)據(jù)手冊上的相關

2023-12-07 08:23:04

DS1302數(shù)據(jù)讀寫時序圖

2012-08-05 21:34:50

DS2411的讀寫時序和DS18B20一致,畢竟同一個公司出的。下面是代碼源文件 ds2411.c#include "ds2411.h"#include "

2022-01-17 07:04:16

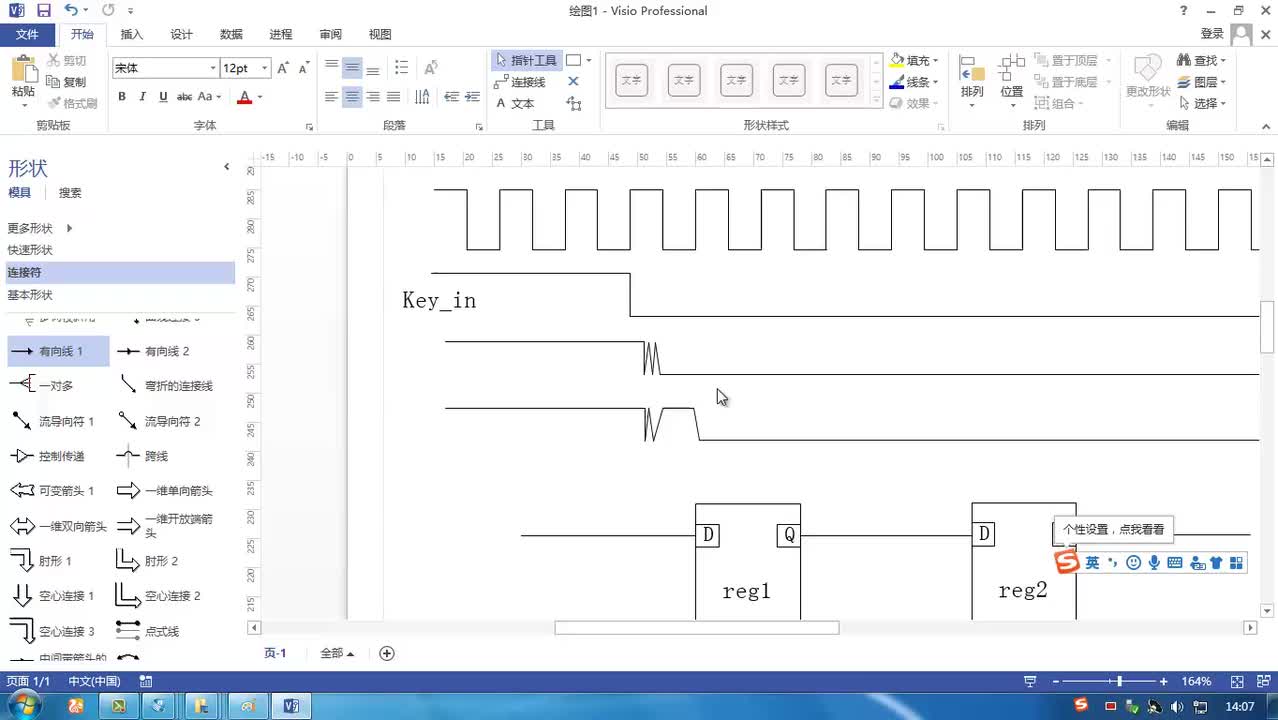

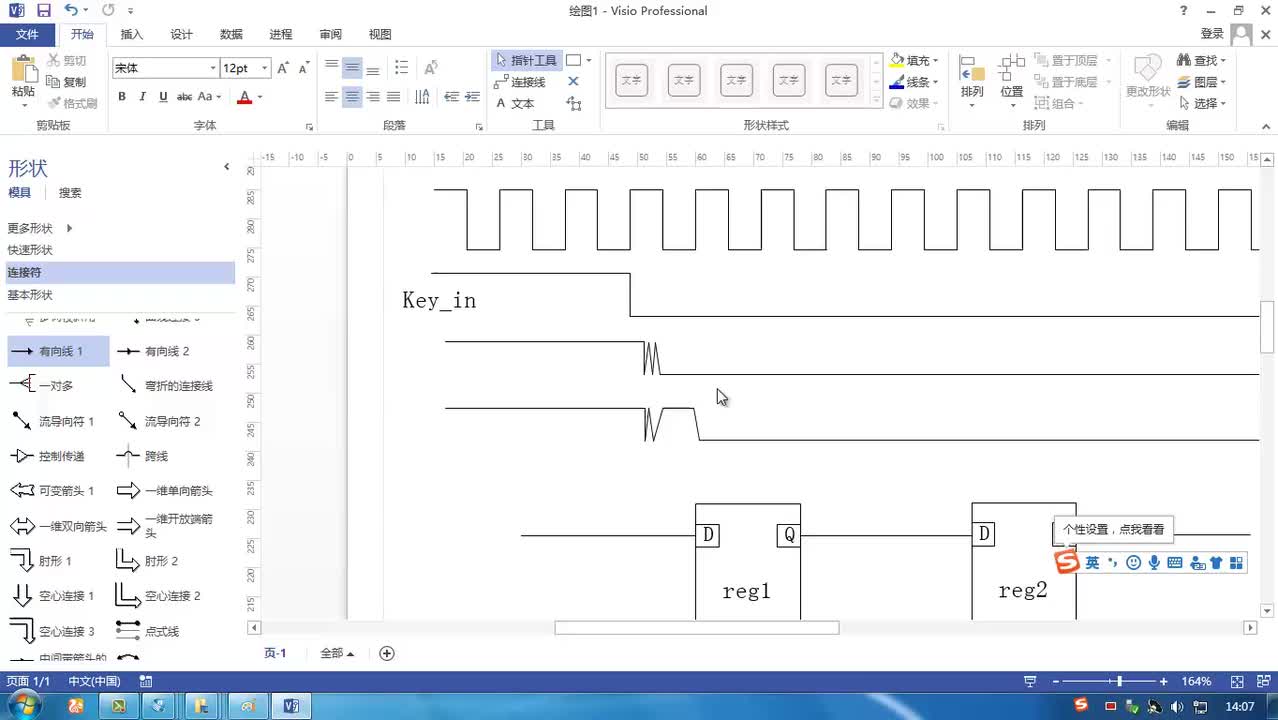

大佬們,求助一下。下面兩張圖是正常的讀寫時序和非正常讀寫時序。非正常讀寫時序中,發(fā)現(xiàn)數(shù)據(jù)保持長度比較短,而且AED在無效時應該為高阻態(tài),有問題的那塊板子,在無效時,AED為0

2019-12-24 15:42:02

文章目錄EEPROM介紹EEPROM 單字節(jié)讀寫操作時序EEPROM 寫數(shù)據(jù)流程EEPROM 讀數(shù)據(jù)流程EEPROM介紹在實際的應用中,保存在單片機 RAM 中的數(shù)據(jù),掉電后就丟失了,保存在單片機

2022-01-26 06:43:52

文章目錄EEPROM 多字節(jié)讀寫操作時序EEPROM 多字節(jié)讀寫操作時序我們讀取 EEPROM 的時候很簡單,EEPROM 根據(jù)我們所送的時序,直接就把數(shù)據(jù)送出來了,但是寫 EEPROM 卻沒有

2021-11-24 07:01:10

I2C讀寫時序I2CI2C寫時序I2C讀時序I2CI2C 總線上的每一個設備都可以作為主設備或者從設備,而且每一個設備都會對應一個唯一的地址(可以從 I2C 器件數(shù)據(jù)手冊得知),主從設備之間就是通過

2022-01-18 07:30:22

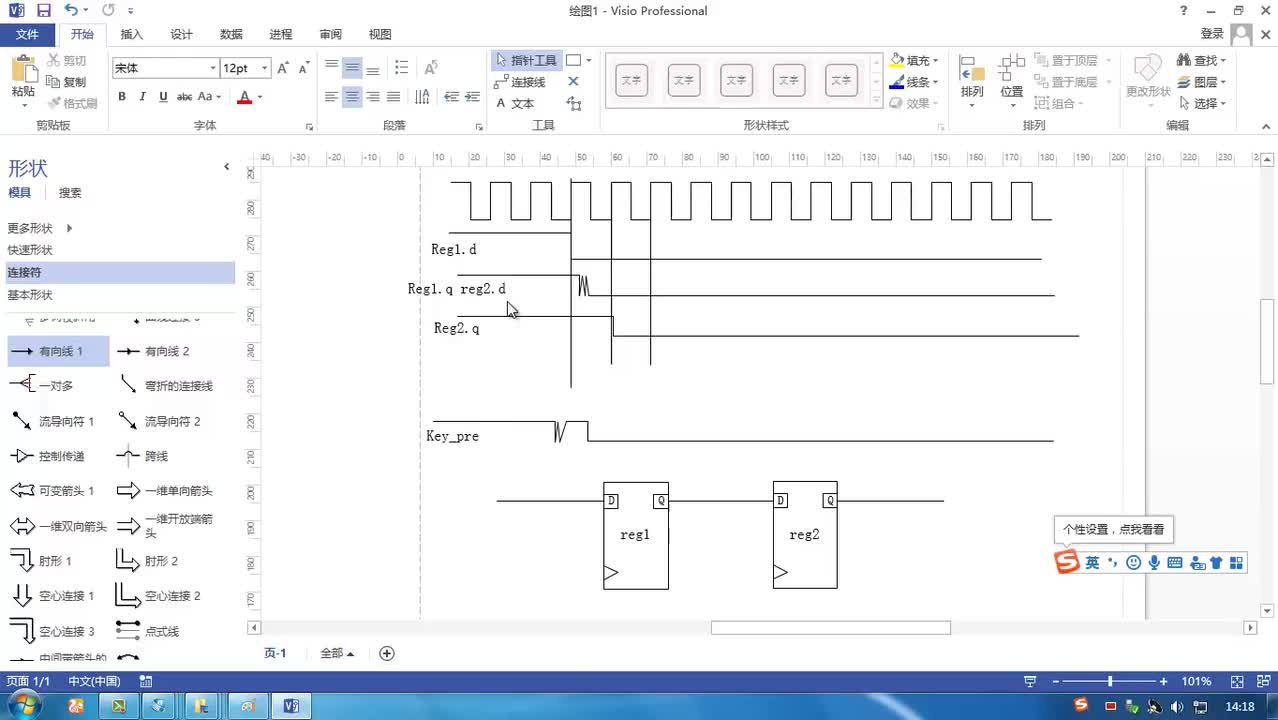

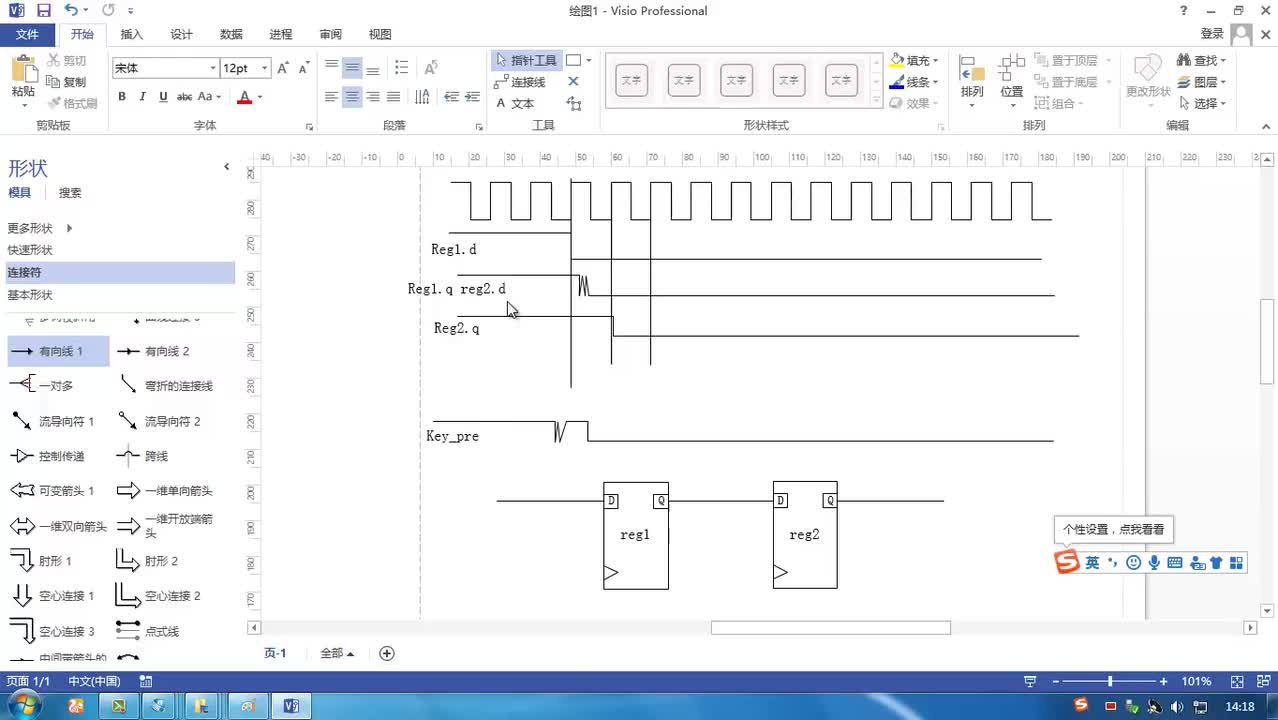

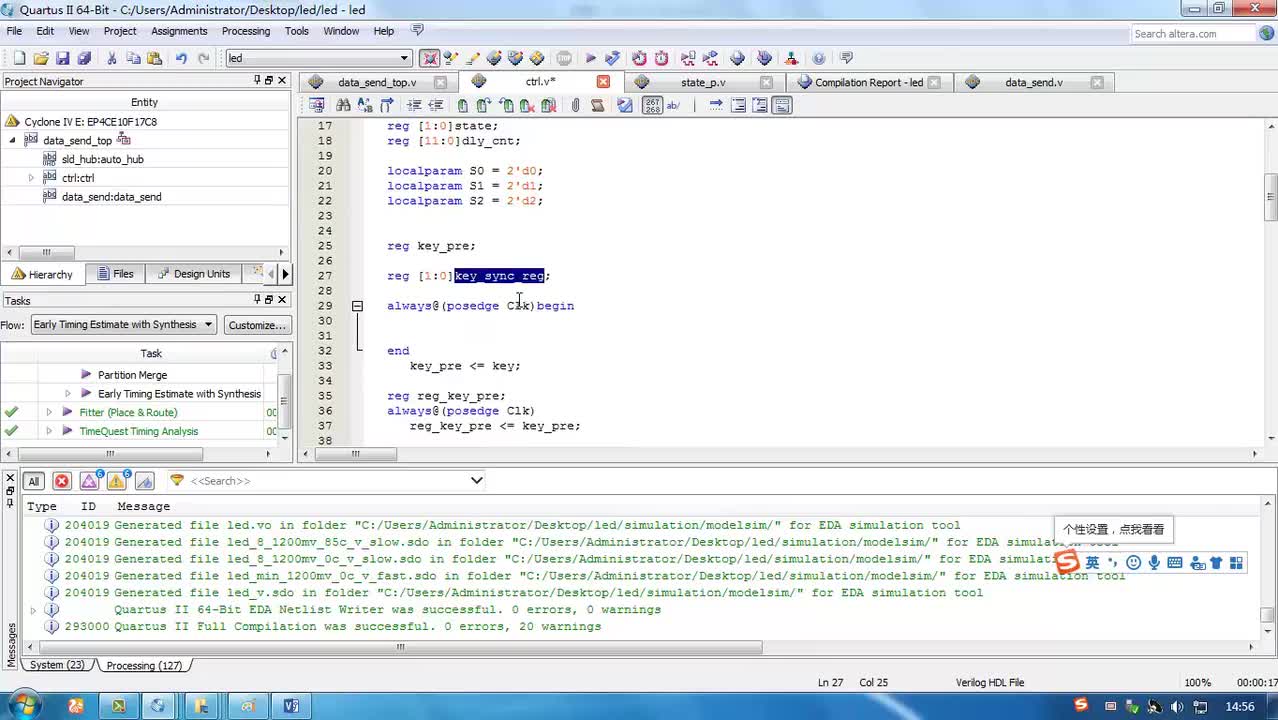

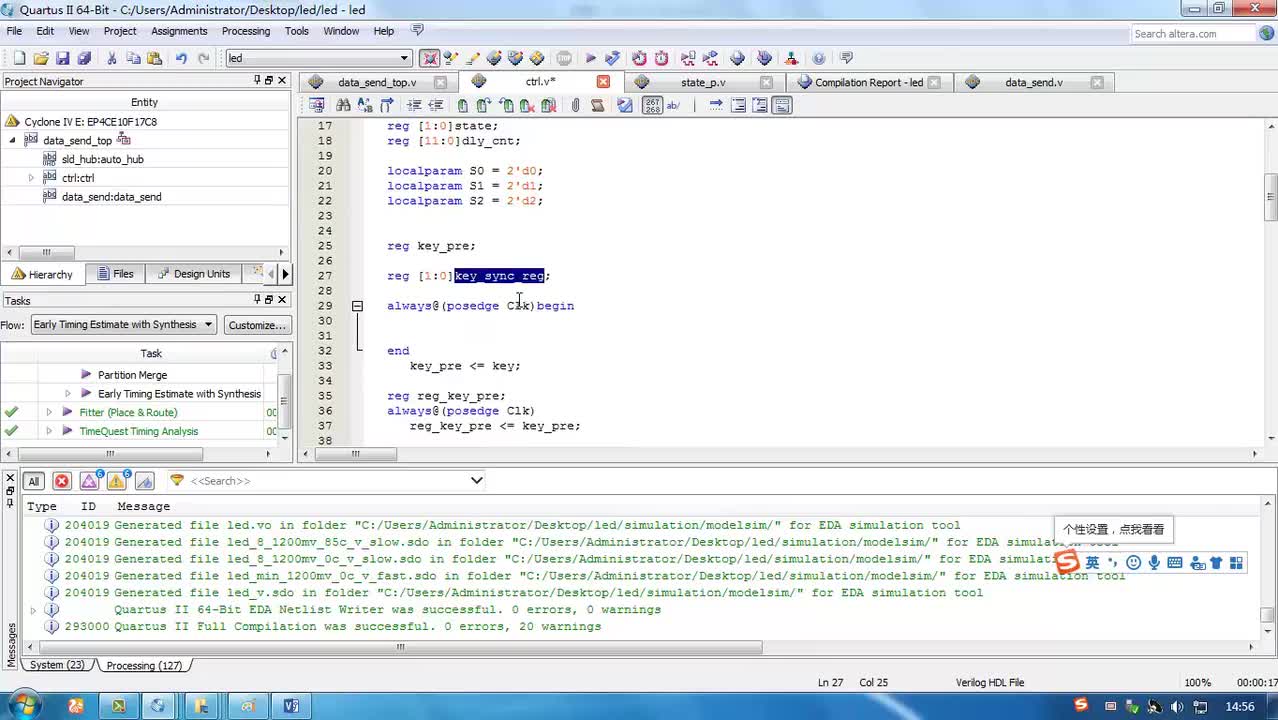

FPGA時序分析系統(tǒng)時序基礎理論對于系統(tǒng)設計工程師來說,時序問題在設計中是至關重要的,尤其是隨著時鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行?b class="flag-6" style="color: red">讀寫窗口越來越小,要想在很短的時間限制里,讓數(shù)據(jù)信號從驅動端完整

2012-08-11 17:55:55

IoT設備的增長引發(fā)了對內(nèi)存技術的新興趣,IPUS 自成立以來,已向市場推出了具有SPI和/或QSPI(Quad SPI)存儲器總線接口的IoT RAM。致力于為物聯(lián)網(wǎng)市場提供解決方案。IPUS

2020-07-10 16:11:28

看了芯片使用手冊,沒有看到,對其讀寫時序很模糊,求高手指導,謝謝

2012-07-10 22:10:27

?目錄0 引言1 SDIO接口1.1 SDIO接口有什么用?1.2 SDIO的功能框圖1.3 SDIO的命令與響應1.4 SDIO數(shù)據(jù)塊讀寫時序1.5 SDIO常用寄存器1.6 SD卡初始化流程

2022-02-21 06:58:01

SLE4442卡的讀寫時序,也是下降沿讀,上升沿寫嗎???求大神解惑!!!

2013-12-12 17:04:09

STM32 Cubemax(十三) ——SPI時序讀寫RFID-RC522目錄STM32 Cubemax(十三) ——SPI時序讀寫RFID-RC522前言一、SPI時序通信二、模塊接線三

2022-02-08 06:13:14

用 NFC 技術可提高流程效率并優(yōu)化成本。為了滿足這些市場需求,意法半導體提供了 ST25 NFC讀寫器和標簽,用于設計先進的集成式讀寫器+標簽NFC 解決方案。意法半導體將為這一強大而安全的集成方案提供專業(yè)支持。

2023-09-13 06:01:57

分析IS62WV51216BLL的讀寫時序圖和時間特性參數(shù),得到較合理的時間參數(shù),大大優(yōu)化了外部RAM的操作時間。下面先介紹下前面3個參數(shù):1.Address setup time: 從設置引腳地址開始到能夠讀取數(shù)據(jù)的時間段2.Data setup time: 設置完地址后,能夠讀取數(shù)據(jù)總線的時間段3.Bus

2021-12-03 06:43:54

本節(jié)的實驗對象SRAM(Static RAM)是一種異步傳輸?shù)囊资Т鎯ζ鳎?b class="flag-6" style="color: red">讀寫傳輸較快,控制時序也不復雜,因此目前有著非常廣泛的應用。你找來任何一顆SRAM芯片的datasheet,會發(fā)現(xiàn)它們的時序

2015-12-16 12:46:04

的讀寫時序。 2 模塊劃分本實例工程模塊層次如圖所示。●Pll_controller.v模塊產(chǎn)生FPGA內(nèi)部所需時鐘信號。●Ram_test.v模塊例化FPGA片內(nèi)RAM,并產(chǎn)生FPGA片內(nèi)RAM讀寫

2016-01-20 12:28:28

的在線邏輯分析儀chipscope,我們可以觀察FPGA片內(nèi)ROM、FIFO和RAM的讀寫時序,也可以只比較ROM預存儲的數(shù)據(jù)和RAM最后讀出的數(shù)據(jù),確認整個讀寫緩存過程中,數(shù)據(jù)的一致性是否實現(xiàn)。 2

2016-03-16 12:43:36

邏輯分析儀chipscope,我們可以觀察FPGA片內(nèi)ROM、FIFO和RAM的讀寫時序,也可以只比較ROM預存儲的數(shù)據(jù)和RAM最后讀出的數(shù)據(jù),確認整個讀寫緩存過程中,數(shù)據(jù)的一致性是否實現(xiàn)。 2 模塊

2019-01-10 09:46:06

問題是這樣的,單片機讀取外部ram時候,通過movx讀寫指定地址,單片機自動配置wd rd P0 以及ale口。并且自動產(chǎn)生讀寫時序。那么有沒有可能用單片機A來模擬一種時序,讓單片機B通過movx來讀取。所以想問問大家,這種做法有沒有可能實現(xiàn)

2017-03-23 23:40:55

求助:ddr2 ram,256M,64位位寬,突發(fā)長度為4時,讀寫地址如何提供。 1. 提供給控制器的數(shù)據(jù)是上升沿和下降沿的拼接,一個周期提供兩個數(shù)據(jù)到app_wdf_data,位寬為128位。那么

2013-09-29 21:48:53

spi讀寫時序里,圖中圓圈處MISO和MOSI為什么不一樣代表什么時序

2017-04-09 20:29:25

分立電池檢測解決方案

2021-02-26 08:38:00

單片機讀寫U盤開發(fā)方案 u***dll.com 非 51MCU+***/CH735 ,單芯片實現(xiàn)* 支持FAT32,F(xiàn)AT16* 是塊寫數(shù)據(jù),延長U盤壽命*一般

2009-01-17 10:12:34

本帖最后由 runileking 于 2016-4-14 17:56 編輯

RAM1和RAM2是兩個一樣的IP核,兩個時序一樣,見圖,為什么RAM1可以正確讀寫,RAM2讀不出數(shù)據(jù)?

2016-04-14 17:13:24

鳥人我找不到TFT讀寫命令時序的說明, 目前只有在程序里看的求貼士。。。。

2020-08-06 06:09:37

本文一方面旨在找到正確解決方案并選擇最合適的電源管理產(chǎn)品,另一方面則是如何優(yōu)化實際解決方案以用于FPGA。找到合適的電源解決方案尋找為FPGA供電的最佳解決方案并不簡單。許多供應商以適合為FPGA

2019-05-05 08:00:00

基于Blackfin的解決方案 針對ADSP-BF706 BLACKFIN+處理器的EVWSS軟件架構基于SigmaDSP的解決方案

2021-01-21 06:25:57

業(yè)內(nèi)首個signoff驅動的PrimeECO解決方案發(fā)布

2020-11-23 14:28:15

簡介 電源時序控制是微控制器、FPGA、DSP、ADC和其他需要多個電壓軌供電的器件所必需的一項功能。這些應用通常需要在數(shù)字I/O軌上電前對內(nèi)核和模擬模塊上電,但有些設計可能需要采用其他序列

2018-09-30 16:01:35

在VIVADO里為我們已經(jīng)提供了RAM的IP核, 我們只需通過IP核例化一個RAM,根據(jù)RAM的讀寫時序來寫入和讀取RAM中存儲的數(shù)據(jù)。實驗中會通過VIVADO集成的在線邏輯分析儀ila,我們可以觀察

2021-01-07 16:05:28

使用NVRAM的簡單解決方案

2021-01-13 06:56:35

nRF24L01+ 2.4GHz無線收發(fā)器的主要特性有哪些?如何使用SPI?如何對SPI的操作時序進行讀寫呢?

2021-12-20 06:32:33

早上好,來自西班牙的每個人,這里是一個棘手的問題,我需要填補(幾乎)8Mbit RAM(1Mx8)與傳入的ADC數(shù)據(jù),然后處理它。當我正在讀DMA規(guī)范時,似乎有64K的頁面限制,即當較低的16比特從

2019-08-02 07:49:48

SPI協(xié)議是什么?如何去實現(xiàn)SPI時序協(xié)議的基本讀寫呢?

2021-12-20 06:43:04

STM32F103的FSMC硬件有哪些呢?怎樣以代碼形式去說明LCD的讀寫時序呢?

2021-10-29 06:26:30

畫中畫的效果。在調(diào)試DDR3的過程中,我有一些高速存儲器的使用心得,特分享給大家。首先我先介紹一下SDRAM存儲器的讀寫時序。SDRAM即同步動態(tài)隨機存儲單元,主要用來存儲較大容量的數(shù)據(jù)。我們都知道,數(shù)據(jù)

2020-01-04 19:20:52

進行監(jiān)控。當所有電壓建立之后,時序控制器電路產(chǎn)生電源良好信號。模擬時序控制解決方案(如ADM1186-1)很容易使用。它們具備多電壓系統(tǒng)所需的全部功能。模擬時序控制器與數(shù)字時序控制器的不同之處在于,前者

2021-04-12 07:00:00

傳統(tǒng)電源方案有哪些弊端?取代傳統(tǒng)電源方案的LIPS解決方案

2021-06-08 07:18:50

就像每個MOSFET需要一個柵極驅動器來切換它,每個電機后面總是有一個驅動力。根據(jù)復雜程度和系統(tǒng)成本、尺寸和性能要求,驅動電機的方式多樣。最簡單和離散的解決方案是由兩個晶體管組成的圖騰柱/推挽電路

2019-03-08 06:45:03

正確收發(fā)數(shù)據(jù),從而使系統(tǒng)不能正常工作。隨著系統(tǒng)時鐘頻率的不斷提高和信號邊沿不斷變陡,系統(tǒng)對時序有更高的要求,一方面留給數(shù)據(jù)傳輸?shù)挠行?b class="flag-6" style="color: red">讀寫窗口越來越小,另一方面,傳輸延時要考慮的因素增多,要想在很短的時間限制里,讓數(shù)據(jù)信號從驅動端完整地傳送到接收端,就必須進行精確的時序計算和分析。

2012-08-02 22:26:06

51 系列單片機慢速讀寫的時序擴展

2009-05-15 14:28:16 18

18 SRAM的簡單的讀寫操作教程

SRAM的讀寫時序比較簡單,作為異步時序設備,SRAM對于時鐘同步的要求不高,可以在低速下運行,下面就介紹SRAM的一次讀寫操作,在

2010-02-08 16:52:39 140

140 摘要:本文介紹了在單片機應用領域中RAM讀寫存儲器中數(shù)據(jù)在掉電時的三種保護方法及相應的設計電路和軟件設計方法,以便更可靠地保護RAM中的數(shù)據(jù)。關鍵詞:RAM 掉電保護

2010-05-31 09:47:41 29

29 LSI 公司與Zarlink半導體日前宣布聯(lián)合推出一款解決方案,該解決方案預集成了 Zarlink 的時序分組 (TOP) 專業(yè)技術和 LSI Axxia通信處理器系列產(chǎn)品,可大幅加速產(chǎn)品上市進程,并顯著簡化網(wǎng)絡 OEM 廠商的集成工作。

2011-03-15 09:12:32 2285

2285 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現(xiàn)工具來優(yōu)化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1169

1169 單片機擴展外部ROM或RAM讀寫時序,PPT介紹。

2016-12-12 21:36:19 9

9 對于mig與DDR3/DDR2 SDRAM的讀寫時序我們不需要了解太多,交給mig就可以了。

2019-03-03 11:11:53 5640

5640

ram也叫主存,是與CPU直接交換數(shù)據(jù)的內(nèi)部存儲器。它可以隨時讀寫(刷新時除外)且速度很快,通常作為操作系統(tǒng)或其他正在運行中的程序的臨時數(shù)據(jù)存儲介質(zhì)。ram工作時可以隨時從任何一個指定的地址寫入

2020-12-09 14:25:05 14861

14861

RAM是FPGA中常用的基礎模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎。本實驗將為大家介紹如何使用FPGA內(nèi)部的RAM以及程序對該RAM的數(shù)據(jù)讀寫操作。

2022-02-08 15:50:49 12183

12183

RAM是FPGA中常用的基礎模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎。本實驗將為大家介紹如何使用FPGA內(nèi)部的RAM以及程序對該RAM的數(shù)據(jù)讀寫操作。

2021-03-15 06:09:45 14

14 文章目錄EEPROM 多字節(jié)讀寫操作時序EEPROM 多字節(jié)讀寫操作時序我們讀取 EEPROM 的時候很簡單,EEPROM 根據(jù)我們所送的時序,直接就把數(shù)據(jù)送出來了,但是寫 EEPROM 卻沒有

2021-11-16 14:21:05 8

8 STM32入門開發(fā): 采用IIC硬件時序讀寫AT24C08(EEPROM)

2021-11-21 13:51:04 45

45 分析IS62WV51216BLL的讀寫時序圖和時間特性參數(shù),得到較合理的時間參數(shù),大大優(yōu)化了外部RAM的操作時間。下面先介紹下前面3個參數(shù):1.Address setup time: 從設置引腳地址開始到能夠讀取數(shù)據(jù)的時間段2.Data setup time: 設置完地址后,能夠讀取數(shù)據(jù)總線的時間段3.Bus

2021-11-23 17:36:41 21

21 STM32 Cubemax(十三) ——SPI時序讀寫RFID-RC522目錄STM32 Cubemax(十三) ——SPI時序讀寫RFID-RC522前言一、SPI時序通信二、模塊接線

2021-12-04 20:36:09 51

51 ram也叫主存,是與CPU直接交換數(shù)據(jù)的內(nèi)部存儲器。它可以隨時讀寫(刷新時除外)且速度很快,通常作為操作系統(tǒng)或其他正在運行中的程序的...

2022-01-25 20:03:25 1

1 新思科技近日宣布與Ansys聯(lián)合開發(fā)的電壓時序簽核解決方案已獲三星采用,用以加速開發(fā)其具有理想功耗、性能和面積(PPA)的高能效比設計。

2022-04-24 15:27:02 1236

1236 該聯(lián)合解決方案基于新思科技的行業(yè)金牌PrimeTime簽核技術和Ansys 的RedHawk-SC電源完整性簽核技術,能夠防止動態(tài)電壓降引起的時序失效并盡可能減小時序悲觀性。

2022-04-27 14:29:22 811

811 本文介紹了在低功耗系統(tǒng)中降低功耗同時保持測量和監(jiān)控應用所需的精度的時序因素和解決方案。它解釋了當所選ADC是逐次逼近寄存器(SAR)ADC時影響時序的因素。對于Σ-Δ(∑-Δ)架構,時序考慮因素有所不同(請參閱本系列文章的第1部分)。本文探討了模擬前端時序、ADC時序和數(shù)字接口時序中的信號鏈考慮因素。

2022-12-13 11:20:18 1057

1057

。本來的含義是:ROM是Read Only Memory的意思,也就是說這種存儲器只能讀,不能寫。而RAM是Random Access Memory的縮寫。這個詞的由來是因為早期的計算機曾經(jīng)使用磁鼓作為內(nèi)存,而磁鼓和磁帶都是典型的順序讀寫設備。RAM則可以隨機讀寫。

2023-03-30 14:53:27 1941

1941 本文將介紹低功耗系統(tǒng)在降低功耗的同時保持精度所涉及的時序因素和解決方案,以滿足測量和監(jiān)控應用的要求。

2023-07-11 16:16:26 360

360

8月10日, 三星半導體在本次第五屆OCP China Day 2023(開放計算中國技術峰會)上分享了兩大應對內(nèi)存墻限制的創(chuàng)新技術解決方案和開放協(xié)作的業(yè)務戰(zhàn)略。

2023-08-10 14:16:26 685

685 電子發(fā)燒友網(wǎng)站提供《GD32F30x的設備限制及解決方案介紹.pdf》資料免費下載

2023-12-14 09:44:12 0

0 電子發(fā)燒友網(wǎng)站提供《GD32F45x/F40x的設備限制及解決方案介紹.pdf》資料免費下載

2023-12-14 09:45:45 0

0 電子發(fā)燒友網(wǎng)站提供《GD32F3x0的設備限制及解決方案介紹.pdf》資料免費下載

2023-12-14 09:47:44 0

0 電子發(fā)燒友網(wǎng)站提供《GD32E50x系列器件的限制及解決方案勘誤手冊.pdf》資料免費下載

2023-12-14 09:49:18 0

0 ram也叫主存,是與CPU直接交換數(shù)據(jù)的內(nèi)部存儲器。它可以隨時讀寫(刷新時除外)且速度很快,通常作為操作系統(tǒng)或其他正在運行中的程序的臨時數(shù)據(jù)存儲介質(zhì)。

2024-01-09 11:11:57 436

436

電子發(fā)燒友網(wǎng)站提供《GD32A503系列器件的限制及解決方案介紹.pdf》資料免費下載

2024-01-26 10:21:03 0

0 電子發(fā)燒友網(wǎng)站提供《GD32A513系列器件的限制及解決方案介紹.pdf》資料免費下載

2024-01-26 10:19:45 0

0 FPGA雙口RAM的使用主要涉及配置和使用雙端口RAM模塊。雙端口RAM的特點是有兩組獨立的端口,可以對同一存儲塊進行讀寫操作,從而實現(xiàn)并行訪問。

2024-03-15 13:58:14 80

80

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

2929

2929 4794

4794

328

328

425

425 140

140 29

29

2285

2285 1169

1169 14861

14861

12183

12183

14

14 8

8 45

45 21

21 51

51 1

1 1236

1236 811

811 1057

1057

1941

1941 360

360

685

685 0

0 436

436

80

80

評論