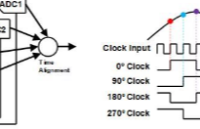

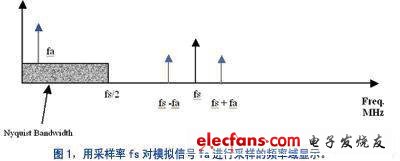

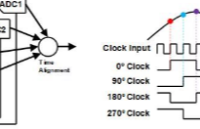

交織結構的優勢可惠及多個細分市場。交織型ADC最大好處是增加了帶寬,因為ADC的奈奎斯特帶寬更寬了。同樣,我們舉兩個100 MSPS ADC交織以實現200 MSPS采樣速率的例子。

2020-06-09 09:54:49 6440

6440

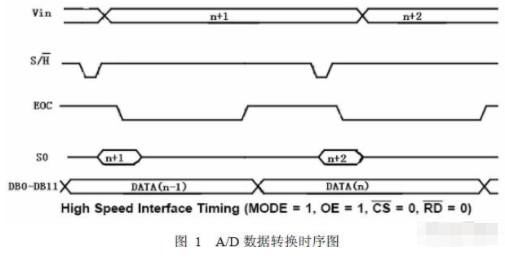

ADC 使用若干個ADC_CLK 周期對輸入電壓采樣,采樣周期數目可以通過ADC_SMPR1 和ADC_SMPR2 寄存器中的SMP[2:0]位而更改。

2012-03-22 10:45:30 5849

5849 在之前接觸的設計中如果涉及要實現ADC采樣的話,往往會從精度和速率來考慮對性能的影響,一般來說精度是固定的或有一個最大精度設置,但是采樣速率的話,過快會造成采樣不準確,往往會對整個設計的性能造成限制

2017-09-22 11:24:34 9499

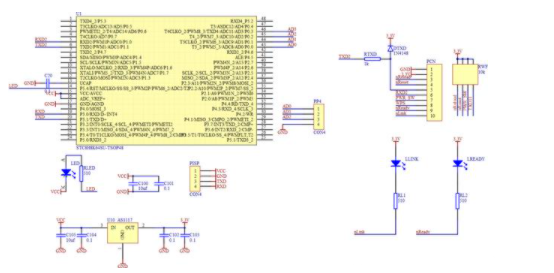

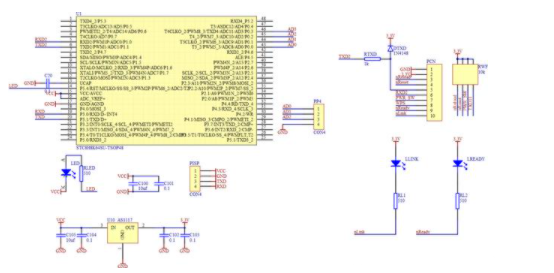

9499 設計基于STC8G8K64U單片機的高速ADC采樣板,可以為普通的電路實驗提供快速波形采樣的模塊。

2021-04-28 11:12:00 7669

7669

如今大多數ADC芯片里都集成了采樣保持功能,以便更好地處理交流信號,這種類型的ADC我們叫做采樣ADC,可是早些時候的ADC并非采樣類型,而只是一個簡單的編碼器。 非采樣ADC的一個缺點是,如果在

2021-04-28 11:02:50 24116

24116

ADC掃描采樣若干通道,數據保存在指定緩沖區,連續采樣若干次之后觸發中斷,然后讀取采樣數據處理。

2022-09-09 12:54:11 1747

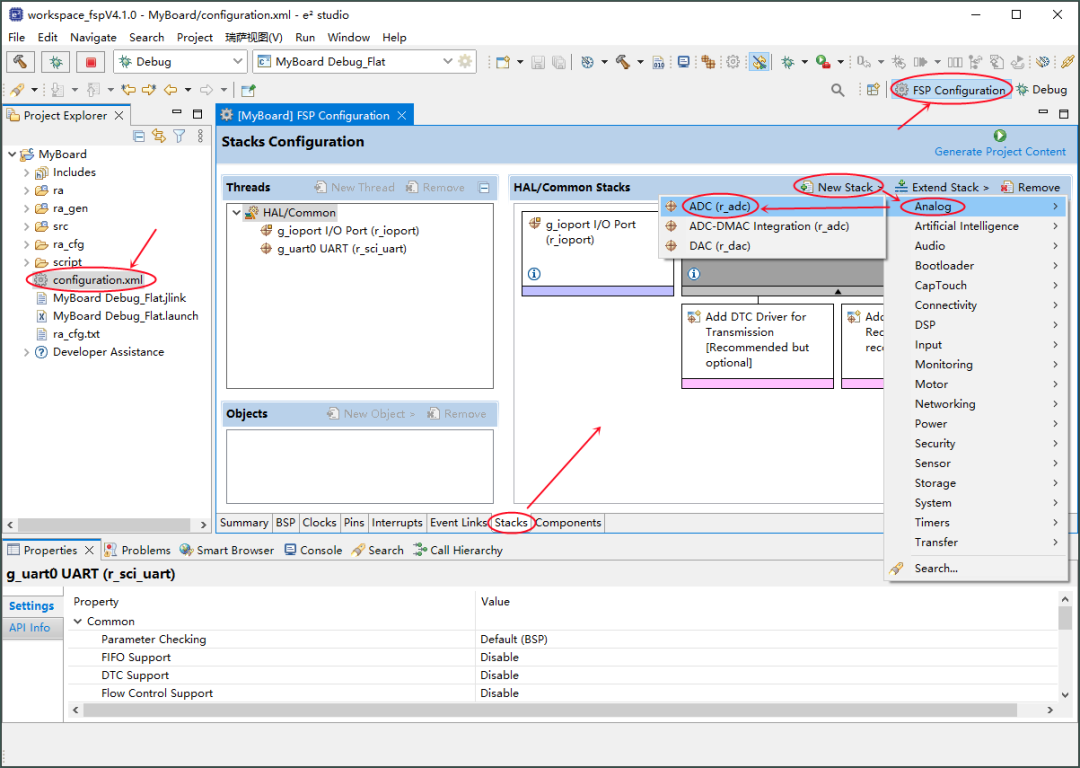

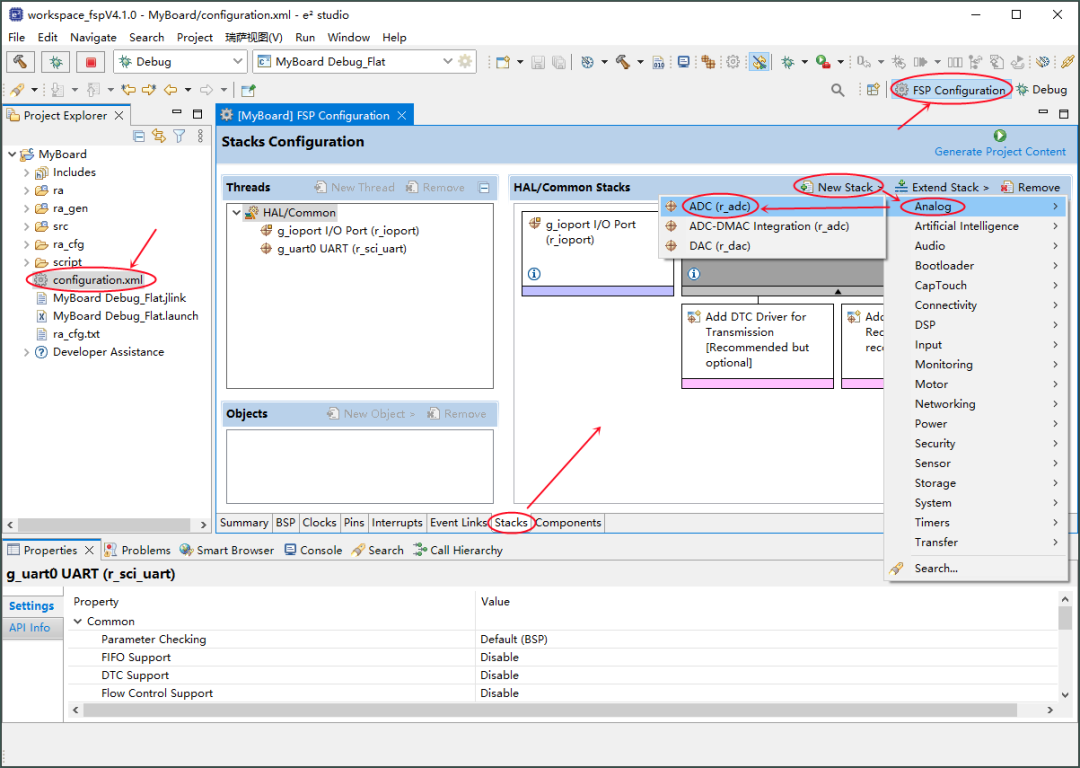

1747 在RA6M4處理器的ADC里,有兩路ADC可以分別采樣當前的CPU內部溫度和參考電壓值。

2022-12-19 09:23:20 1498

1498

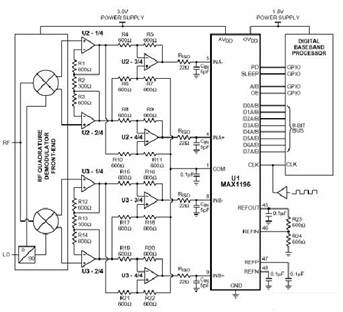

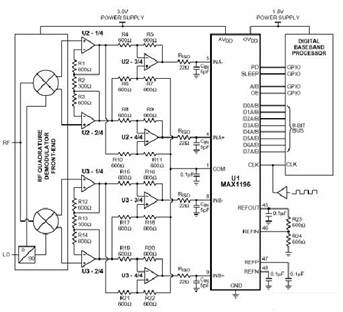

本文詳細介紹了通常應用于IF和基帶的高速模數轉換器(ADC)的正確布板、元件選擇及元件布局。文中以高分辨率、高速數據轉換器MAX12555系列為例,介紹了優化電路設計、正確高速布板、旁路和去耦技巧、熱管理、元件選擇及布局。

2023-02-23 14:53:19 757

757 2808中epwm啟動adc采樣,現在希望在一次epwm中斷中(采樣讀值在epwm中斷中,不對adc設置中斷函數),要求對某一通道連續采樣四次,而不是用四個通道,請問有沒有可能實現?

2020-05-12 09:33:34

作為一個偏向工控的芯片,ADC采樣是一個十分重要的外設。STM32集成三個12位精度18通道的內部ADC,最高速度1微秒,結合DMA可以解放CPU進行更好的處理。ADC接口上的其它邏輯功能包括:

2019-07-18 08:25:29

在雷達、導航等軍事領域中,由于信號帶寬寬(有時可能高于10MHz),要求ADC的采樣率高于30MSPS,分辨率大于10位。目前高速高分辨率ADC器件在采樣率高于10MSPS時,量化位數可達14位,但

2021-04-14 06:16:30

ADC_RegularChannelConfig(ADC1, ADC_Channel_10, 1, ADC_SampleTime_55Cycles5); //設置指定 ADC 的規則組通道,設置它們的轉化順序和采樣時間 ADC

2020-08-28 08:00:16

采用的高速AD:PXIe-5114 PXI示波器,高速DA:PXIe-5413 PXI波形發生器,跪求實現高速DA采樣和AD的例程。

2018-08-21 16:19:19

大家好,我的問題與樣品率有關。選擇任意波形采樣率的ADC采樣率的標準是什么?在我的例子中,我的WaveDAC(50 KSPS)直接連接到ADC(17位;5kSPS和實際轉換率=4935個SPS

2018-12-28 15:26:46

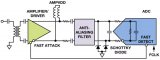

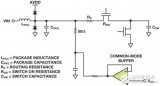

采用高速模數轉換器(ADC)的系統設計非常困難,對于輸入有兩類ADC架構可供選擇:緩沖型和無緩沖型。

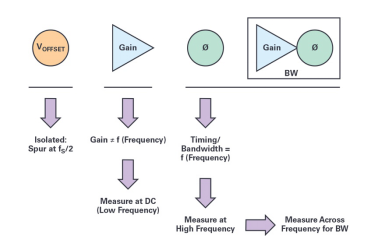

緩沖和無緩沖架構的特征

高線性度緩沖器,但需要更高的功率;

更易設計輸入網絡與高阻抗緩沖器接口

2023-12-18 07:42:00

采用高速模數轉換器(ADC)的系統設計非常困難,對于輸入有兩類ADC架構可供選擇:緩沖型和無緩沖型。緩沖和無緩沖架構的特征緩沖架構的基本特征*高線性度緩沖器,但需要更高的功率;*更易設計輸入網絡與高

2018-10-18 11:23:57

正確選擇輸入網絡元件對于高速ADC的驅動和輸入網絡的平衡至關重要(參考應用筆記:“正確選擇輸入網絡,優化高速ADC的動態性能和增益平坦度”)。??在較高IF應用中,端接電阻的位置非常重要。交流耦合

2021-10-23 11:10:35

。近年來,NS、Atmel等公司都開發出了高速ADC,比如ADC08D1000、AT84AS003TP等,它們都是經采樣后分多路降速進行傳輸。目前,多路并行數據傳輸存儲成為高速信號采集系統的主流趨勢。

2019-07-05 08:11:34

外部高速ADC,PWM輸出做時鐘驅動,GPIO端口做數據接口,DMA讀取到內部RAM,可以做到30M的采樣速度嗎,新唐M4的IO口的讀取速度有那么高嗎

2023-06-26 06:26:11

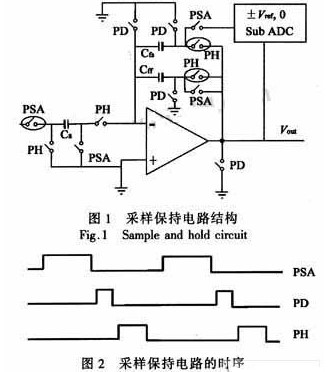

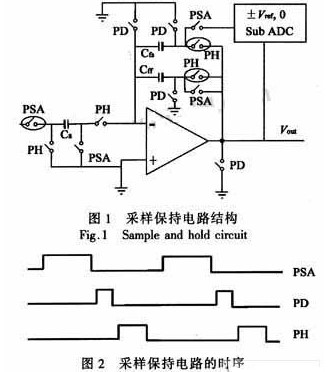

的應用中是一個關鍵部分。由于其他結構諸如兩步快閃結構或內插式結構都很難在高輸入頻率下提供低諧波失真,因此流水線結構在高速低功耗的ADC應用中也成為一個比較常用的結構。 作為流水線ADC前端的采樣保持

2018-10-08 15:47:53

高速、超寬帶信號采集技術在雷達、天文和氣象等領域應用廣泛。高采樣率需要高速的模/數轉換器(ADC)。目前市場上單片高速ADC的價格昂貴,分辨率較低,且采用單片超高速ADC實現的數據采集對FPGA的性能和PCB布局布線技術提出了嚴峻的挑戰。

2019-11-08 06:34:52

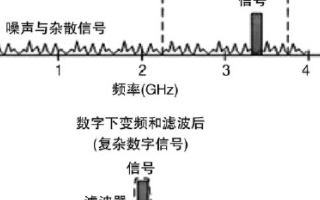

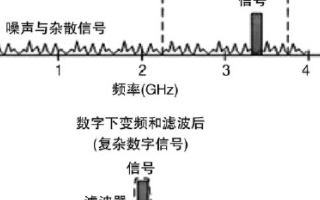

關于AD選型過程中,看到ADI出了一些針對直接射頻采樣的高速寬帶ADC和DAC,比如AD9625和AD9144,最大采樣率可以支持2.5GSPS和2.8GSPS. 我一直有個觀點,就是SDR的一個

2018-10-10 14:28:33

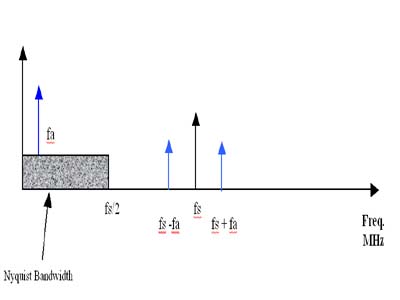

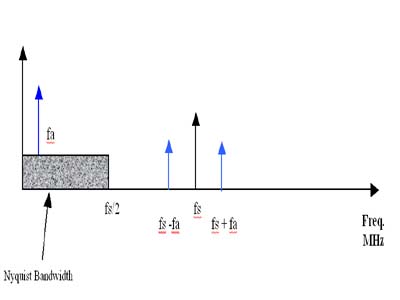

Nyquist 和 Shannon信息定理是什么?使用國家半導體ADC演示高速ADC應用欠采樣的作用與好處是什么?

2021-05-28 06:53:56

描述TIDA-01016 是一款適合高動態范圍高速 ADC 的時鐘解決方案。射頻輸入信號由高速 ADC 直接采用射頻取樣法捕獲。ADC32RF80 是一款雙通道 14 位 3GSPS 射頻取樣

2018-09-30 09:26:09

關于高速ADC的選擇與應用你想要的都在這里

2021-05-25 06:57:38

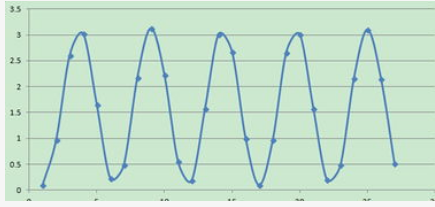

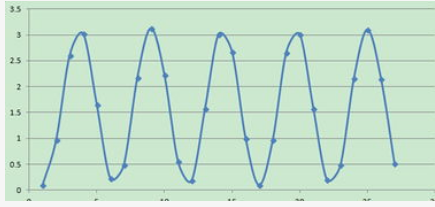

摘 要: 針對當前高采樣率ADC成本高昂、采樣精度較低的問題,提出了基于欠采樣的信號頻率估計方法,通過組合使用低速ADC,可以達到高速ADC的采樣效果。通過建立仿真對所提出的方法進行驗證,結果顯示

2018-07-31 10:24:36

介紹了一種基于現場可編程門陣列(FPGA)和第二代雙倍數據率同步動態隨機存取記憶體(DDR2)的高速模數轉換(ADC)采樣數據緩沖器設計方法,論述了在Xilinx V5 FPGA中如何實現高速同步

2010-04-26 16:12:39

如何合理的選擇PLC?如何利用三菱PLC實現對印刷機的精確控制?

2021-11-03 07:02:27

高頻應用如何才能取得最好性能所需的變頻器特性?如何選擇適合高頻應用的高速ADC?

2021-04-13 06:45:25

如何在Mbed OS操作系統下實現ADC高速數據采樣?

2021-12-17 06:38:46

如何用STM32內置的高速ADC去實現一個數字采樣示波器呢?其實現方式是什么?

2021-11-08 06:52:55

需要一個高速的ADC在某個定點進行采樣,對采樣的電壓值進行量化,但是找了一圈好像高速的ADC都是時鐘直接控制的,只能在時鐘的沿進行采樣。因為需要對外部事件產生的時間點對電壓值進行量化操作,所以需要實時。按道理來說應該是有的啊我感覺

2022-03-14 21:14:01

ADI的高速模數轉換器(高速ADC)提供市場上最佳的性能和最高的ADC采樣速度。該系列產品包括高中頻ADC (10MSPS -125MSPS)、集成接收機的低中頻ADC (125MSPS

2017-04-12 17:24:29

定時器觸發ADC采樣如何去實現呢?如何使用ADC的定時器去觸發ADC單次轉換的功能呢?

2021-11-23 06:23:29

(使用放大器)也可以是無源(使用變壓器或巴倫),具體取決于系統要求。無論哪種情況,都必須謹慎選擇元器件,以便實現在目標頻段的最優ADC性能。射頻采樣ADC采用深亞微米CMOS工藝技術制造,并且半導體器件的物理

2018-11-01 11:25:01

怎么實現高速采樣保持電路的設計?

2021-10-11 07:42:17

谷歌搜索術語“模數轉換器選擇”會產生了數以千計的搜索結果,證明這一任務對參與設計傳感解決方案的許多人而言仍然具有挑戰性。畢竟,從8位微控制器(MCU)中集成的簡單10位ADC到可以GHz速率解析

2019-03-18 06:45:12

需要選擇一款帶寬在2MHz以上、采樣率在20MSPS、位數最好是16位的高速ADC,對于有正有負的正弦脈沖信號應選擇怎樣的ADC進行采樣?

2023-12-21 07:40:09

小弟最近項目中要對200KHz的超聲波信號進行采樣,采樣時長越100us,無奈MCU自帶的ADC采樣率最高才200ksps,所以希望用MCU外帶一塊高速ADC來實現。因為后續處理要求精度比較高,所以

2018-09-27 11:45:20

您好:我在選型高速ADC時,發現datasheet上標注了采樣率范圍,給出最小值典型值和最大值。比如AD9208,輸入時鐘最高6GHz,采樣率三值分別為2500,3000,3100MSPS。請問

2018-07-30 08:53:53

搬移到基帶不會被Fs/2內的信號干擾,因此,Pipeline型的ADC也常常被稱為欠采樣ADC。(原文 德州儀器高性能單片機和模擬器件在高校中的應用和選型指南 p13),請問這里所說的把中頻處的信號搬移到基帶進行處理,是怎么實現的?不理解?請教

2019-02-26 08:59:33

想請問大家: 我擬采用500Msps以上采樣率,JESD204B接口的ADC芯片構建2通道以上的一個多通道高速數據采集系統。為使討論問題具體,簡單,明確。現假設有一系統是4個采樣率500Msps

2018-07-24 10:45:54

需要選擇一款帶寬在2MHz以上、采樣率在20MSPS、位數最好是16位的高速ADC,對于有正有負的正弦脈沖信號應選擇怎樣的ADC進行采樣?附件print_26.bmp2.3 MB

2018-10-26 09:33:24

問個類似的問題,如果我系統采樣頻率是62MHz,對于同一款ADC,比如AD9258,有AD9258-65,也有AD9268-80。我是否也要選擇-65的?

2019-03-11 09:48:26

ADI的高速模數轉換器(高速ADC)提供市場上最佳的性能和最高的ADC采樣速度。該系列產品包括高中頻ADC (10MSPS -125MSPS)、集成接收機的低中頻ADC (125MSPS

2018-08-17 06:55:58

Luminary的ADC過采樣應用筆記

本文主要介紹一種Luminary單片機高精度低成本AD轉換的實現方法,解決在某些要求高精度ADC領域的Luminary應用問題。

2010-04-03 14:38:21 31

31 ,信號帶寬同等重要。我們發現,高于 Shannon 速率的采樣還有其它的好處,如處理增益可以極大地改善動態范圍。系統設計師掌握了這一知識,就能在通用且價格合理的標準 ADC 中,正確地選擇 ADC 采樣頻率和精度。

2006-03-11 12:54:23 1448

1448

在高速數據采集中,高速ADC的選用和數據的存儲是兩個關鍵問題。本文介紹一種精度為12位、采樣速率達25Msps的高速模數轉換器AD9225,并給出其與8位RAM628512存儲器的接口電路。由于存儲

2009-06-16 07:51:33 4226

4226

高性能、多通道、同時采樣ADC在數據采集系統(DAS)中的設計摘要:本文將幫助設計人員實現高性能、多通道、同時采樣的數據采集系統(DAS)。介紹了元器件的合理選擇及其PCB布線

2009-06-23 21:12:55 4022

4022

高速ADC,什么是高速ADC

背景知識:

隨著計算機技術、通信技術和微電子技術的高速發展,大大促進了ADC技術的發展,ADC作為模擬量與數據量接

2010-03-24 13:28:01 9741

9741 設置高速ADC的共模輸入電壓范圍(中文)

對于包含基帶采樣、高速ADC的通信接收機,輸入共模電壓范圍(VCM)非常重要。特別是對于單電源供

2010-03-30 17:59:39 3883

3883

本文介紹對于了解高速ADC電源設計至關重要的各種測試測量方法。為了確定轉換器對供電軌噪聲影響的敏感度,以及確定供電軌必須處于何種噪聲水平才能使ADC實現預期性能,有兩種測

2011-06-28 09:51:15 1027

1027

本文應用ADS 軟件設計了一個4GSps 4bit GaAs 基超高速ADC,該ADC 芯片采用折疊內插結構實現。文中詳細描述了采樣保持電路(T/H)與折疊內插電路設計與仿真,芯片最終采用GaAs HBT 工藝實現

2011-07-05 15:45:24 48

48 C8051F020實現C8051F020實現ADC采樣芯片外的模擬電壓ADC采樣芯片外的模擬電壓通過LCD顯示,并通過串口發送到PC機

2015-11-12 14:23:11 29

29 基于FPGA的高速多通道AD采樣系統的設計與實現_徐加彥

2017-01-18 20:23:58 12

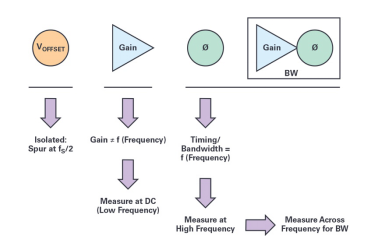

12 現代高速采樣ADC設計為低失真和寬失真信號處理系統中的動態范圍。實現規定的性能電平取決于ADC自身外部的許多因素,包括適當的設計任何必要的支持電路。模擬輸入驅動電路為尤其重要,因為在以下情況下,它會降低固有的ADC動態性能:設計不當。

2022-08-01 14:18:13 0

0 了解高速ADC時鐘抖動的影響將高速信號數字化到高分辨率要求仔細選擇一個時鐘,不會妥協模數轉換器的采樣性能(ADC)。 在這篇文章中,我們希望給讀者一個更好的了解時鐘抖動及其影響高速模數轉換器的性能

2017-05-15 15:20:59 13

13 的應用中是一個關鍵部分。由于其他結構諸如兩步快閃結構或內插式結構都很難在高輸入頻率下提供低諧波失真,因此流水線結構在高速低功耗的ADC應用中也成為一個比較常用的結構。 作為流水線ADC前端的采樣保持電路是整個系統的關鍵模塊電路

2017-11-16 15:23:31 1

1 是無源(使用變壓器或巴倫),具體取決于系統要求。無論哪種情況,都必須謹慎選擇元器件,以便實現在目標頻段的最優ADC性能。 簡介 射頻采樣ADC采用深亞微米CMOS工藝技術制造,并且半導體器件的物理特性表明較小的晶體管尺寸支持的最大電壓也較低

2017-11-22 17:46:05 1009

1009

本文主要討論采樣時鐘抖動對 ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。 ADC 是現代數字解調器和軟件無線電接收機中連接模擬信號處理部分和數字信號處理部分的橋梁,其性能在很大程度上決定

2017-11-27 14:59:20 17

17 的應用中是一個關鍵部分。由于其他結構諸如兩步快閃結構或內插式結構都很難在高輸入頻率下提供低諧波失真,因此流水線結構在高速低功耗的ADC應用中也成為一個比較常用的結構。 作為流水線ADC前端的采樣保持電路是整個系統的關鍵模塊電路

2017-12-07 10:45:23 5

5 1;ADC在最高速采樣的時候需要1.5+12.5個ADC周期,在14M的ADC時鐘下達到 1Msps的速度,因為我主頻是72M所以4分頻后稍微高了點,18MHZ的ADC時鐘,采樣速度應該高于1M了。ADC 采樣2路同時采樣方式,用TIM2 CC2來生成時鐘信號觸發ADC來實現指定頻率的采樣。

2018-05-18 01:44:00 24018

24018 任何高性能ADC,尤其是射頻采樣ADC,輸入或前端的設計對于實現所需的系統級性能而言很關鍵。很多情況下,射頻采樣ADC可以對幾百MHz的信號帶寬進行數字量化。前端可以是有源(使用放大器)也可以

2018-06-04 10:50:00 1894

1894

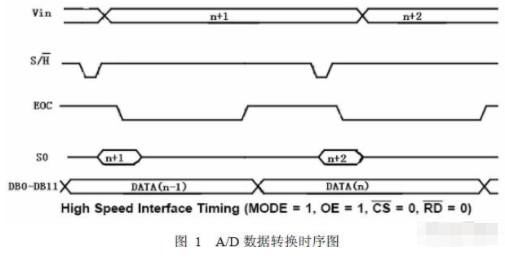

數據采集系統的總體架構如圖1所示,其中PCI核、DMA控制器與A/D控制器均在FPGA內部實現。為實現多路并行采樣,可選用多片A/D器件并行處理的方式,在FPGA的高速狀態機控制下,完成模擬信號經過

2018-08-28 10:16:07 12734

12734

的模塊,采樣保持電路的性能直接決定了整個ADC的性能,在以上系統中對功耗的要求十分嚴格。本設計在實現高速高精度采樣保持功能的同時,還實現了MDAC功能,這樣既能降低ADC功耗又能減少芯片面積。

2019-06-13 08:19:00 4768

4768

在應用C8051F020的片內高速ADC進行時間序列采樣時,編寫代碼使ADC工作于最高速度是一個難題。本文從ADC的C語言中斷模式的驅動代碼設計開始,分析對應的匯編語言中消耗CPU的主要步驟,研究

2019-09-12 08:00:00 6

6 1/14HZ = 71.4ms,一個周期采樣6000個點,則每兩個點之間的采樣間隔為:71.4ms/6000 = 71.4 / 6 us;

選擇ADC的采樣周期為71.5,則ADC時鐘頻率為:71.4 /(6 * 71.5)≈ 6MHZ。

2019-10-14 16:22:06 19056

19056

過去5年間,速度在1GSPS以上的高速ADC技術的采樣率和性能不斷提升,全新器件能夠實現RF頻譜的直接采樣。這些全新的模數轉換器 (ADC) 能夠在保持出色噪聲和線性的同時,在3GHz或更高的頻率

2020-02-07 10:55:31 2001

2001

任何高性能ADC,尤其是射頻采樣ADC,輸入或前端的設計對于實現所需的系統級性能而言很關鍵。很多情況下,射頻采樣 ADC可以對幾百MHz的信號帶寬進行數字量化。前端可以是有源(使用放大器)也可以

2020-09-29 10:44:00 0

0 本文應用的測控系統中,按照測控需求,每個信號周期內通常采樣 96 個點,采樣值累 加次數為4096 次,若采樣頻率選擇為1 MHZ,則平均每個采樣占用時間為0.393216 秒,為 了滿足測控實時性的要求。因此本系統設計中,ADC 的采樣頻率選擇為1MHZ。

2020-12-25 10:31:43 8612

8612

AN-1388: 使用AD7779 24位同步采樣Σ-型ADC實現電能質量測量的相干采樣

2021-03-20 14:37:48 14

14 AD9260:2.5 MHz輸出字率下16位分辨率的高速過采樣CMOS ADC數據表

2021-04-17 17:07:26 14

14 AD7864:4通道、同步采樣、高速、12位ADC數據表

2021-04-27 14:03:50 4

4 軟件無線電直接射頻采樣的高速ADC系統研究(開關電源技術與設計 潘永雄pdf)-該文檔為軟件無線電直接射頻采樣的高速ADC系統研究總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-16 13:35:42 19

19 STM32 ADC 過采樣技術

2021-12-08 16:21:06 41

41 project選擇芯片(此處我選的是STM32F051R8選擇結束后如下配置一下芯片的相關配置我是ST-LINK下載所以選擇SW模式.ADC是4通道采樣1-4.打開串口一.只要左邊的選項選好,右邊的芯片的引腳就自動配置好.RCC我在左側的表格里沒勾選,因為我用的是內部時鐘啊,不用

2021-12-24 19:29:29 15

15 現代接收器系統對更高容量和更多數據吞吐量的需求不斷增加。我們必須擁有高采樣率數據轉換器和高動態范圍系統。一些模數轉換器(ADC)架構確實實現了非常高的采樣率,但沒有最佳的信噪比(SNR)。其他器件可實現非常好的SNR,但其采樣率有限。沒有一個內核ADC器件同時滿足高采樣速率和動態范圍的要求。

2023-04-15 09:49:09 1242

1242

本文將幫助設計人員實現高性能、多通道、同時采樣的數據采集系統(DAS)。介紹了元器件的合理選擇及其PCB布線,以優化系統性能。Maxim的MAX1308、MAX1320和MAX11046是極具特色的同時采樣ADC。本文給出的測試數據說明了遵循設計要點能夠為系統帶來的各項益處。

2023-06-16 14:39:24 833

833

adc采樣率和帶寬的關系 ADC(Analog-to-Digital Converter),即模擬轉數字轉換器,是將模擬信號轉換成數字信號的重要器件。其中,采樣率和帶寬是ADC性能參數之一,也是

2023-09-12 10:51:12 6012

6012 運用DMA功能實現高級定時器和ADC的同步觸發采樣在做BLDC電機控制時,需要ADC的采樣時刻和定時器產生的PWM波形相配合,才能獲取準確的采樣值,本文介紹了CW32F030系列芯片通過運用DMA功能實現高級定時器和ADC的同步觸發采樣的功能。

2022-06-06 13:35:55 31

31 大家在使用ADC采樣的時候是否計算過ADC的采樣率,這個問題非常關鍵!

2024-01-23 09:29:47 560

560

電子發燒友App

電子發燒友App

評論