在復雜信號處理與通信技術的開發中,設計流程的不連續越來越具有破壞性,并且代價越來越高昂。同時,縮短設計和驗證周期的需求使設計不連續的影響被進一步被放大。本文通過介紹算法設計、系統架構和硬件設計中的幾個用例,來展示最近在建模、仿真和代碼生成工具及方法上的重要技術發展。

流系統的算法設計

現在越來越多的工程師開始用MATLAB中的浮點運算來開發信號處理與通信系統算法。這些算法開發人員可以利用MATLAB強大的信號采集和分析功能,以及多個工具箱的內置算法庫。但是,在有些團隊中,為了算法的優化實現,工程師會用C代碼重寫這些算法,將其轉換為定點或整數運算,或將它們與其他設計元素集成。該重寫步驟就是設計流程中一個潛在的,成本高昂且具有破壞性的典型不連續。

MATLAB提供的數百個用于信號處理、通信、圖像和視頻處理的新組件,都可作為System對象庫。在MATLAB中,System對象庫是為設計實時系統設計的,是即用型打包的算法實現。它們隱式地處理著流、索引、緩沖和狀態管理,使編寫、調試和維護代碼變得更簡單。

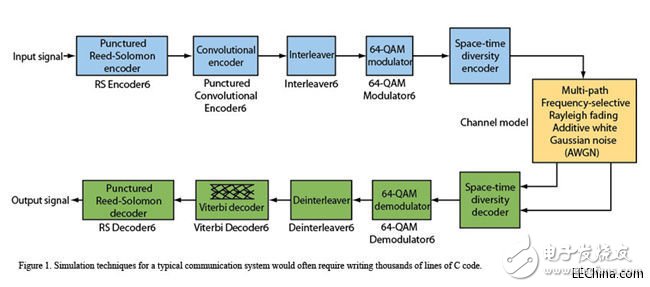

圖1顯示的是帶發射器、信道和接收器組件的基本通信系統的框圖表示形式。為了對這樣一個系統進行建模和仿真,工程師需要寫數千行的C代碼,然后,尋找各種方法,以便將設計與測試設備進行集成,或者分析仿真結果。

圖1:典型通信系統物理層的框圖。

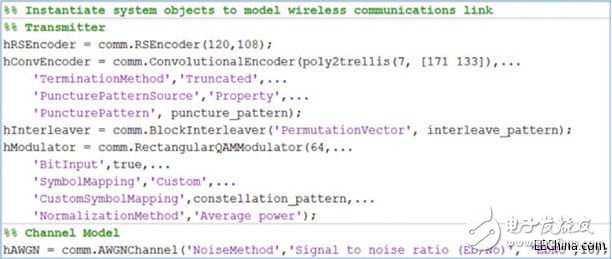

與這數千行C代碼(一般情況下為實施此通信系統而寫入的)相比,圖2中顯示的MATLAB代碼使用了來自DSP System Toolbox和Communications System Toolbox的若干個System對象。

圖2:部分MATLAB代碼,展示來自DSP System Toolbox和Communications System Toolbox的System對象的使用。

例如,要對發射器進行建模,工程師可以按順序實例化和調用Communications System Toolbox中的Reed-Solomon編碼器、卷積編碼器、區塊交織器、矩形QAM調制器和正交空時分組碼System對象(如圖2所示)。這種代碼結構讓工程師可以輕松地將其與原始規格或框圖進行對比。算法設計師則可以快速地將此代碼與其現有的MATLAB代碼相結合,并使用從測試儀器獲取的實時流數據來測試這些算法。

MATLAB與C/C++相結合#e#

MATLAB與C/C++相結合

使用System對象編碼的算法可促進系統設計流程中的代碼重用。浮點或定點型的MATLAB代碼可以作為系統架構、建模和設計流程的一部分直接包含在Simulink模型中。工程師也可以使用MATLAB Coder從MATLAB代碼自動生成C代碼,這包括System對象,在正確驗證后,使用該C代碼進行仿真,或與其他C/C++設計元素進行集成。

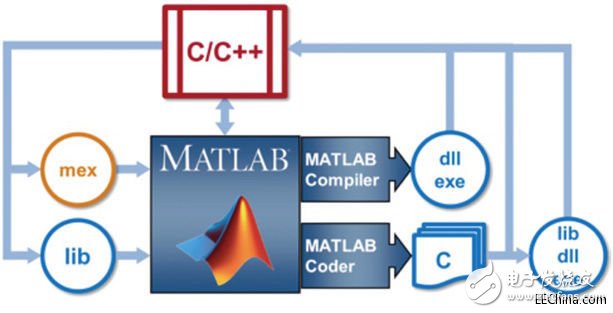

圖3展示的是工程流程中使用MATLAB與C/C++的集成而實現的幾個重要用例。例如,工程師可以從C程序直接觸發MATLAB,以利用MATLAB的信號處理庫或可視化功能;可以在MATLAB中將現有的C/C++設計直接用作外部庫;也可使用MATLAB Compiler部署MATLAB算法, 甚至可使用MATLAB Coder從MATLAB自動生成C代碼。

圖3:將MATLAB與C/C++相結合為信號處理應用提供了強大而靈活的算法及系統設計平臺。

RF和數字系統架構

在基于LTE 、藍牙、ZigBee、Wi-Fi或其他技術規范的RF設計中,第一個步驟通常是靜態鏈接預算計算。這些計算提供了良好的起點,但是它們未將輸入信號調制、鏡像效應、干擾以及其他真實的現象考慮在內。為了對通信系統的RF損失效果進行有效的建模和仿真,系統架構師會同時采用多個不相關聯的工具,它們可支持數字或模擬/RF設計,但不能同時支持兩者。

SimRF工具箱與Simulink集成,為 RF收發器中的多頻動態系統的仿真提供電路包絡引擎。SimRF工具箱包含非線性放大器、三端口混頻器、S參數模塊和其他基本模塊的行為模型,用于設計含任意拓撲的架構,并對RF前端進行系統級仿真。借助SimRF,您可以仿真RF放大器以預估增益、噪聲、奇偶階互調失真。混合器的仿真使您可以預測鏡像抑制、倒易混頻(Reciprocal mixing)、本地振蕩器相位偏移和DC轉換。您也可以在時域和頻域,對線性與非線性組件之間的頻率相關失配進行仿真。

SimRF與Simulink相結合,為在統一設計設計中對RF及基帶子系統進行建模和仿真提供了通用環境。通過結合使用這些工具,系統架構師可以在開發過程的早期完成真實的仿真,并在包含數字和模擬/RF組件的設計中做出合理的權衡決策。

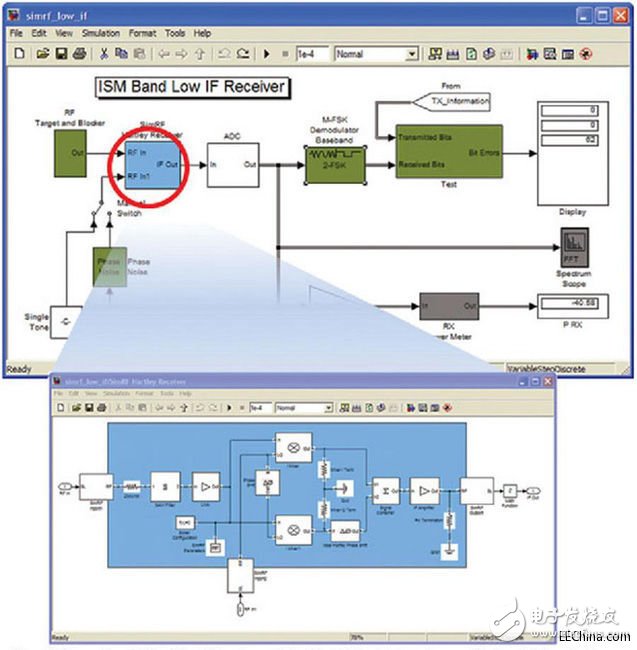

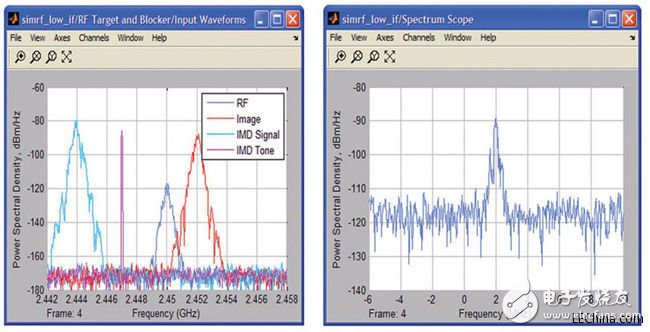

圖4顯示工作在ISM頻段上的低IF接收器的整體系統模型,包含數字信號處理組件和RF接收器子系統。圖中也顯示了采用Hartley IF接收器的RF子系統的詳細信息。與使用兩端口單元相級聯以及單頻近似值的傳統建模方法不同,使用三端口單元可簡化接收器模型。該模型也會使用電路包絡仿真技術,并支持多頻建模來估算干擾器和鏡像信號對非線性接收器的影響。

圖4:一個統一模型中的ISM頻段低IF接收器(含數字和RF子系統)(上圖),以及在SimRF中建模的Hartley接收器RF子系統的詳圖(下圖)。

系統架構師還可以在這統一的環境下來研究諸如超外差接收或直接變頻這樣的鏡像抑制方法的可行性和性能提升價值。除了對RF損失效果進行仿真外,系統架構師還可以使用設計中使用過的相同模型,來執行仿真中的驗證任務,而這些任務通常需要在試驗臺才能完成。

圖5:顯示低IF鏡像抑制結果的輸入(左側)和輸出(右側)功率譜密度圖形。

硬件設計

在完成算法設計和系統架構后,許多開發周期的下一步是FPGA實現和數字部分的驗證,有時候會作為ASIC進入最終開發。FPGA原型和實現中低效率的主要原因是耗時的設計迭代(這是尋求功耗、性能和區域達到恰當平衡所必需的)。

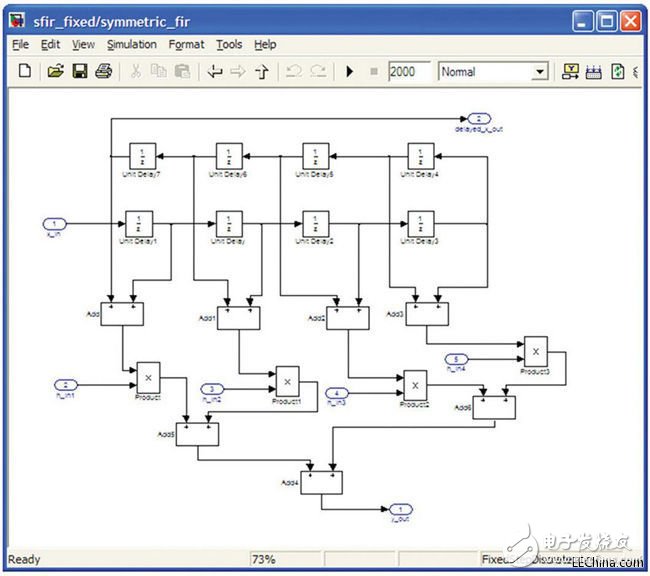

圖6顯示的是一個以定點算法來實現的對稱FIR濾波器。為實現硬件中的濾波器,工程師必須謹慎地平衡吞吐能力和延遲,并監控所用的硬件資源量。“關鍵路徑突出顯示”是一項新功能,能針對系統中的潛在瓶頸提供可操作的信息。

圖6:在Simulink中建模的對稱定點FIR濾波器。

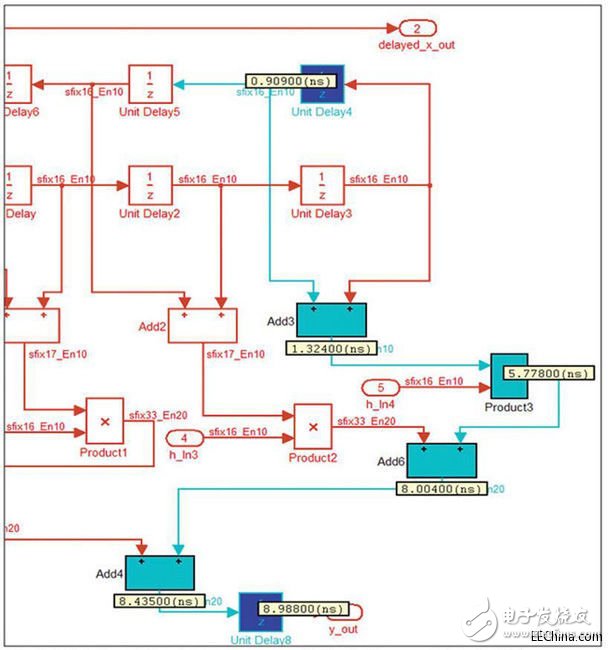

使用綜合工具生成的后綜合信息,HDL Coder可以在Simulink模型中對關鍵路徑時間進行注釋。工程師可以利用該信息與流水線技術,對他們的設計進行劃分,以減少關鍵路徑延遲,并推斷出大部分FPGA上專用DSP可用資源的使用情況。圖7展示了關鍵路徑自動突出顯示和針對每個路徑段估算延遲的相同的濾波器設計。

圖7:對稱的定點FIR濾波器,展示關鍵路徑和估算的延遲。

如上所述,流水線技術是工程師用來解決關鍵路徑延遲的主要技術之一。對于流水線技術,眾所周知的挑戰之一是并行路徑可能存在不匹配延遲,這會導致意外的系統行為。令人高興的是,用以解決這一問題的分布式流水線技術現在已實現了自動化。通過選擇該方案,工程師可以自動重定時模型,并在相關的并行路徑中平衡流水線寄存器所引入的延遲。

在過去,這些類型的設計迭代和權衡評估要求我們投入大量的時間和精力。最近,包括Workflow Advisor控制臺在內的增強,使工程師能夠以直觀的方式更快地完成設計迭代。對于那些不是特別熟悉HDL編程卻需要利用FPGA處理的人員來說,這特別有幫助。

除了使用關鍵路徑突出顯示和分布式流水線技術外,工程師還可以查看一份自動生成的資源使用報告,來監控所用的關鍵硬件組件的類型和數量,并通過對多個可行的設計方案進行快速迭代,為給定的情況確定最佳架構選擇。

加速跨團隊的設計

今天的工程經理面臨協調處理整個系統不同部分的團隊的挑戰,這些團隊位于不同地方、使用不同的工具。在許多情況下,系統級設計最好在圖形環境中完成,而某些較低級別的細節設計最好在MATLAB或C中最好以文本的形式表示。本文展示了一些提升跨設計流程各個階段的效率的最新技術發展。

對于算法設計,在建模、仿真信號處理,以及通信系統中,System對象庫是一個重要的新開發工具。現在,MATLAB中可提供數百個即用型信號處理與通信System對象。此外,System對象支持定點算法,它們可以與Simulink集成或用于自動生成C代碼。SimRF采用電路包絡仿真技術,是面向更高效系統架構流程的重要新工具。它使工程師可以在一個統一的環境中對RF和基帶系統組件進行建模,并執行真正的多頻仿真。

為了縮短硬件設計的設計迭代循環時間,HDL Coder中有多個最新的開發工具,包括Workflow Advisor、關鍵路徑突出顯示、分布式流水線技術、回注及資源利用情況報告,這提供了有關系統性能的可操作信息,并為硬件開發人員簡化工作流框架。

無論團隊是小是大,地理位置分散還是位于同一個辦公室,工程部門可以應用部分這些技術來消除其工作流程中的不連續,并借此簡化和加速復雜信號處理與通信系統的開發。

電子發燒友App

電子發燒友App

評論