?

1 引 言

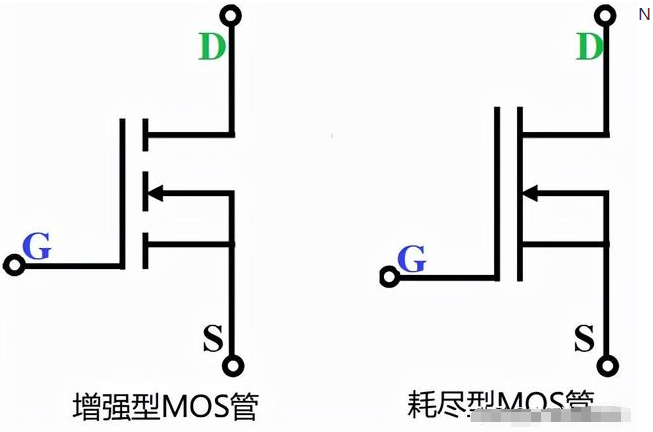

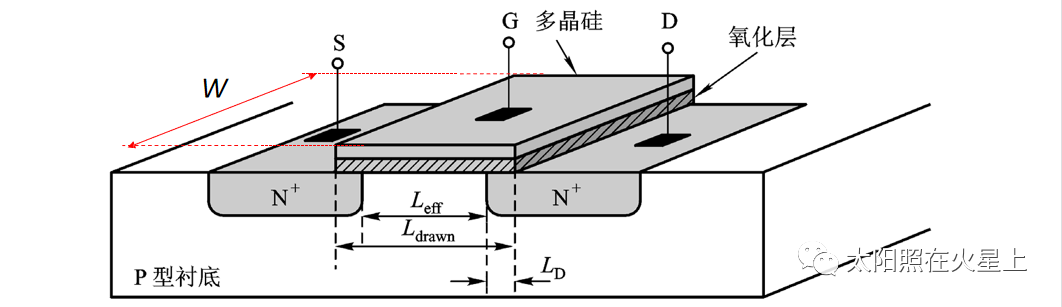

目前,實現微電路最常用的技術是使用MOS晶體管。隨著科學技術的發展,集成電路的集成密度不斷地在提高,MOS晶體管器件的尺寸也逐年縮小, 當MOS管的溝道長度小到一定值之后,出現的短溝道效應將對器件的特性產生影響,使其偏離傳統長溝道MOS管的特性

VHDL2AMS(Analog andMixed Signal)是一種高層次的混合信號硬件描述語言,它不僅支持對模擬系統的建模和仿真,而且支持對離散系統及數字模擬混合系統的建模和仿真。它對電路系統的描述既可以采用結構描述,也可以采用行為描述,即只需要描述模型的行為,而不需要聲明模型是如何實現的。

2 工作原理

當MOS管溝道縮短到一定程度,就會出現短溝道效應,其主要表現在MOS管溝道中的載流子出現速度飽和現象。在MOS管溝道較長、電場較小的情況下,載流子的速度正比于電場,即載流子的遷移率是個常數。然而在溝道電場強度很高情況下,載流子的速度將由于散射效應而趨于飽和。載流子速度v與電場的關系可用以下關系式來近似:

?

其中μn 是遷移率, E是溝道水平方向的電場, Ec是速度飽和發生時的臨界電場。溝道水平方向的電場取決于UDS /L,對于短溝道MOS管,由于溝道長度L 比長溝道MOS管小得多,因此水平方向的電場也相應大得多,隨著漏源電壓UDS的增加,很快就可以達到飽和點。因此在分析MOS管特性時,考慮到速度飽和效應,就不能沿用傳統長溝道MOS管的電流、電壓關系式,需要對其加以修正。

在線性區,漏極電流的公式原來為

?

其中ID 為漏極電流, kp 為跨導系數,W 為溝道寬度, L 為溝道長度, UT 為閾值電壓, UGS和UDS分別是柵極電壓和漏極電壓。

對于短溝道MOS管,應該修正為

?

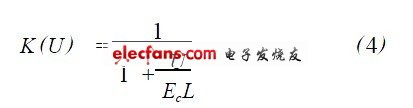

其中, K (UDS ) 因子考慮了速度飽和的因素。K(U)定義為:

?

UDS /L 可以理解為溝道中水平方向的平均電場,對于長溝道MOS管,由于L 較大, UDS /L 比Ec 小得多,因此K (UDS ) 接近于1, 而對于短溝道MOS 管,K (UDS )通常小于1,因此產生的漏極電流要比通常電流公式計算的值要小。在飽和區,漏極電流的公式原來為

?

?

其中, K (UGS - UT )因子考慮了速度飽和的因素。在(UGS - UT ) /LEc 比1大得多的情況下, ID 與(UGS -UT )不再是長溝道MOS管中的平方關系,而接近于線性關系。

3 基于VHDL 2AM S的MOS管建模

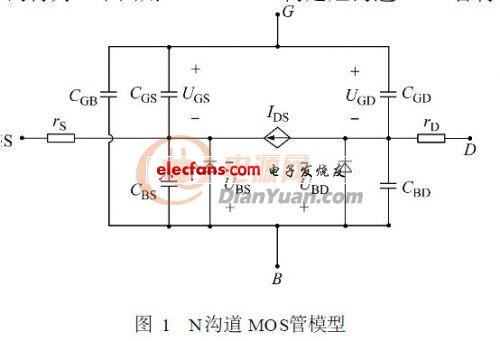

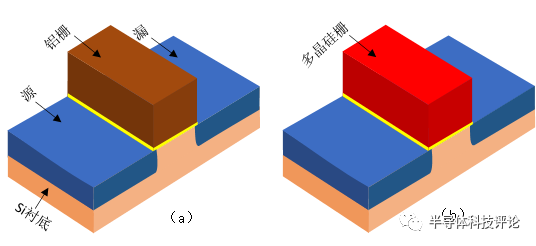

N溝道MOS管模型如圖1 所示[ 6, 7 ] , VHDL2AMS既可以針對其結構進行結構描述,也可以對其進行行為描述,即通過一些數學表達式或傳遞函數來描述對象的行為。下面用VHDL2AMS構建短溝道MOS管行為。

?

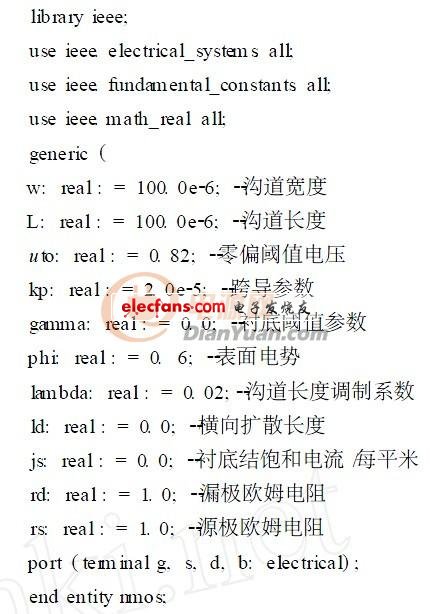

短溝道MOS管行為模型中,庫和程序包的調用以及接口參數定義如下:

?

在ieee庫中,程序包electrical_ systems中定義了電子系統中電壓、電流、電源地等基本電路變量,程序包fundamental_constants中定義了電子電荷、波耳茲曼等一些基本常數,math_real程序包則定義了各種數學運算符等。VHDL2AMS在接口定義中列出了MOS管模型中的有關參數,可以方便地進行設置和修改。由于MOS管的VHDL2AMS模型占有較大篇幅,以下僅給出短溝道MOS管VHDL2AMS模型中與前面內容相關的關鍵程序語句。

?

以上程序中, k為增益因子

k = kpW /Lk_uds = = 1. 0 / (1. 0 + uds/ ( Ec3 L) ) 對應于前述K (UDS )項; k_udssat = = 1. 0 / (1. 0 + ( ugs2u th ) /(Ec3 L) ) 對應于前述K (UGS - UT )項。可以看出,在截止區,漏極電流幾乎為零,在線性區和飽和區,漏極電流表達式分別包含k _uds和k_udssat因子,反映了

短溝道效應。此外漏極電流表達式還包含( 1. 0 +lambda3 uds)項,其中lambda為溝道長度調制系數,反映漏極電壓對溝道長度的影響。

4 分析與比較

利用混合信號仿真器SMASH5. 5, 得到VHDL2

?

AMS描述的MOS管模型的仿真結果,如圖2所示。圖中分別給出兩個MOS管的ID2UDS特性。兩個管子是具有相同W /L 比的N溝道MOS管,各項參數基本相同,比如開啟電壓UT 均為0. 5 V,主要差別在于一個是長溝道(L = 10μm) MOS管, 一個是短溝道(L =0. 2μm)MOS管。上面一條特性是長溝道MOS管特性,下面一條特性是短溝道MOS管特性。從圖中可看出,長溝道MOS管特性曲線在UDS =UGS - UT = 2 - 0. 5 = 1. 5V處飽和,符合常理。而短溝道MOS管曲線則在UDS遠低于1. 5V處就已經提前飽和。通過觀察可以發現飽和點約為0. 5V。因此短溝道MOS管的飽和區域要比長溝道MOS管更寬。

此外同在飽和區,如當UDS = 2V時,可以看到短溝道MOS管的漏極電流只是長溝道MOS管漏極電流的1 /3左右。這意味著短溝道MOS管的電流驅動能力明顯下降。

5 結 論

對于如今的深亞微米工藝,傳統的長溝道MOS管模型已經不再適用。由于速度飽和因素的影響,使得短溝道MOS管在達到UGS2UT 之前已經達到飽和狀態,因此短溝道MOS管經歷的飽和范圍更大。短溝道MOS管的VHDL2AMS行為模型仿真結果很好地揭示了這一結論。

電子發燒友App

電子發燒友App

評論