您的位置:電子發(fā)燒友網(wǎng) > 電子技術(shù)應(yīng)用 > 電源管理 > 開關(guān)電源 >

多模式開關(guān)電源控制芯片的低功耗設(shè)計(jì)方案

2012年02月08日 10:50 來源:《固體電子學(xué)研究與進(jìn)展 作者:郝炳賢,吳曉波,陳 我要評論(0)

引 言

所謂多模式控制就是在開關(guān)電源的工作中根據(jù)負(fù)載情況的不同采用不同的控制策略,以降低其功耗,提高效率。它是針對常用開關(guān)電源在輕載和待機(jī)條件下效率低的特點(diǎn)提出的,其設(shè)計(jì)思想可描述為:在重載下采用PWM 模式,以發(fā)揮其重載下效率高的優(yōu)點(diǎn);在輕載下采取PFM 模式,通過降低開關(guān)頻率來降低功耗;而在極輕載條件下(待機(jī)模式下)則采取BURST模式來降低功耗。

針對降低多模式開關(guān)電源控制芯片在輕載與待機(jī)工作模式下功耗,提高其全負(fù)載條件下工作效率的需要,提出一種開關(guān)電源控制芯片供電系統(tǒng)的設(shè)計(jì)方案,實(shí)現(xiàn)了其在啟動(dòng)、關(guān)斷、重載、輕載以及待機(jī)等各種工作情況下的高效率低功耗工作。該供電系統(tǒng)主要包括欠壓鎖定電路、數(shù)字模塊電源單元和兩種不同的模擬模塊電源單元,以及狀態(tài)檢測模塊和模式控制邏輯單元,能夠?qū)崿F(xiàn)電源的上電、掉電控制,同時(shí)能夠根據(jù)電源的負(fù)載條件控制各模塊的開通關(guān)斷以實(shí)現(xiàn)低功耗工作。該系統(tǒng)已應(yīng)用于綠色多模式反激式開關(guān)控制器的設(shè)計(jì)中,取得了提高電源效率、降低待機(jī)功耗的作用。芯片采用1.5 um BiCMOS工藝設(shè)計(jì)制成。測試表明,所設(shè)計(jì)電源的各項(xiàng)指標(biāo)均已達(dá)到設(shè)計(jì)要求。

1 系統(tǒng)與電路設(shè)計(jì)

1.1 系統(tǒng)構(gòu)成

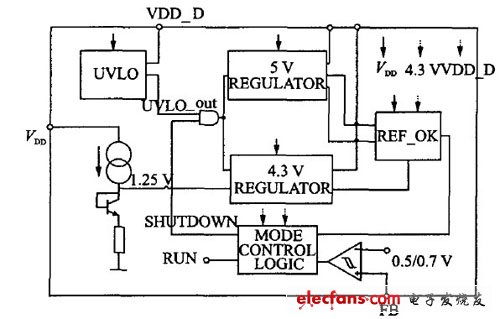

整個(gè)系統(tǒng)的構(gòu)成如圖1所示。系統(tǒng)中包括一個(gè)欠壓鎖定電路(UVLO,Under voltage lockout),用于保證電路在合適的電壓范圍內(nèi)正常工作;一個(gè)帶隙基準(zhǔn)電壓源和一個(gè)專為數(shù)字模塊供電的電壓源(記為VDD_D),分別為芯片提供基準(zhǔn)偏置和數(shù)字部分的電源。具體構(gòu)成時(shí)此兩模塊包含在UVLO模塊內(nèi)。兩個(gè)電壓調(diào)整器(REGULATOR)分別產(chǎn)生一個(gè)5 V和一個(gè)4.3 V 的穩(wěn)定電壓,其中5 V穩(wěn)定電壓源輸出記為REG,用于在重載時(shí)為控制器供電(輕載時(shí)關(guān)斷);4.3 V 穩(wěn)定電壓源輸出記為VDD_AD,用于輕載時(shí)的供電。當(dāng)然,必要時(shí)還可以利用帶隙基準(zhǔn)產(chǎn)生更多不同的電壓以滿足復(fù)雜控制模式的需要。

圖1電源系統(tǒng)框圖

此外,本設(shè)計(jì)中還設(shè)置了一個(gè)REF-OK模塊來判斷上電后電源系統(tǒng)是否已進(jìn)入正常工作狀態(tài)。

1.2 欠壓鎖定電路的設(shè)計(jì)

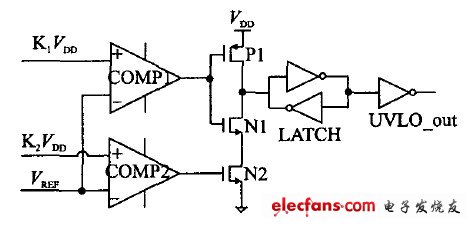

欠壓鎖定電路又稱UVLO,見圖2.圖中 VDD為芯片外部供電電源,設(shè)計(jì)值為12 V.欠壓鎖定電路的窗口設(shè)置為7~9.5 V,即上電后電壓上升到大于9.5V 時(shí)芯片開始正常工作,而當(dāng)供電電壓小于7 V時(shí)芯片停止工作。考慮到欠壓鎖定電路在電源控制芯片中的重要性,設(shè)計(jì)給出了兩種實(shí)現(xiàn)方案,并對兩種控制策略的性能進(jìn)行了分析與比較。

圖2 兩個(gè)比較器實(shí)現(xiàn)的欠壓鎖定電路

圖2給出第一種欠壓鎖定電路的原理圖,稱為U-VLO1,這是用兩個(gè)比較器實(shí)現(xiàn)的欠壓鎖定電路。VDD是外部供電電壓源,K1、K2 是小于1的常數(shù),且K1>K2,VREF為1.25 V帶隙基準(zhǔn)電壓,LATCH是由兩個(gè)反相器組成的鎖存器。圖中標(biāo)的UVLO_out代表欠壓鎖定信號(hào),狀態(tài)設(shè)置是UVLO_out=0時(shí)有效。

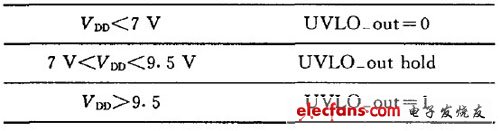

電路的工作原理可簡述如下:12 V供電電壓可在VDD比較低時(shí)建立一個(gè)PTAT (ProportiONal toabsolute temperature)電流源,然后利用其建立起帶隙基準(zhǔn)電壓源;當(dāng)VDD由0上升時(shí),帶隙基準(zhǔn)電壓r首先建立,此時(shí)兩個(gè)比較器的輸出為低電位,P1導(dǎo)通,輸出為高電位;當(dāng)K1VDD大于 r時(shí),COMP1輸出跳變,N1管導(dǎo)通,鎖存器鎖存上一個(gè)信號(hào),UVLO為高電位(注意其為低電位有效);當(dāng)K2VDD大于VREF 時(shí),N2導(dǎo)通,則UVLO-out為低電位,使能其他模塊;隨著VDD減小,K2VDD首先小于VREF,N2關(guān)斷,則鎖存器鎖存信號(hào),UVLO-out保持;當(dāng) VDD減小到K1 VDD小于VREF時(shí)COMP1跳變,P1導(dǎo)通,N1關(guān)斷,則輸出UVLO-out為高電位,關(guān)斷整個(gè)控制芯片。

表1 UVLO 的狀態(tài)對應(yīng)表

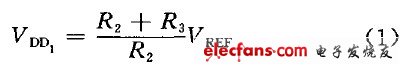

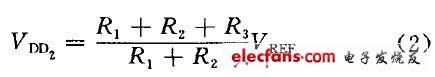

另一個(gè)方案是利用一個(gè)比較器實(shí)現(xiàn)的UVLO電路,稱UVLO2.該電路的特點(diǎn)是通過外部遲滯實(shí)現(xiàn)了欠壓鎖定功能,可應(yīng)用于高壓和低壓場合,如圖3.電路的工作原理如下:當(dāng)VDD由0上升到一個(gè)比較小的值時(shí),帶隙基準(zhǔn)電壓VREF首先建立,當(dāng)VDD上升到:

時(shí),比較器開始跳變,N1關(guān)斷,UVLO-out為0,使能整個(gè)控制芯片。當(dāng)外部電源電壓開始減小到:

時(shí),比較器跳轉(zhuǎn),N1開通,UVLO-out開始變l.通過合理設(shè)置R1、R2、R3值就可以使VDD1=9.5 V,VDD2=7V,即VDD上升到9.5 V時(shí)UVLO輸出為零,芯片正常工作; VDD下降到7 V 時(shí)芯片停止工作。

圖3 用外部遲滯實(shí)現(xiàn)的欠壓鎖定電路

兩種方案的工作特性對比結(jié)果如表2所列。需要指出的是,若直接用門電路實(shí)現(xiàn)施密特觸發(fā),由于"的工藝離散性,將使觸發(fā)電壓難以準(zhǔn)確控制。

表2 兩種欠壓鎖定電路比較

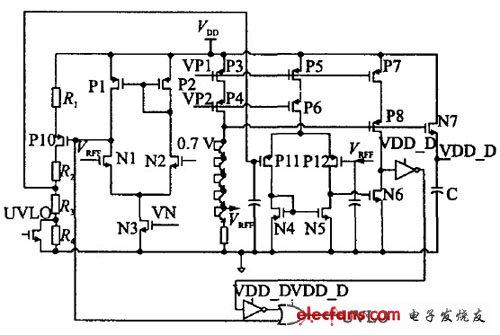

經(jīng)比較可知,UVL02結(jié)構(gòu)較為簡單,面積小,啟動(dòng)電流小,有利于降低功耗。因此,本設(shè)計(jì)最終采用了UVL02方案。此外,為最大限度減小功耗,設(shè)計(jì)中將帶隙基準(zhǔn)電壓、數(shù)字電源和欠壓鎖定電路集成在一起。具體電路圖見圖4。

圖4 欠壓鎖定和數(shù)字電源的具體電路圖

圖中利用帶隙基準(zhǔn)電壓加上四個(gè)二極管連接的三極管產(chǎn)生一個(gè)大于4 V 的電壓,然后經(jīng)過M0S管產(chǎn)生一個(gè)大約2.65 V左右的電壓。這個(gè)電壓在基準(zhǔn)電壓建立后就產(chǎn)生了,主要用于為欠壓鎖定電路的數(shù)字部分供電,并且擔(dān)任了為整個(gè)系統(tǒng)的數(shù)字電路供電的任務(wù)。

本文導(dǎo)航

- 第 1 頁:多模式開關(guān)電源控制芯片的低功耗設(shè)計(jì)方案(1)

- 第 2 頁:5 V基準(zhǔn)電壓源(REG)

- 第 3 頁:模式控制和效率測試

標(biāo)簽:開關(guān)電源(3)控制芯片(17)低功耗設(shè)計(jì)(13)

用戶評論

發(fā)表評論

開關(guān)電源業(yè)界動(dòng)態(tài)

開關(guān)電源技術(shù)應(yīng)用

開關(guān)電源資料下載

控制芯片技術(shù)應(yīng)用

控制芯片資料下載

- ISP1362 USB OTG 控制芯片及應(yīng)用

- 無USB控制芯片的AVR USB編程器的實(shí)現(xiàn)

- SD/MMC存儲(chǔ)卡控制芯片

- 基于SOPC的簡易運(yùn)動(dòng)控制芯片方案

- MC34262系列PFC控制芯片的應(yīng)用研究

- 全速USB控制芯片SL11的應(yīng)用

- SED1335中文資料 (液晶控制芯片中文手冊兼容RA8835)

- 開關(guān)電源控制芯片中減小EMI的一種電路實(shí)現(xiàn)方法

- PWM控制芯片SG3524的特殊應(yīng)用研究

- 基于DSP和電機(jī)控制芯片的交流電機(jī)控制硬件設(shè)計(jì)