您的位置:電子發燒友網 > 電子技術應用 > 電源管理 > 開關電源 >

多模式開關電源控制芯片的低功耗設計方案(2)

2012年02月08日 10:50 來源:《固體電子學研究與進展 作者:郝炳賢,吳曉波,陳 我要評論(0)

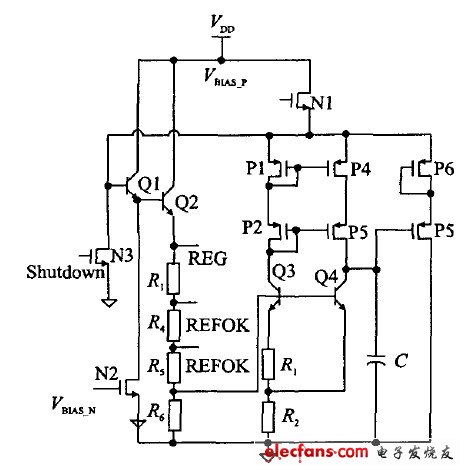

圖5為5 V穩定電壓源(REG)的電路原理。其中P1、P2、P3、P4組成共源共柵結構,可以提高電流鏡的鏡像精度,同時提高電源抑制比。Q3、Q4、R 1、R2組成一個帶隙基準電壓,這樣可以減小額外的電流支路,降低功耗。Q1、Q2組成達林頓結構,增加輸出能力。P5、P6增加匹配,減小溝道長度調制效應。Q1、Q2、R3、R4、R5、R6、Q4、P5、P6組成一個負反饋環路,將REG電壓穩定在5 V。圖中C具有兩種作用:1、記憶直流工作點;2、補償環路電容。

穩壓機理如下:當負載增加時,REG電壓下降,則Q4基極下降,集電極升高,經過P5、P6,使得Q1、Q2基極升高,REG 電壓升高;反之亦然。

REG電壓是片上多數模塊的供電電壓,驅動能力設計為4mA。

圖5 5 V 穩定電壓源

1.4 4.3 V穩定電壓源

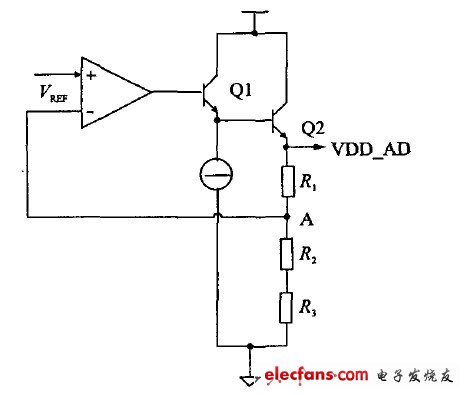

4.3 V 的穩定電壓源(VDD-AD)用來在輕載時為系統供電,始終保持工作,在BURST模式下由它為模擬模塊供電。

圖6 4.3 V 的穩定電壓源

是帶隙基準電壓,通過一個運放、一個達林頓結構的晶體管和一個電阻分壓網絡組成負反饋環路來產生4.3 V 的穩定電壓。其穩壓機理如下:當負載增大時,VDD-AD電壓下降,此時A點電壓下降,使運放的輸出上升,則Q1、Q2基極升高,REG電壓重新升高,獲得穩定;反之亦然。

VDD-AD是檢測模塊的供電電壓,設計驅動能力為2 mA.芯片負載減小時,關斷REG,減小了芯片的靜態功耗,這樣既能保證芯片的驅動能力,又同時降低了芯片的靜態功耗。

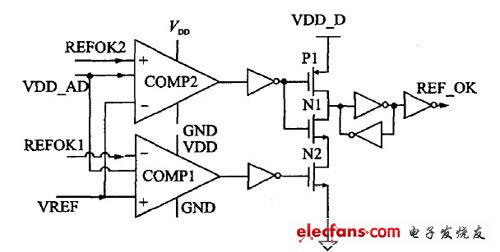

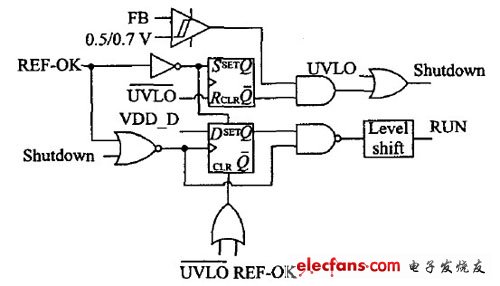

圖7 REF-OK 電路的設計

1.5 REF_OK模塊

REF_0K模塊用以標志電源系統是否建立好,以控制決定供電單元是否正常開始工作。其中兩個比較參考電平REFOK1、REF0K2的關系始終保持為REFOK1

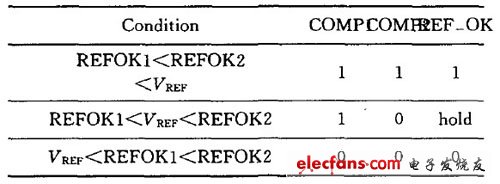

表3 REF_OK 的基本功能表

1.6 模式控制邏輯

模式控制邏輯用以保證在進行模式選擇時,電源系統正常工作。當FB電壓底于0.5 V時,該控制邏輯通過內部電流滯回比較器自動選擇進入待機模式。RUN信號(其為高電位有效)用來關斷綠色多模式反激變換器中的其它控制模塊,以實現低待機功耗。

圖8 模式控制邏輯

2.版圖設計及測試結果

2.1 版圖設計

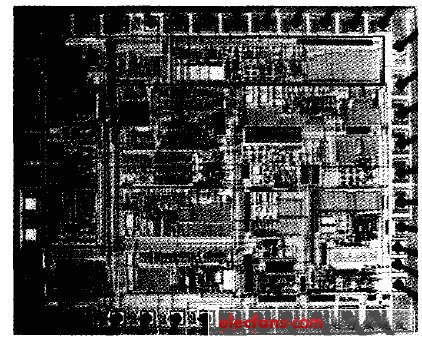

圖9給出了制得的多模式開關電源控制芯片的顯微照片,其中用線框標出的部分就是所設計的供電模塊,包括:欠壓鎖定電路,數字電源,模擬電壓源(5 V穩定電壓源,4.3 V穩定電壓源),REF_OK等子模塊。兩個模擬電壓源因功率較大,可視為熱源,將其統一放置在版圖的左邊,而PTAT、帶隙基準等敏感模塊則盡量遠離熱源,放置在版圖的右邊,欠壓鎖定電路也放置在版圖的右上角。

圖9 芯片的顯微照片

2.2 Regulator的測試

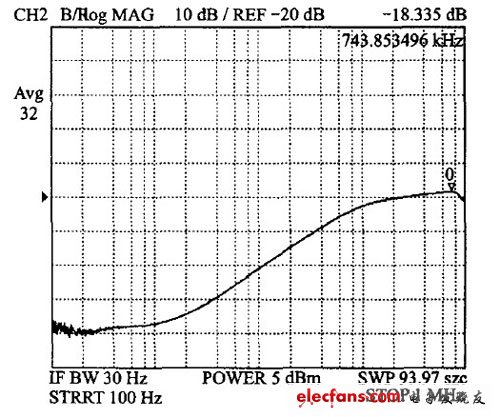

5 V 電壓的PSR測試波形如圖10所示。由此圖可見,其PSR可以達到-60 dB.該供電模塊在工作頻率為40~130 kHz的綠色多模式反激式控制器中的應用表明,它對來自電源的干擾具有較好的抑制能力。

圖10 5 V電源的PSR

2.3 供電系統的測試

UVLO的啟動電流測量值僅為17.8 A,實現了系統的低啟動電流。系統上電和掉電的測試結果如圖11和圖12所示。可見系統在VDD的設置門限內工作良好,REF-OK可以正確指示各個供電模塊正常工作。掉電過程正好相反。

圖11 供電模塊的上電和掉電過程(1)

圖12 供電模塊的上電和掉電過程(2)

本文導航

- 第 1 頁:多模式開關電源控制芯片的低功耗設計方案(1)

- 第 2 頁:5 V基準電壓源(REG)

- 第 3 頁:模式控制和效率測試