- 設計一個自己專用處理器該怎么完成?

為了實現定制指令(對原有指令集進行擴展),Cadence(Tensilica)設計了一種專用的描述語言:Tensilica Instruction Extension (TIE) language。由于Xtensa處理器有一個基本的架構模板,使用TIE語言對它進行擴展是有一定的限制,不是說你想做的指令和架構改動都能夠實現。

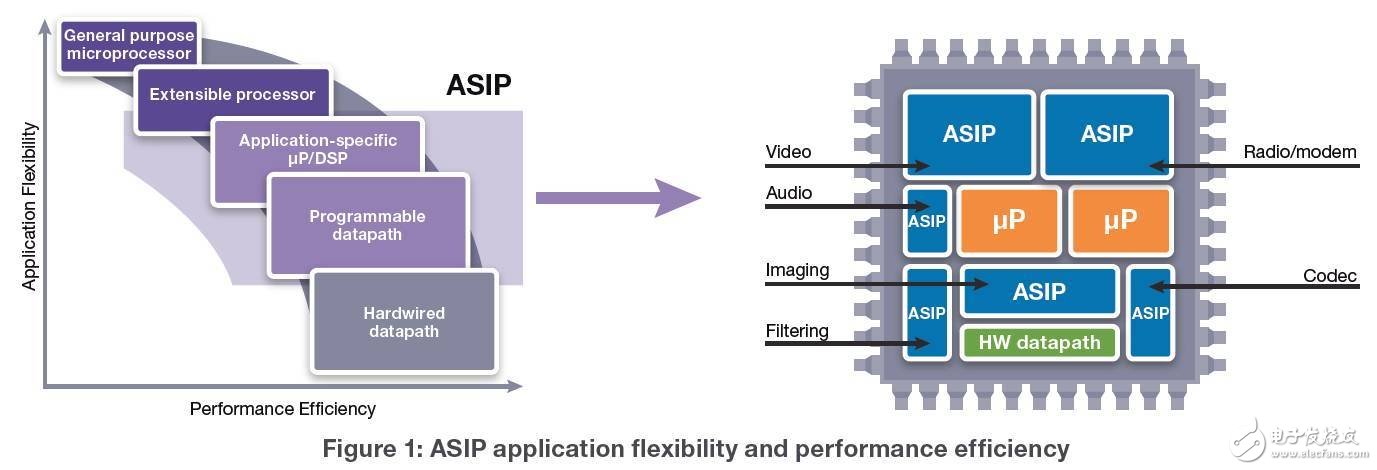

Synopsys提供的工具直接就叫ASIP designer,ASIP(Application-Specific Processor)專用處理器設計工具。和Tensilica的可擴展處理器不同,ASIP designer支持從零開始設計和實現一個專用處理器。相應的,它比Tensilica可擴展處理器有更高的靈活性。你可以非常自由的設計指令集和微結構,覆蓋從Extensible processor,到Application-specific uP/DSP,到Programmable datapath這樣一個更大的架構空間,如下圖所示。這里也可以看出,這個工具的目標并不是設計通用處理器。

轉自synopsys.com

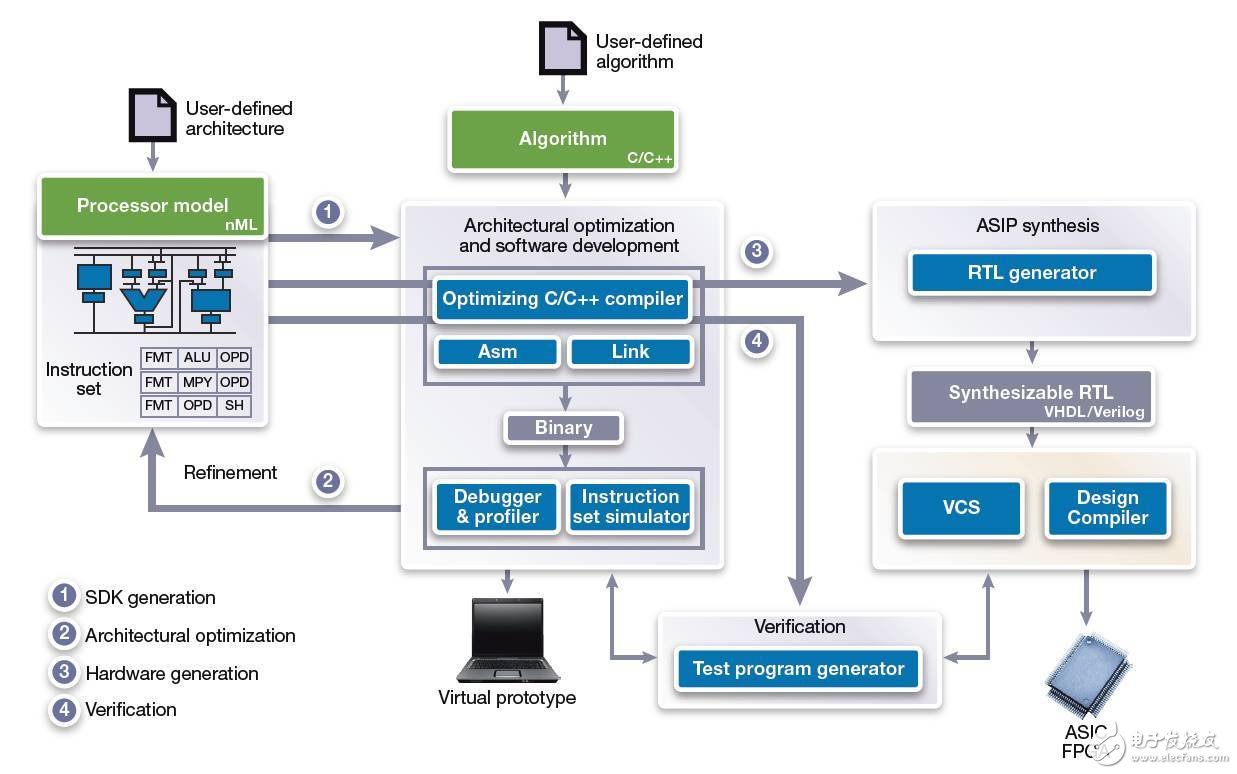

下圖是這個工具完整的方法學。

轉自synopsys.com

它的輸入就是兩個,算法(C/C++代碼)和處理器模型(Processor Model),輸出則是一個處理器相關的所有設計和工具鏈。從輸入到輸出的過程同樣是自動化完成的。當然,這個過程并不像看起來那么簡單,處理器建模的門檻不低。而且,工具賦予你的靈活性越高,掌握這種工具的門檻也越高。ASIP designer的處理器建模需要使用一種專門的語言,即nML,對處理器的指令集和架構進行高層次建模;此外還需要很多和編譯器相關的設計,(具體的信息大家可以訪問synopsys網站)。所以,即使你能買得起,要玩好這套工具,還得具備兩個條件:第一,是你必須熟悉處理器架構和編譯方面知識;第二,是要學習這套建模語言和工具。

總的來說,如果你有專用處理器設計的需求,足夠的資金和學習的耐心,可以考慮引入這類輔助設計工具。在經歷過一定的學習周期后,你不僅可以完成一個設計,還能獲得快速、高效設計處理器的能力。

窮玩法

看了上面的介紹,你是不是也對“自動”設計專用處理器的方法很眼饞呢?可惜,你可能沒有足夠的資金來購買這樣的工具,或者是你的目標收益還不值得做出這樣的投資。這種情況下,我建議你從開源的處理器(或者指令集)開始做你自己的專用處理器。其實這也算是廢話吧。所以還是得給個具體的例子,假設你想在RSIC-V的基礎上做定制處理器。RSIC-V是現在一個相對成熟的開源處理器指令,已經有很多相關實現和非常活躍的社區。相信大家都聽說過,就不科普了。這里得說明一下,我并沒有對RISC-V進行過深入的研究和嘗試,以下的說法基本上是紙上談兵,不對的地方請大家批評指正。

首先,你要好好學習一下RISC-V指令集手冊中的“Chapter 10 Extending RISC-V”,這里明確介紹了給RISC-V指令集增加指令的規則。

第二,在現有的RISC-V的硬件實現基礎上,增加新指令對應的硬件。可能需要增加專用的寄存器,運算單元,pipeline寄存器,控制信號等等。或者,你可以按照新的指令集(假設叫“RISC-V++ ISA”)自己做完整的硬件實現。其實我覺得第二種方法還更靠譜一點。很多時候,修改別人的東西,要比自己做困難的多。

第三,在RISC-V原有的工具鏈(比如GNU或者LLVM的編譯器)基礎上做出修改,支持新的指令。相對來說,這項工作是有比較完善的規則的,只要按照編譯工具的規則就可以把新增的指令加進去。當然,如果你增加的指令比較特殊,比如是向量操作,那么工具鏈的設計會困難很多。這種情況下的一個選擇是在高級程序語言的編譯器中不增加對新指令的支持,這些新的指令以匯編或者intrinsic的方法實現。

最后,這套方法是不是也能支持在第二節中所說的快速design space exploration呢?基本的思路也是差不多的。你可以先用基本指令集來仿真你的算法;根據profiling的結果(比如性能指標,指令效率,code size等)考慮對指令集進行的修改;然后更新相應的硬件實現和工具鏈,再編譯和仿真你的算法,并不斷迭代。現在你實現這個過程沒有自動化工具的幫忙,可能需要更長的時間才能完成,特別是需要對功耗面積等implementation結果進行優化的情況。當然,如果現在RSIC-V的生態中已經有了輔助設計工具,那么可能情況會輕松一些。

這種方法看起來行的通,不過中間的坑非常多,要求你對基礎處理器(比如RISC-V)非常熟悉。適合那些已經完整的做過RISC-V實現的玩家嘗試。否則,也許有的坑你根本過不去。

最后,我寫這篇文章并不是想鼓勵大家都自己做專用處理器,而是希望大家清楚做這件事情要付出的代價。

非常好我支持^.^

(0) 0%

不好我反對

(0) 0%

相關閱讀:

- [電子說] 怎樣解決霍爾搖桿耗電量大的問題?揭秘霍爾芯片的選型要求 2023-10-24

- [電子說] Blackwell GB100能否在超級計算機和AI市場保持領先優勢? 2023-10-24

- [電子說] 淺析BUCK芯片在電路中的應用及特點 2023-10-24

- [處理器/DSP] Codasip發布適用于定制計算的新一代RISC-V處理器系列產品 2023-10-24

- [電子說] OTA語音芯片NV040C在智能電動牙刷的應用 2023-10-24

- [電子說] 新思科技面向臺積公司N5A工藝技術推出領先的廣泛車規級IP組合 2023-10-24

- [電子說] 使用半大馬士革工藝流程研究后段器件集成的工藝 2023-10-24

- [電子說] 國產運放和溫度傳感器介紹 2023-10-24

( 發表人:方泓翔 )