在當(dāng)前高速發(fā)展的科技時(shí)代,系統(tǒng)級(jí)芯片(System on Chip,簡(jiǎn)稱(chēng) SoC)設(shè)計(jì)已經(jīng)成為了集成電路領(lǐng)域的研究熱點(diǎn)。

2023-09-07 09:34:17 1829

1829 為什么現(xiàn)在原來(lái)越多的模塊封裝成SOC

2023-11-02 06:47:31

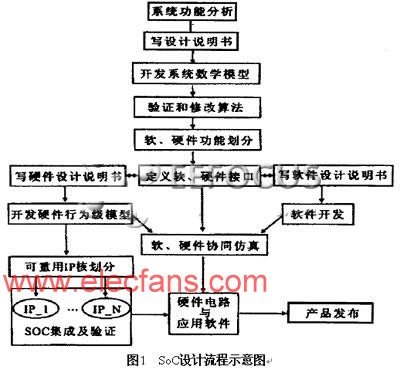

簡(jiǎn)述SOC的設(shè)計(jì)流程跟方法,以及現(xiàn)在市場(chǎng)上跟SOC設(shè)計(jì)相關(guān)的解決方案;接下來(lái)我們會(huì)將眼光轉(zhuǎn)到OPENCORES,這是一個(gè)以opensource的精神推廣IC設(shè)計(jì)的機(jī)構(gòu),筆者會(huì)介紹在OPENCORES

2023-09-20 07:24:04

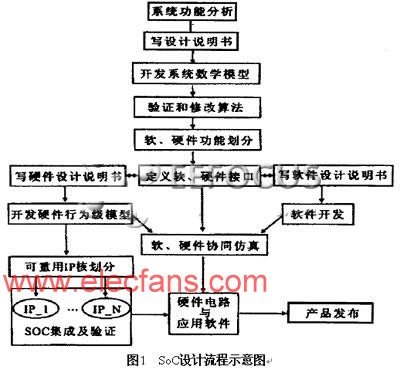

的IP(MCU、DSP,etc)。因此,作為一種軟/硬件平臺(tái),面向系統(tǒng)需求的軟/硬件協(xié)同設(shè)計(jì)技術(shù)與方法一定是決定SOC設(shè)計(jì)成敗的最關(guān)鍵因素。針對(duì)這一問(wèn)題,本文從闡述軟/硬件協(xié)同設(shè)計(jì)對(duì)SOC芯片開(kāi)發(fā)

2009-11-19 11:19:30

Altera公司意欲通過(guò)更先進(jìn)的制程工藝和更緊密的產(chǎn)業(yè)合作,正逐步強(qiáng)化FPGA協(xié)同處理器,大幅提升SoC FPGA的整體性能,為搶攻嵌入式系統(tǒng)市場(chǎng)版圖創(chuàng)造更大的差異化優(yōu)勢(shì)。隨著SoC FPGA在

2019-08-26 07:15:50

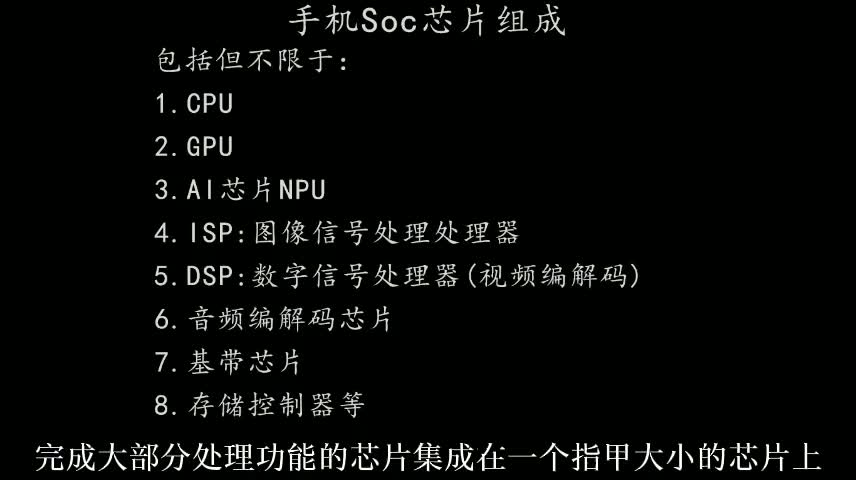

是因?yàn)?b class="flag-6" style="color: red">SoC上集成了很多手機(jī)上最關(guān)鍵的部件,比如CPU、GPU、內(nèi)存、也就說(shuō)雖然它在主板上的存在是一個(gè)芯片,但是它里邊可是由很多部件封裝組成的。比如通常我們所說(shuō)的高通801,Tegra 4,A6等等都只是系統(tǒng)部件

2021-07-28 07:57:15

SoC是什么意思?SoC是由哪些部件封裝組成的?

2021-10-19 06:07:13

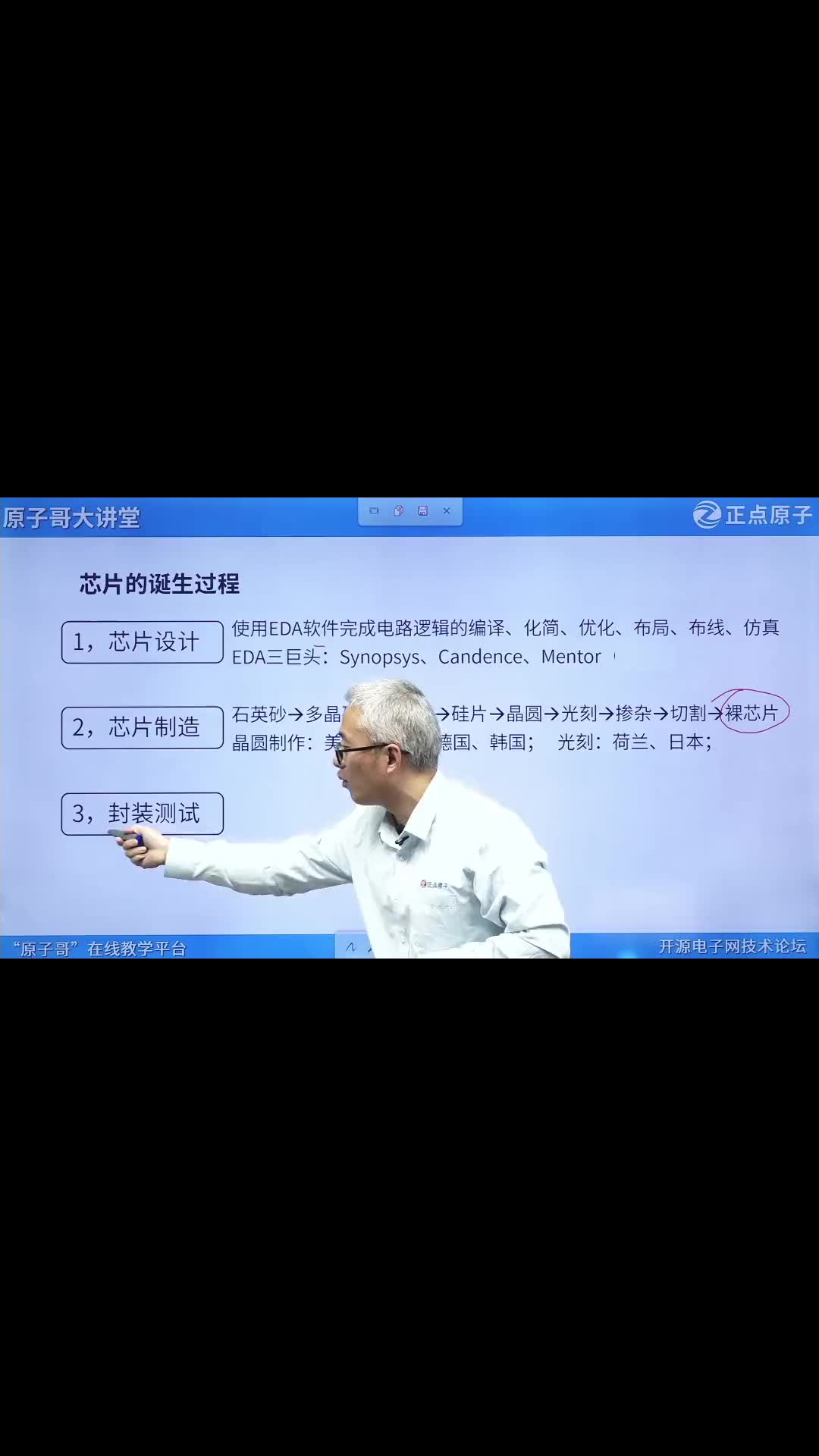

SoC,系統(tǒng)級(jí)芯片,片上系統(tǒng),是一個(gè)有專(zhuān)用目標(biāo)的集成電路,其中包含完整系統(tǒng)并有嵌入軟件的全部?jī)?nèi)容。同時(shí)它又是一種技術(shù),用以實(shí)現(xiàn)從確定系統(tǒng)功能開(kāi)始,到軟/硬件劃分,并完成設(shè)計(jì)的整個(gè)過(guò)程。從狹義角度講

2016-05-24 19:18:54

家庭娛樂(lè)市場(chǎng)上的新興標(biāo)準(zhǔn)是什么?SoC設(shè)計(jì)中杜比數(shù)字加的實(shí)現(xiàn)優(yōu)化方法是什么

2021-06-08 07:15:27

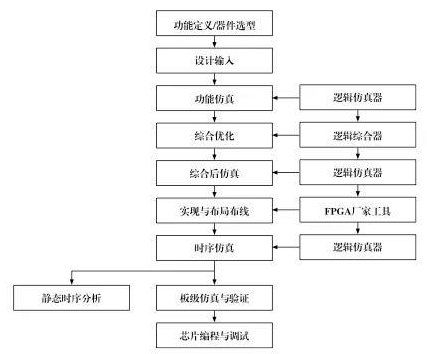

引言 隨著技術(shù)的進(jìn)一步發(fā)展,SoC設(shè)計(jì)面臨著一些諸如如何進(jìn)行軟硬件協(xié)同設(shè)計(jì),如何縮短電子產(chǎn)品開(kāi)發(fā)周期的難題。為了解決SoC設(shè)計(jì)中遇到的難題,設(shè)計(jì)方法必須進(jìn)一步優(yōu)化。因此,人們提出了基于FPGA

2019-07-12 07:25:22

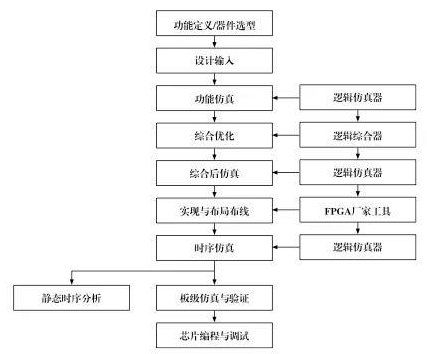

SoC設(shè)計(jì)流程一、SoC設(shè)計(jì)的特點(diǎn)二、軟硬件協(xié)同設(shè)計(jì)流程2.1 系統(tǒng)需求說(shuō)明2.2 高級(jí)算法建模與仿真2.3 軟硬件劃分過(guò)程2.4 軟硬件同步設(shè)計(jì)三、基于標(biāo)準(zhǔn)單元的SoC芯片設(shè)計(jì)流程一、SoC

2021-11-11 07:48:45

soc芯片即System-on-a-Chip,簡(jiǎn)單解釋就是系統(tǒng)級(jí)芯片。它是一個(gè)產(chǎn)品,是一個(gè)有專(zhuān)用目標(biāo)的集成電路,其中包含完整系統(tǒng)并有嵌入軟件的全部?jī)?nèi)容。同時(shí)它又是一種技術(shù),用以實(shí)現(xiàn)從確定系統(tǒng)功能

2022-01-25 07:42:31

soc計(jì)算方法,BMS中的SOC的計(jì)算其實(shí)可以分為三大部分:1、電芯層級(jí)的SOC計(jì)算(軟件中最真實(shí)的SOC計(jì)算,不涉及任何濾波處理);2、模組或者電池包層級(jí)的SOC計(jì)算(電芯到電池包級(jí)別的SOC映射

2021-07-27 06:13:05

由于技術(shù)的發(fā)展,高速電路電源設(shè)計(jì)要求三個(gè)協(xié)同:1.) SI、PI和EMI協(xié)同設(shè)計(jì);2.) 芯片、封裝和系統(tǒng)協(xié)同設(shè)計(jì);3.) 多物理場(chǎng)協(xié)同設(shè)計(jì)。

2019-11-11 17:31:44

現(xiàn)在有哪些芯片是將IC與外圍電路做在一起的(封裝成一個(gè)IC)?同事說(shuō)到后面會(huì)把晶振等較大的器件也會(huì)封裝進(jìn)去,那這種IC在后面是不是一種大趨勢(shì)?如果是這樣,怎樣能保證匹配和性能,因?yàn)?b class="flag-6" style="color: red">封裝到里,可能無(wú)法靠調(diào)整外圍電路優(yōu)化,個(gè)人還不是太懂,請(qǐng)各位發(fā)表下自己的觀點(diǎn)幫忙了解些~~

2015-07-20 11:49:43

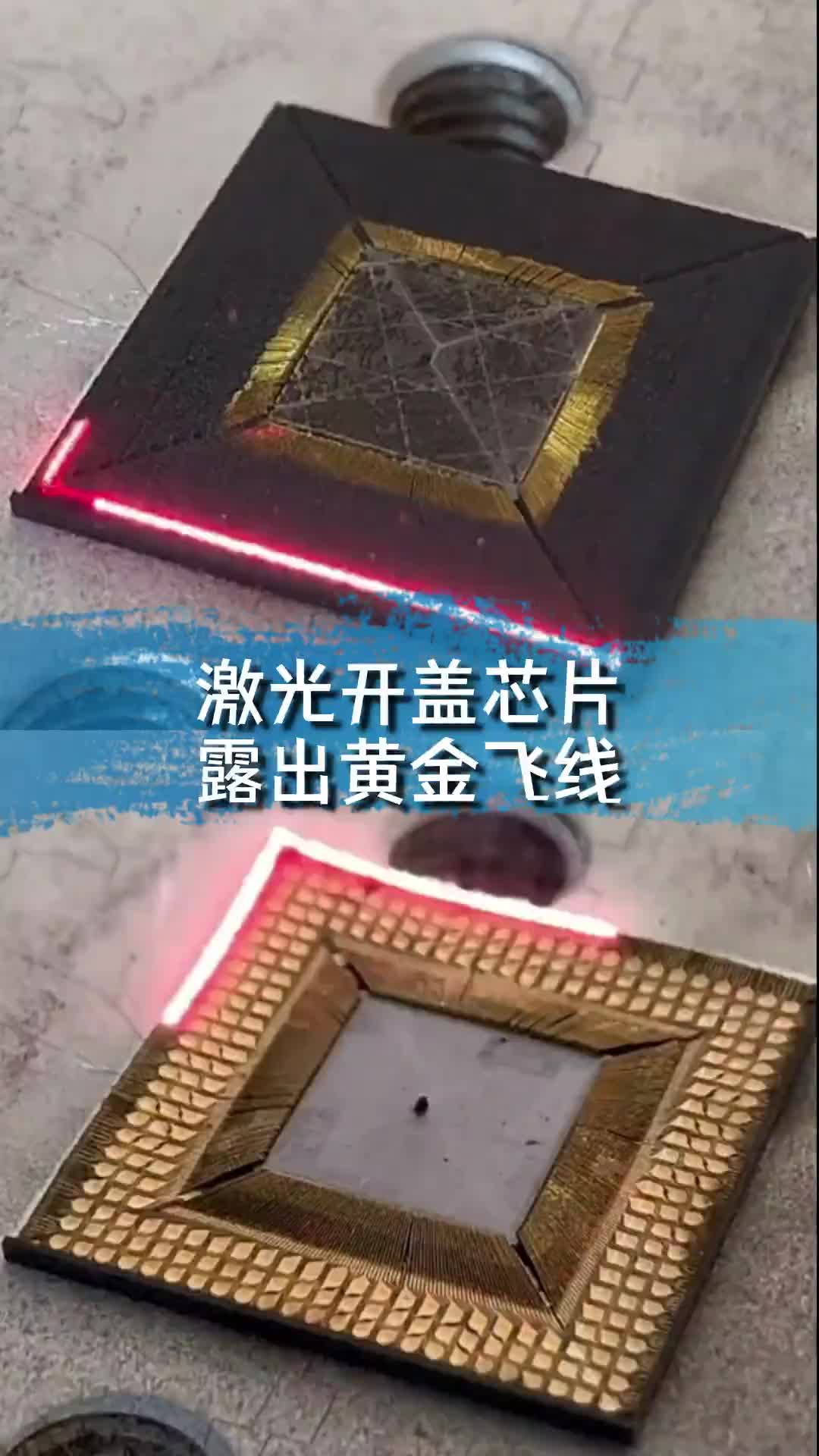

`芯片開(kāi)封也就是給芯片做外科手術(shù),通過(guò)開(kāi)封我們可以直觀的觀察芯片的內(nèi)部結(jié)構(gòu),開(kāi)封后可以結(jié)合OM分析判斷樣品現(xiàn)狀和可能產(chǎn)生的原因。開(kāi)封的含義:Decap即開(kāi)封,也稱(chēng)開(kāi)蓋,開(kāi)帽,指給完整封裝的IC做局部

2020-04-14 15:04:22

16.5開(kāi)始,Cadence能夠?qū)崿F(xiàn),根據(jù)提供的封裝與PCB板協(xié)同規(guī)劃的SoC IP從而高效實(shí)現(xiàn)系統(tǒng)級(jí)芯片。該版本的發(fā)布將提供一款封裝與PCB板協(xié)同規(guī)劃的DDR3 SoC IP方法的工具包,提供一個(gè)

2020-07-06 17:50:50

本帖最后由 hukaipanwenjing 于 2012-8-16 20:47 編輯

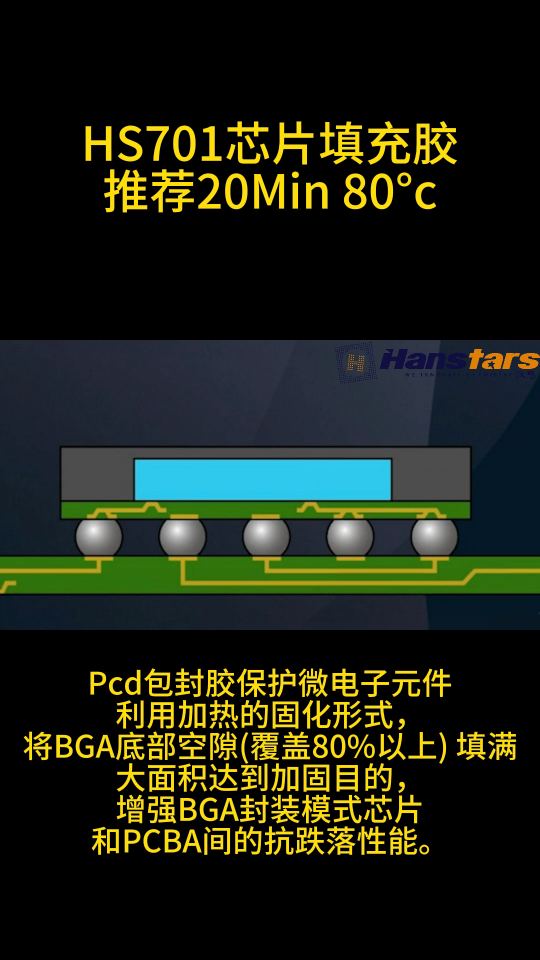

板上芯片封裝(COB),半導(dǎo)體芯片交接貼裝在印刷線路板上,芯片與基板的電氣連接用引線縫合方法實(shí)現(xiàn),芯片

2012-08-16 20:44:11

摘要:簡(jiǎn)要介紹了軟硬件協(xié)同仿真技術(shù),指出了在大規(guī)模FPGA開(kāi)發(fā)中軟硬件協(xié)同仿真的重要性和必要性,給出基于Altera FPGA的門(mén)級(jí)軟硬件協(xié)同仿真實(shí)例。 關(guān)鍵詞:系統(tǒng)級(jí)芯片設(shè)計(jì);軟硬件協(xié)同仿真

2019-07-04 06:49:19

軟硬件協(xié)同設(shè)計(jì)(Hardware/Software Co-deaign)是在20世紀(jì)90年代興起的跨領(lǐng)域交叉學(xué)科。隨著超大規(guī)模集成電路制造工藝的進(jìn)步,單個(gè)芯片所能提供的晶體管數(shù)量已經(jīng)超過(guò)了大多數(shù)

2020-04-08 08:03:10

preference-inspired coevolutionary approach基于偏好啟發(fā)協(xié)同進(jìn)化方法的混合可再生能源系統(tǒng)的多目標(biāo)優(yōu)化設(shè)計(jì)Keywords:Hybrid renewable energy systems混合可再生能源系統(tǒng);Optimization優(yōu)化;Preference-inspired coevo

2021-07-12 08:10:00

SoC設(shè)計(jì)的特點(diǎn)軟硬件協(xié)同設(shè)計(jì)流程基于標(biāo)準(zhǔn)單元的SoC芯片設(shè)計(jì)流程

2021-01-26 06:45:40

車(chē)路協(xié)同與智能協(xié)同群體智能和協(xié)同控制該怎樣實(shí)現(xiàn)

2020-12-30 07:51:36

采用遺傳算法對(duì) EKF 中的系統(tǒng)噪聲矩陣和測(cè)量矩陣的協(xié)方差進(jìn)行在線優(yōu)化,以實(shí)現(xiàn)在模型誤差最小時(shí)對(duì) SOC 進(jìn)行在線估計(jì)

2020-03-12 12:27:05

SOC 的發(fā)展趨勢(shì)是:體系結(jié)構(gòu)需要在新技術(shù)與產(chǎn)品、市場(chǎng)和應(yīng)用需求之間取得平衡;設(shè)計(jì)方法趨向于走專(zhuān)用、定制和自動(dòng)化的道路。一方面由于SOC 的專(zhuān)用化設(shè)計(jì)要求,另一方面由于IP 提供商的支持, SOC

2019-07-19 06:12:14

本文將討論通過(guò)優(yōu)化封裝內(nèi)的阻抗不連續(xù)性和改善其回波損耗性能,以滿(mǎn)足10Gbps SerDes鍵合線封裝規(guī)范。

2021-04-25 07:42:13

如何實(shí)現(xiàn)一體化芯片-封裝協(xié)同設(shè)計(jì)系統(tǒng)的設(shè)計(jì)?如何優(yōu)化封裝和芯片接口設(shè)計(jì)?

2021-04-21 07:01:10

請(qǐng)問(wèn)一下,如何利用AMSVF來(lái)進(jìn)行混合信號(hào)SoC的全芯片驗(yàn)證?

2021-05-06 07:56:08

板上芯片封裝(COB),半導(dǎo)體芯片交接貼裝在印刷線路板上,芯片與基板的電氣連接用引線縫合方法實(shí)現(xiàn),芯片與基板的電氣連接用引線縫合方法實(shí)現(xiàn),并用樹(shù)脂覆蓋以確保可靠性。雖然COB是最簡(jiǎn)單的裸芯片貼裝

2018-09-17 17:12:09

固網(wǎng)短信電話(huà)專(zhuān)用SoC芯片介紹一種數(shù)模混合SoC設(shè)計(jì)協(xié)同仿真的驗(yàn)證方法

2021-04-23 06:06:39

測(cè)量小型封裝的運(yùn)算放大器或類(lèi)似器件芯片溫度的最佳辦法是什么?測(cè)量結(jié)溫或芯片溫度的方法有幾種,某些方法較優(yōu)。高速放大器部門(mén)應(yīng)用工程師 John Ardizzoni 給大家介紹了 4 中方法——

2019-07-19 07:17:45

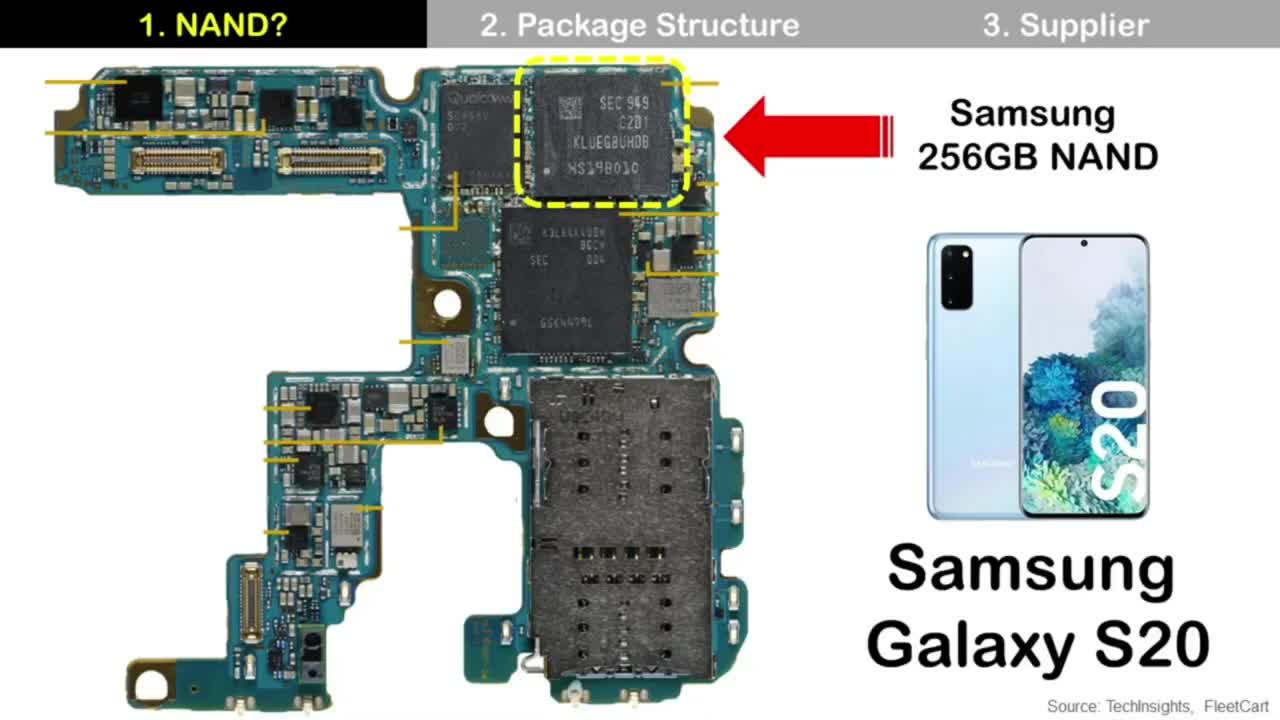

隨著行動(dòng)裝置與新興穿戴式裝置等終端產(chǎn)品需求持續(xù)成長(zhǎng),我們需要將更多種元件安裝在電路板上,以提高產(chǎn)品功能。如果各個(gè)元件都獨(dú)立封裝,組合起來(lái)將耗費(fèi)非常大的空間,因此目前有兩種方法,可滿(mǎn)足縮小體積的要求

2017-06-28 15:38:06

藍(lán)牙SOC芯片有哪個(gè)壇友對(duì)樂(lè)鑫的藍(lán)牙SOC芯片熟悉的?封裝最好是QFN24的不能比這個(gè)封裝大。需要藍(lán)牙5.0+MCU集成了,藍(lán)牙有內(nèi)置巴倫電路,一根線拉出來(lái)就可以,不需要用被動(dòng)器件調(diào)匹配電路!至少有兩個(gè)ADC口,一個(gè)IIC,一個(gè)UART,需要低功耗推薦下,只想用國(guó)產(chǎn)

2021-09-09 17:25:33

高速電路多物理場(chǎng)的芯片-封裝-系統(tǒng)(CPS)的協(xié)同SI-PI-EMI仿真

2019-11-13 08:56:06

` 由于技術(shù)的發(fā)展,高速電路設(shè)計(jì)要求三個(gè)協(xié)同:1.) SI、PI和EMI協(xié)同設(shè)計(jì);2.) 芯片、封裝和系統(tǒng)協(xié)同設(shè)計(jì);3.) 多物理場(chǎng)協(xié)同設(shè)計(jì)。https://bbs.elecfans.com/jishu_1882790_1_1.html`

2019-11-12 09:49:47

數(shù)模混合信號(hào)仿真已經(jīng)成為SoC芯片驗(yàn)證的重要環(huán)節(jié)。文章以一款固網(wǎng)短信電話(huà)專(zhuān)用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協(xié)同仿真環(huán)境進(jìn)行仿真的驗(yàn)證方法,并給出驗(yàn)證結(jié)

2009-05-15 15:41:26 19

19 數(shù)模混合信號(hào)仿真已經(jīng)成為SoC芯片驗(yàn)證的重要環(huán)節(jié)。文章以一款固網(wǎng)短信電話(huà)專(zhuān)用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協(xié)同仿真環(huán)境進(jìn)行仿真的驗(yàn)證方法,并給出驗(yàn)證結(jié)

2009-05-15 15:41:26 5

5 本文介紹了以超深亞微米技術(shù)為支撐的 SOC 的定義以及芯片設(shè)計(jì)方法,并闡述了軟硬件協(xié)同設(shè)計(jì)理論、IP 核生成及復(fù)用技術(shù)、超深亞微米IC 設(shè)計(jì)面對(duì)的難題以及SOC 測(cè)試與驗(yàn)證技術(shù)。

2009-06-19 09:28:12 35

35 以 IP(Intellectual Property )核復(fù)用為基礎(chǔ)的SoC(System on a Chip,簡(jiǎn)稱(chēng)SoC)設(shè)計(jì)是以軟硬件協(xié)同設(shè)計(jì)為主要設(shè)計(jì)方法的芯片設(shè)計(jì)技術(shù)。本文從IP 核復(fù)用技術(shù)、軟硬件協(xié)同設(shè)計(jì)技術(shù)兩個(gè)方面

2009-08-10 08:32:17 18

18 基于SOC 的USB 主設(shè)備的軟硬件協(xié)同驗(yàn)證李棟1,李正衛(wèi)2(桂林電子科技大學(xué)通信與信息工程系,廣西 桂林 541004)摘 要:本文首先介紹了SOC 軟硬件協(xié)同驗(yàn)證方法及其平臺(tái)Seamless

2009-12-14 11:31:21 15

15 研究表明協(xié)同推薦技術(shù)容易受到攻擊。由于現(xiàn)有的檢測(cè)模型對(duì)低填充規(guī)模攻擊的檢測(cè)效果不理想,本文結(jié)合檢測(cè)模型特點(diǎn),改進(jìn)Pearson相似度計(jì)算方法。其思想是,降低共同評(píng)分項(xiàng)目對(duì)用

2010-03-01 15:33:59 15

15 (COB)板上芯片封裝焊接方法及封裝流程

板上芯片(Chip On Board, COB)工藝過(guò)程首先是在基底表面用導(dǎo)熱環(huán)氧樹(shù)脂(一般用摻銀

2009-11-19 09:10:30 2305

2305 SOC設(shè)計(jì)方法

本文通過(guò)對(duì)集成電路IC技術(shù)發(fā)展現(xiàn)狀的討論和歷史回顧,特別是通過(guò)對(duì)電子整機(jī)設(shè)計(jì)技術(shù)發(fā)展趨勢(shì)的探討,引入系統(tǒng)芯片(System on Chip,簡(jiǎn)稱(chēng)S

2009-12-08 15:48:27 779

779

什么是soc芯片

SoC(System on Chip)。SoC是在一個(gè)芯片上由于廣泛使用預(yù)定制模塊IP而得以快速開(kāi)發(fā)的集成電路。

2010-09-10 22:50:51 45585

45585

在高層次對(duì)系統(tǒng)進(jìn)行功耗佑算和功耗優(yōu)化是soc設(shè)計(jì)的關(guān)健技術(shù)本文首先給出soc設(shè)計(jì)的特點(diǎn)和流程,然后綜述目前高層次功耗估算和功耗優(yōu)化的常用方法和技術(shù),重點(diǎn)論述寄存器傳輸級(jí)和

2011-12-27 16:42:38 46

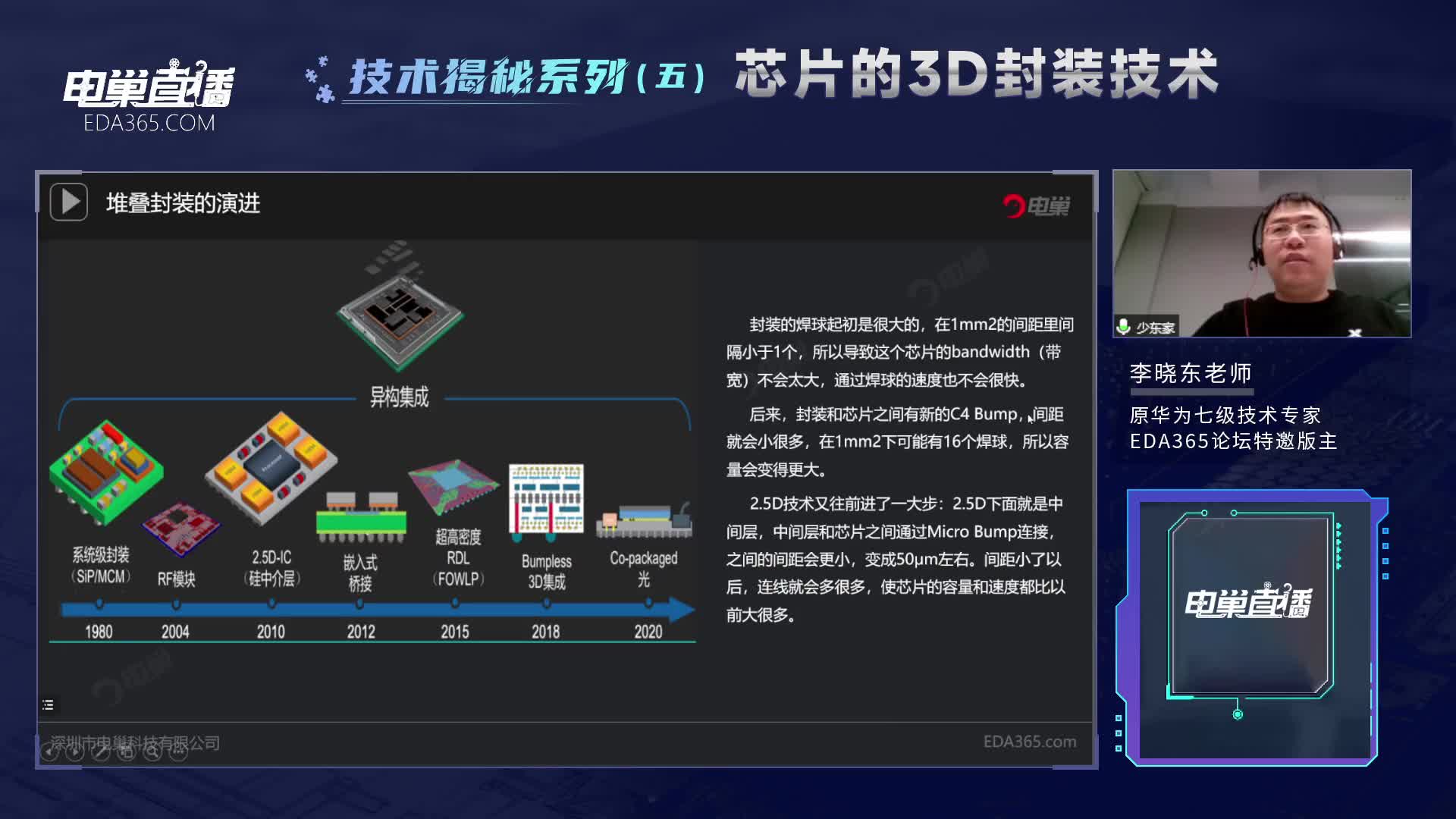

46 芯片堆疊封裝是提高存儲(chǔ)卡類(lèi)產(chǎn)品存儲(chǔ)容量的主流技術(shù)之一,采用不同的芯片堆疊方案,可能會(huì)產(chǎn)生不同的堆疊效果。針對(duì)三種芯片堆疊的初始設(shè)計(jì)方案進(jìn)行了分析,指出了堆疊方案失

2012-01-09 16:14:14 42

42 基于集成電路規(guī)模與設(shè)計(jì)工藝不斷發(fā)展的現(xiàn)狀,SI問(wèn)題日益突出和嚴(yán)重。系統(tǒng)介紹了SOC設(shè)計(jì)SI的概念、分類(lèi)及產(chǎn)生基理,根據(jù)電路工程設(shè)計(jì)經(jīng)驗(yàn),重點(diǎn)闡述了在SOC設(shè)計(jì)SI的設(shè)計(jì)、優(yōu)化、分

2012-04-12 14:31:05 35

35 SoC基于IP設(shè)計(jì)的特點(diǎn)使驗(yàn)證項(xiàng)目中多語(yǔ)言VIP(Verification IP)協(xié)同驗(yàn)證的需求不斷增加,給驗(yàn)證工作帶來(lái)了很大的挑戰(zhàn)。為了解決多語(yǔ)言VIP在SoC驗(yàn)證環(huán)境靈活重用的問(wèn)題。提出了一種

2015-12-31 09:25:13 12

12 基于SOC調(diào)控的用于抑制光伏波動(dòng)的電池儲(chǔ)能優(yōu)化控制方法

2017-01-13 13:26:03 12

12 基于CMGA的SoC測(cè)試多目標(biāo)優(yōu)化研究_談恩民

2017-01-07 18:39:17 1

1 開(kāi)關(guān)磁阻電機(jī)多目標(biāo)協(xié)同優(yōu)化設(shè)計(jì)_宋受俊

2017-01-08 11:28:38 0

0 關(guān)于協(xié)同空戰(zhàn)目標(biāo)分配效能優(yōu)化策略仿真_安超

2017-03-19 19:04:39 0

0 設(shè)計(jì)了一種基于FPGA的驗(yàn)證平臺(tái)及有效的SoC驗(yàn)證方法,介紹了此FPGA驗(yàn)證軟硬件平臺(tái)及軟硬件協(xié)同驗(yàn)證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗(yàn)證SoC系統(tǒng)的過(guò)程和方法。利用此軟硬件協(xié)同驗(yàn)證

2017-11-17 03:06:01 13138

13138

設(shè)計(jì)了一種基于FPGA的驗(yàn)證平臺(tái)及有效的SoC驗(yàn)證方法,介紹了此FPGA驗(yàn)證軟硬件平臺(tái)及軟硬件協(xié)同驗(yàn)證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗(yàn)證SoC系統(tǒng)的過(guò)程和方法。利用此軟硬件協(xié)同驗(yàn)證

2017-11-17 03:06:01 3769

3769

針對(duì)協(xié)同優(yōu)化算法迭代次數(shù)多、易收斂于局部極值點(diǎn)問(wèn)題,提出一種全局快速尋優(yōu)的協(xié)同優(yōu)化算法。在系統(tǒng)級(jí)一致性等式約束中采用改進(jìn)后松弛因子,改進(jìn)動(dòng)態(tài)松弛因子使優(yōu)化設(shè)計(jì)點(diǎn)快速收斂于極值點(diǎn),靜態(tài)松弛因子使優(yōu)化

2017-11-17 15:01:58 2

2 針對(duì)協(xié)同優(yōu)化過(guò)程對(duì)初始點(diǎn)敏感以及容易陷入局部最優(yōu)點(diǎn)的問(wèn)題,提出了一種改進(jìn)的協(xié)同優(yōu)化算法。改進(jìn)后的協(xié)同優(yōu)化算法綜合考慮學(xué)科級(jí)優(yōu)化設(shè)計(jì)點(diǎn)與系統(tǒng)級(jí)設(shè)計(jì)點(diǎn)的距離以及子學(xué)科級(jí)內(nèi)部最優(yōu)設(shè)計(jì)點(diǎn),能較好地減弱優(yōu)化

2017-11-24 14:46:02 1

1 空調(diào)作為具有熱存儲(chǔ)特性負(fù)荷的典型,具有被納入電力系統(tǒng)調(diào)度控制體系的潛能。設(shè)計(jì)了含可控空調(diào)負(fù)荷群的調(diào)度控制構(gòu)架,提出了一種計(jì)及空調(diào)負(fù)荷群控制的源一荷協(xié)同優(yōu)化調(diào)度模型方法。對(duì)基于多樣性保持的空調(diào)負(fù)荷

2018-01-03 10:29:45 12

12 在一個(gè)芯片上,包括核心處理器、存儲(chǔ)單元、硬件加速單元以及眾多的外部設(shè)備接口等,具有設(shè)計(jì)周期長(zhǎng)、實(shí)現(xiàn)成本高等特點(diǎn),因此其設(shè)計(jì)方法必然是自頂向下的從系統(tǒng)級(jí)到功能模塊的軟、硬件協(xié)同設(shè)計(jì),達(dá)到軟、硬件的無(wú)縫結(jié)合。

2020-07-13 09:53:57 2618

2618

電子發(fā)燒友網(wǎng)為你提供4/5G協(xié)同優(yōu)化方法的研究資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶(hù)指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-18 08:49:37 2

2 智能駕駛越來(lái)越進(jìn)入大眾生活的同時(shí),汽車(chē)芯片的類(lèi)型從之前的成熟封裝向先進(jìn)封裝演進(jìn),同時(shí)對(duì)測(cè)試的要求也愈加復(fù)雜。在保證芯片功能安全性的條件下如何優(yōu)化測(cè)試的方法是其中重要的挑戰(zhàn)。 月芯科技(ISE

2021-06-01 10:37:25 3916

3916 SoC設(shè)計(jì)流程一、SoC設(shè)計(jì)的特點(diǎn)二、軟硬件協(xié)同設(shè)計(jì)流程2.1 系統(tǒng)需求說(shuō)明2.2 高級(jí)算法建模與仿真2.3 軟硬件劃分過(guò)程2.4 軟硬件同步設(shè)計(jì)三、基于標(biāo)準(zhǔn)單元的SoC芯片設(shè)計(jì)流程一、SoC

2021-11-06 16:21:01 37

37 本文分別從芯片設(shè)計(jì)技術(shù)和芯片封裝技術(shù)的維度,針對(duì)解決電子產(chǎn)品對(duì)芯片小型化、性能優(yōu)、功能 強(qiáng)的要求,對(duì) SOC 片上系統(tǒng)及 HIC、MCM、SIP 封裝技術(shù)的特點(diǎn)進(jìn)行分析,并給出其相互關(guān)系,最終

2022-05-05 11:26:18 5

5 (Signal Integrity, SI)、電源完整性 (Power

Integrity, PI) 及可靠性優(yōu)化。總結(jié)了目前 2.5D/3D 芯片仿真進(jìn)展與挑戰(zhàn),介紹了基于芯片模型的

Ansys 芯片-封裝-系統(tǒng) (CPS) 多物理場(chǎng)協(xié)同仿真方法,闡述了如何模擬芯片在真實(shí)工況下達(dá)到優(yōu)化

芯片信

2022-05-06 15:20:42 8

8 系統(tǒng)級(jí)封裝 (SiP) 是一種用于將多個(gè)集成電路 (IC) 和無(wú)源元件捆綁到一個(gè)封裝中的方法,它們?cè)谠?b class="flag-6" style="color: red">封裝下協(xié)同工作。這與片上系統(tǒng) (SoC) 形成對(duì)比,而這些芯片上的功能集成到同一芯片中。

2023-03-27 11:46:45 649

649 英特爾和Arm達(dá)成了一項(xiàng)合作協(xié)議,英特爾代工服務(wù)(Intel Foundry Services)和Arm將會(huì)進(jìn)行設(shè)計(jì)技術(shù)協(xié)同優(yōu)化,這意味著讓芯片設(shè)計(jì)者能夠基于英特爾18A制程打造低功耗的SoC

2023-04-19 14:31:23 914

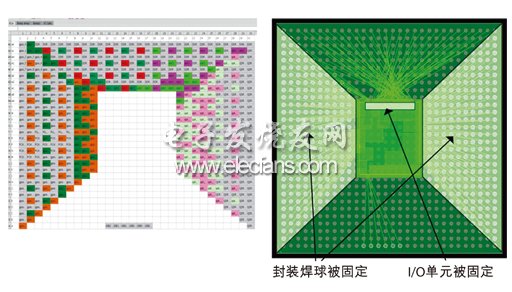

914 芯片與封裝之間,封裝內(nèi)各芯片之間,以區(qū)封裝與印制電路板(PCB)之間存在交互作用,采用芯片-封裝-PCB 協(xié)同設(shè)計(jì)可以優(yōu)化芯片、封裝乃至整個(gè)系統(tǒng)的性能,減少設(shè)計(jì)迭代,縮短設(shè)計(jì)周期,降低設(shè)計(jì)成本。

2023-05-14 10:23:34 1488

1488

多芯片封裝技術(shù)是一種將多個(gè)芯片封裝在同一個(gè)封裝體內(nèi)的集成封裝技術(shù)。在傳統(tǒng)的單芯片封裝中,一個(gè)封裝體內(nèi)只封裝一個(gè)芯片,而多芯片封裝技術(shù)將多個(gè)芯片封裝在一個(gè)封裝體中,實(shí)現(xiàn)了不同功能芯片的集成和協(xié)同工作。

2023-05-24 16:22:31 672

672 CSP(Chip Scale Package)封裝芯片是一種高密度、小尺寸的封裝形式,它在集成電路行業(yè)中具有廣泛的應(yīng)用。對(duì)于CSP封裝芯片的測(cè)試方法而言,主要涉及到以下幾個(gè)方面:

2023-06-03 10:58:16 1142

1142 AI芯片和SoC芯片都是常見(jiàn)的芯片類(lèi)型,但它們之間有些區(qū)別。本文將介紹AI芯片和SoC芯片的區(qū)別。

2023-08-07 17:38:19 2103

2103 引言 在芯片設(shè)計(jì)中,IP設(shè)計(jì)(Intellectual Property design)和SOC設(shè)計(jì)(System on a Chip design)都是常用的設(shè)計(jì)方法。這兩種設(shè)計(jì)方法都旨在將多個(gè)

2023-08-24 10:10:44 1886

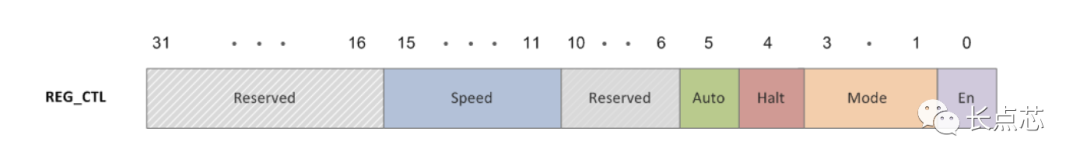

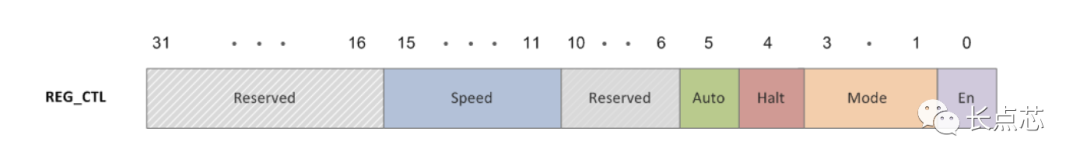

1886 就像芯片本身一樣,SoC上的CSR設(shè)計(jì)也沿用了層級(jí)設(shè)計(jì)的方法。從最底層往上,寄存器可以被分為以下幾個(gè)層級(jí)。

2023-10-20 10:39:39 394

394

SiP系統(tǒng)級(jí)封裝、SOC芯片和合封芯片技術(shù)都是重要的芯片封裝技術(shù),在提高系統(tǒng)性能、穩(wěn)定性和功耗效率方面有重要作用,但它們?cè)诩煞绞健?yīng)用領(lǐng)域和技術(shù)特點(diǎn)等方面存在區(qū)別。

2023-11-24 09:06:18 288

288

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論