在當前高速發展的科技時代,系統級芯片(System on Chip,簡稱 SoC)設計已經成為了集成電路領域的研究熱點。

2023-09-07 09:34:17 1829

1829 為什么現在原來越多的模塊封裝成SOC

2023-11-02 06:47:31

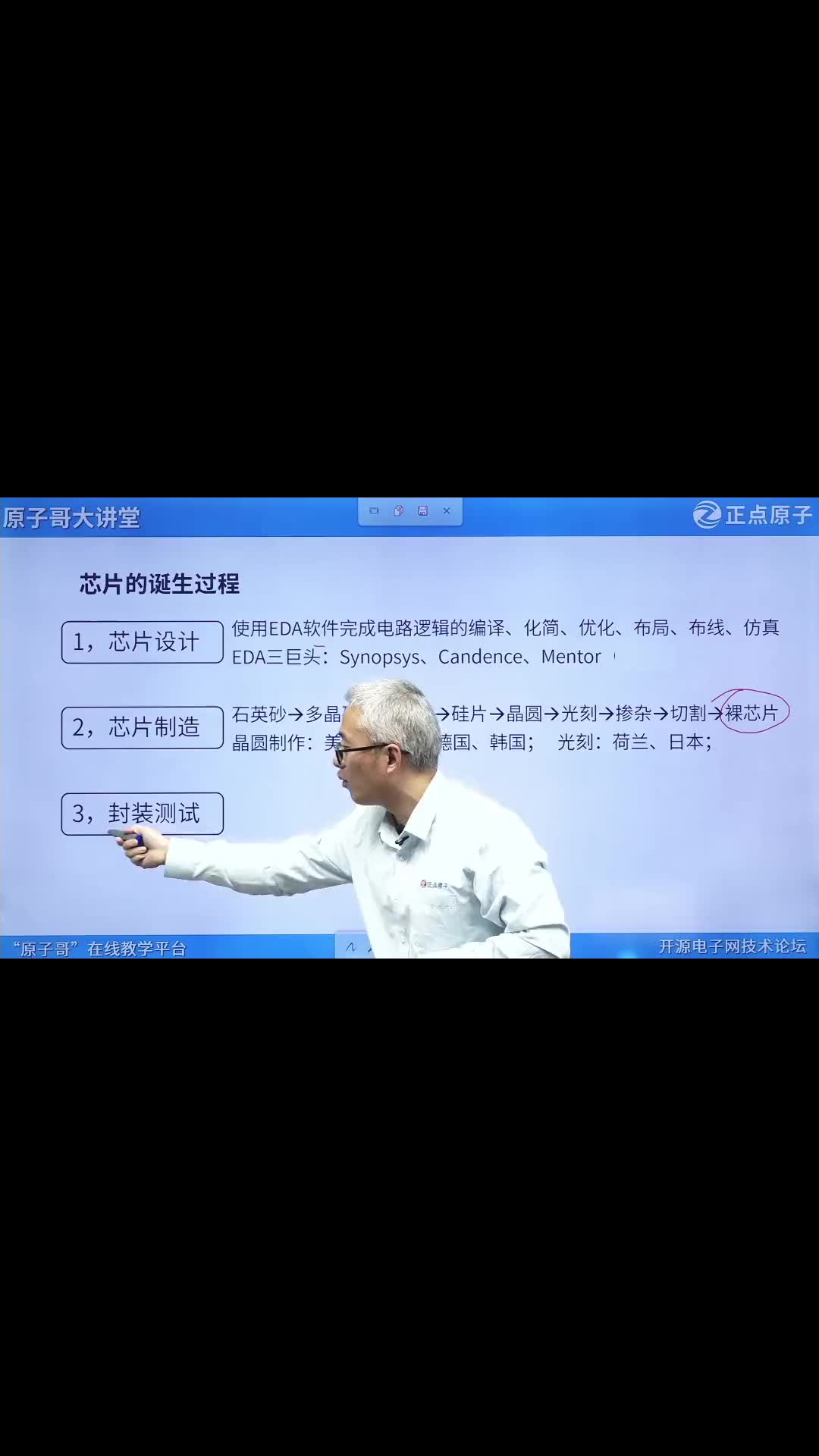

簡述SOC的設計流程跟方法,以及現在市場上跟SOC設計相關的解決方案;接下來我們會將眼光轉到OPENCORES,這是一個以opensource的精神推廣IC設計的機構,筆者會介紹在OPENCORES

2023-09-20 07:24:04

的IP(MCU、DSP,etc)。因此,作為一種軟/硬件平臺,面向系統需求的軟/硬件協同設計技術與方法一定是決定SOC設計成敗的最關鍵因素。針對這一問題,本文從闡述軟/硬件協同設計對SOC芯片開發

2009-11-19 11:19:30

Altera公司意欲通過更先進的制程工藝和更緊密的產業合作,正逐步強化FPGA協同處理器,大幅提升SoC FPGA的整體性能,為搶攻嵌入式系統市場版圖創造更大的差異化優勢。隨著SoC FPGA在

2019-08-26 07:15:50

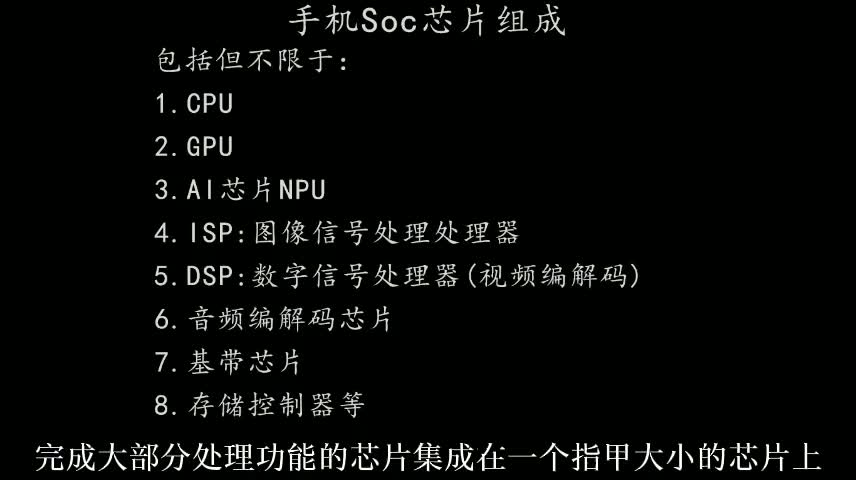

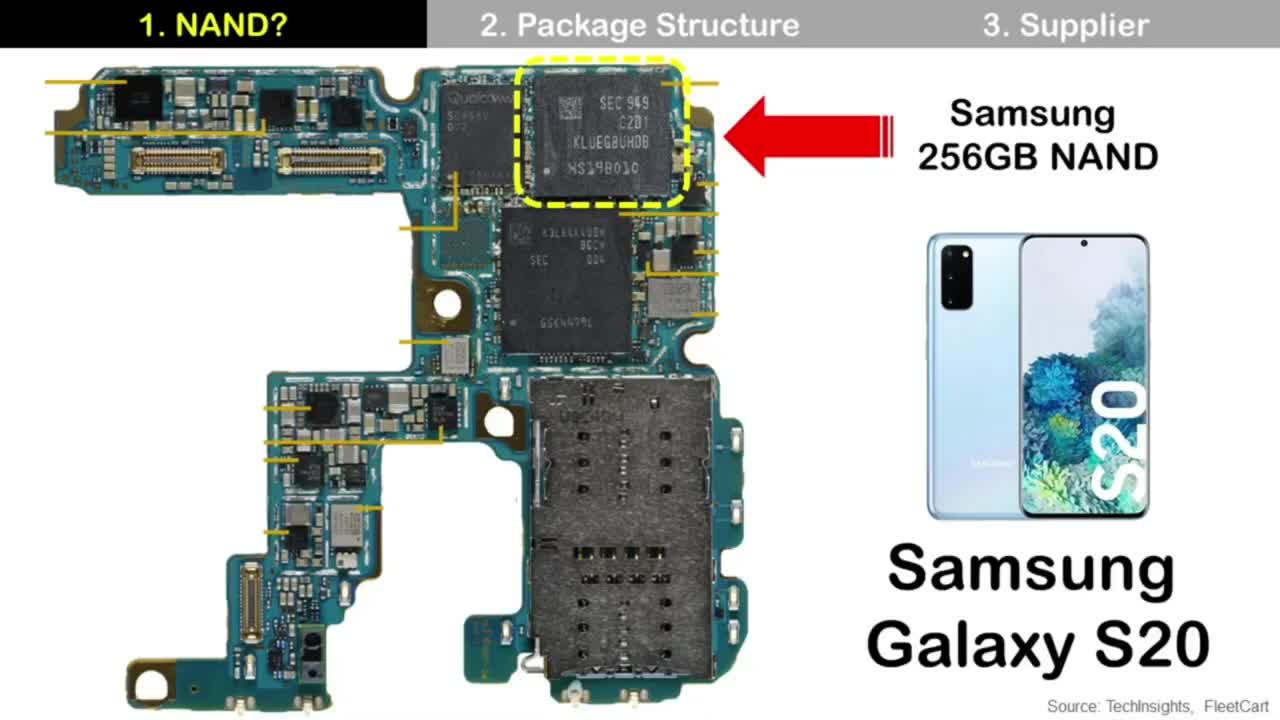

是因為SoC上集成了很多手機上最關鍵的部件,比如CPU、GPU、內存、也就說雖然它在主板上的存在是一個芯片,但是它里邊可是由很多部件封裝組成的。比如通常我們所說的高通801,Tegra 4,A6等等都只是系統部件

2021-07-28 07:57:15

SoC是什么意思?SoC是由哪些部件封裝組成的?

2021-10-19 06:07:13

SoC,系統級芯片,片上系統,是一個有專用目標的集成電路,其中包含完整系統并有嵌入軟件的全部內容。同時它又是一種技術,用以實現從確定系統功能開始,到軟/硬件劃分,并完成設計的整個過程。從狹義角度講

2016-05-24 19:18:54

家庭娛樂市場上的新興標準是什么?SoC設計中杜比數字加的實現優化方法是什么

2021-06-08 07:15:27

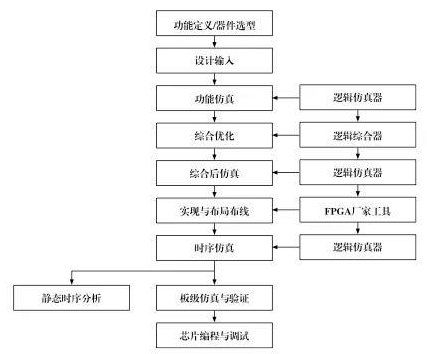

引言 隨著技術的進一步發展,SoC設計面臨著一些諸如如何進行軟硬件協同設計,如何縮短電子產品開發周期的難題。為了解決SoC設計中遇到的難題,設計方法必須進一步優化。因此,人們提出了基于FPGA

2019-07-12 07:25:22

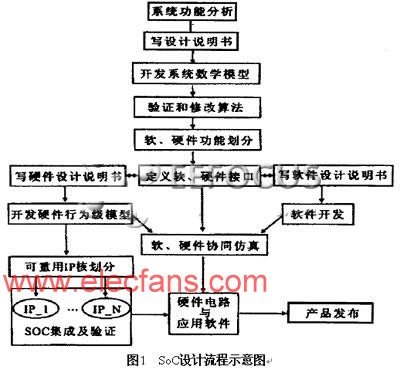

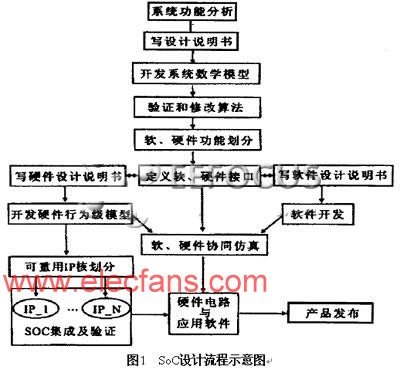

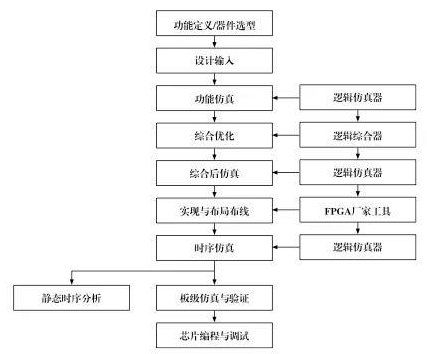

SoC設計流程一、SoC設計的特點二、軟硬件協同設計流程2.1 系統需求說明2.2 高級算法建模與仿真2.3 軟硬件劃分過程2.4 軟硬件同步設計三、基于標準單元的SoC芯片設計流程一、SoC

2021-11-11 07:48:45

soc芯片即System-on-a-Chip,簡單解釋就是系統級芯片。它是一個產品,是一個有專用目標的集成電路,其中包含完整系統并有嵌入軟件的全部內容。同時它又是一種技術,用以實現從確定系統功能

2022-01-25 07:42:31

soc計算方法,BMS中的SOC的計算其實可以分為三大部分:1、電芯層級的SOC計算(軟件中最真實的SOC計算,不涉及任何濾波處理);2、模組或者電池包層級的SOC計算(電芯到電池包級別的SOC映射

2021-07-27 06:13:05

由于技術的發展,高速電路電源設計要求三個協同:1.) SI、PI和EMI協同設計;2.) 芯片、封裝和系統協同設計;3.) 多物理場協同設計。

2019-11-11 17:31:44

現在有哪些芯片是將IC與外圍電路做在一起的(封裝成一個IC)?同事說到后面會把晶振等較大的器件也會封裝進去,那這種IC在后面是不是一種大趨勢?如果是這樣,怎樣能保證匹配和性能,因為封裝到里,可能無法靠調整外圍電路優化,個人還不是太懂,請各位發表下自己的觀點幫忙了解些~~

2015-07-20 11:49:43

`芯片開封也就是給芯片做外科手術,通過開封我們可以直觀的觀察芯片的內部結構,開封后可以結合OM分析判斷樣品現狀和可能產生的原因。開封的含義:Decap即開封,也稱開蓋,開帽,指給完整封裝的IC做局部

2020-04-14 15:04:22

16.5開始,Cadence能夠實現,根據提供的封裝與PCB板協同規劃的SoC IP從而高效實現系統級芯片。該版本的發布將提供一款封裝與PCB板協同規劃的DDR3 SoC IP方法的工具包,提供一個

2020-07-06 17:50:50

本帖最后由 hukaipanwenjing 于 2012-8-16 20:47 編輯

板上芯片封裝(COB),半導體芯片交接貼裝在印刷線路板上,芯片與基板的電氣連接用引線縫合方法實現,芯片

2012-08-16 20:44:11

摘要:簡要介紹了軟硬件協同仿真技術,指出了在大規模FPGA開發中軟硬件協同仿真的重要性和必要性,給出基于Altera FPGA的門級軟硬件協同仿真實例。 關鍵詞:系統級芯片設計;軟硬件協同仿真

2019-07-04 06:49:19

軟硬件協同設計(Hardware/Software Co-deaign)是在20世紀90年代興起的跨領域交叉學科。隨著超大規模集成電路制造工藝的進步,單個芯片所能提供的晶體管數量已經超過了大多數

2020-04-08 08:03:10

preference-inspired coevolutionary approach基于偏好啟發協同進化方法的混合可再生能源系統的多目標優化設計Keywords:Hybrid renewable energy systems混合可再生能源系統;Optimization優化;Preference-inspired coevo

2021-07-12 08:10:00

SoC設計的特點軟硬件協同設計流程基于標準單元的SoC芯片設計流程

2021-01-26 06:45:40

車路協同與智能協同群體智能和協同控制該怎樣實現

2020-12-30 07:51:36

采用遺傳算法對 EKF 中的系統噪聲矩陣和測量矩陣的協方差進行在線優化,以實現在模型誤差最小時對 SOC 進行在線估計

2020-03-12 12:27:05

SOC 的發展趨勢是:體系結構需要在新技術與產品、市場和應用需求之間取得平衡;設計方法趨向于走專用、定制和自動化的道路。一方面由于SOC 的專用化設計要求,另一方面由于IP 提供商的支持, SOC

2019-07-19 06:12:14

本文將討論通過優化封裝內的阻抗不連續性和改善其回波損耗性能,以滿足10Gbps SerDes鍵合線封裝規范。

2021-04-25 07:42:13

如何實現一體化芯片-封裝協同設計系統的設計?如何優化封裝和芯片接口設計?

2021-04-21 07:01:10

請問一下,如何利用AMSVF來進行混合信號SoC的全芯片驗證?

2021-05-06 07:56:08

板上芯片封裝(COB),半導體芯片交接貼裝在印刷線路板上,芯片與基板的電氣連接用引線縫合方法實現,芯片與基板的電氣連接用引線縫合方法實現,并用樹脂覆蓋以確保可靠性。雖然COB是最簡單的裸芯片貼裝

2018-09-17 17:12:09

固網短信電話專用SoC芯片介紹一種數模混合SoC設計協同仿真的驗證方法

2021-04-23 06:06:39

測量小型封裝的運算放大器或類似器件芯片溫度的最佳辦法是什么?測量結溫或芯片溫度的方法有幾種,某些方法較優。高速放大器部門應用工程師 John Ardizzoni 給大家介紹了 4 中方法——

2019-07-19 07:17:45

隨著行動裝置與新興穿戴式裝置等終端產品需求持續成長,我們需要將更多種元件安裝在電路板上,以提高產品功能。如果各個元件都獨立封裝,組合起來將耗費非常大的空間,因此目前有兩種方法,可滿足縮小體積的要求

2017-06-28 15:38:06

藍牙SOC芯片有哪個壇友對樂鑫的藍牙SOC芯片熟悉的?封裝最好是QFN24的不能比這個封裝大。需要藍牙5.0+MCU集成了,藍牙有內置巴倫電路,一根線拉出來就可以,不需要用被動器件調匹配電路!至少有兩個ADC口,一個IIC,一個UART,需要低功耗推薦下,只想用國產

2021-09-09 17:25:33

高速電路多物理場的芯片-封裝-系統(CPS)的協同SI-PI-EMI仿真

2019-11-13 08:56:06

` 由于技術的發展,高速電路設計要求三個協同:1.) SI、PI和EMI協同設計;2.) 芯片、封裝和系統協同設計;3.) 多物理場協同設計。https://bbs.elecfans.com/jishu_1882790_1_1.html`

2019-11-12 09:49:47

數模混合信號仿真已經成為SoC芯片驗證的重要環節。文章以一款固網短信電話專用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協同仿真環境進行仿真的驗證方法,并給出驗證結

2009-05-15 15:41:26 19

19 數模混合信號仿真已經成為SoC芯片驗證的重要環節。文章以一款固網短信電話專用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協同仿真環境進行仿真的驗證方法,并給出驗證結

2009-05-15 15:41:26 5

5 本文介紹了以超深亞微米技術為支撐的 SOC 的定義以及芯片設計方法,并闡述了軟硬件協同設計理論、IP 核生成及復用技術、超深亞微米IC 設計面對的難題以及SOC 測試與驗證技術。

2009-06-19 09:28:12 35

35 以 IP(Intellectual Property )核復用為基礎的SoC(System on a Chip,簡稱SoC)設計是以軟硬件協同設計為主要設計方法的芯片設計技術。本文從IP 核復用技術、軟硬件協同設計技術兩個方面

2009-08-10 08:32:17 18

18 基于SOC 的USB 主設備的軟硬件協同驗證李棟1,李正衛2(桂林電子科技大學通信與信息工程系,廣西 桂林 541004)摘 要:本文首先介紹了SOC 軟硬件協同驗證方法及其平臺Seamless

2009-12-14 11:31:21 15

15 研究表明協同推薦技術容易受到攻擊。由于現有的檢測模型對低填充規模攻擊的檢測效果不理想,本文結合檢測模型特點,改進Pearson相似度計算方法。其思想是,降低共同評分項目對用

2010-03-01 15:33:59 15

15 (COB)板上芯片封裝焊接方法及封裝流程

板上芯片(Chip On Board, COB)工藝過程首先是在基底表面用導熱環氧樹脂(一般用摻銀

2009-11-19 09:10:30 2305

2305 SOC設計方法

本文通過對集成電路IC技術發展現狀的討論和歷史回顧,特別是通過對電子整機設計技術發展趨勢的探討,引入系統芯片(System on Chip,簡稱S

2009-12-08 15:48:27 779

779

什么是soc芯片

SoC(System on Chip)。SoC是在一個芯片上由于廣泛使用預定制模塊IP而得以快速開發的集成電路。

2010-09-10 22:50:51 45585

45585

在高層次對系統進行功耗佑算和功耗優化是soc設計的關健技術本文首先給出soc設計的特點和流程,然后綜述目前高層次功耗估算和功耗優化的常用方法和技術,重點論述寄存器傳輸級和

2011-12-27 16:42:38 46

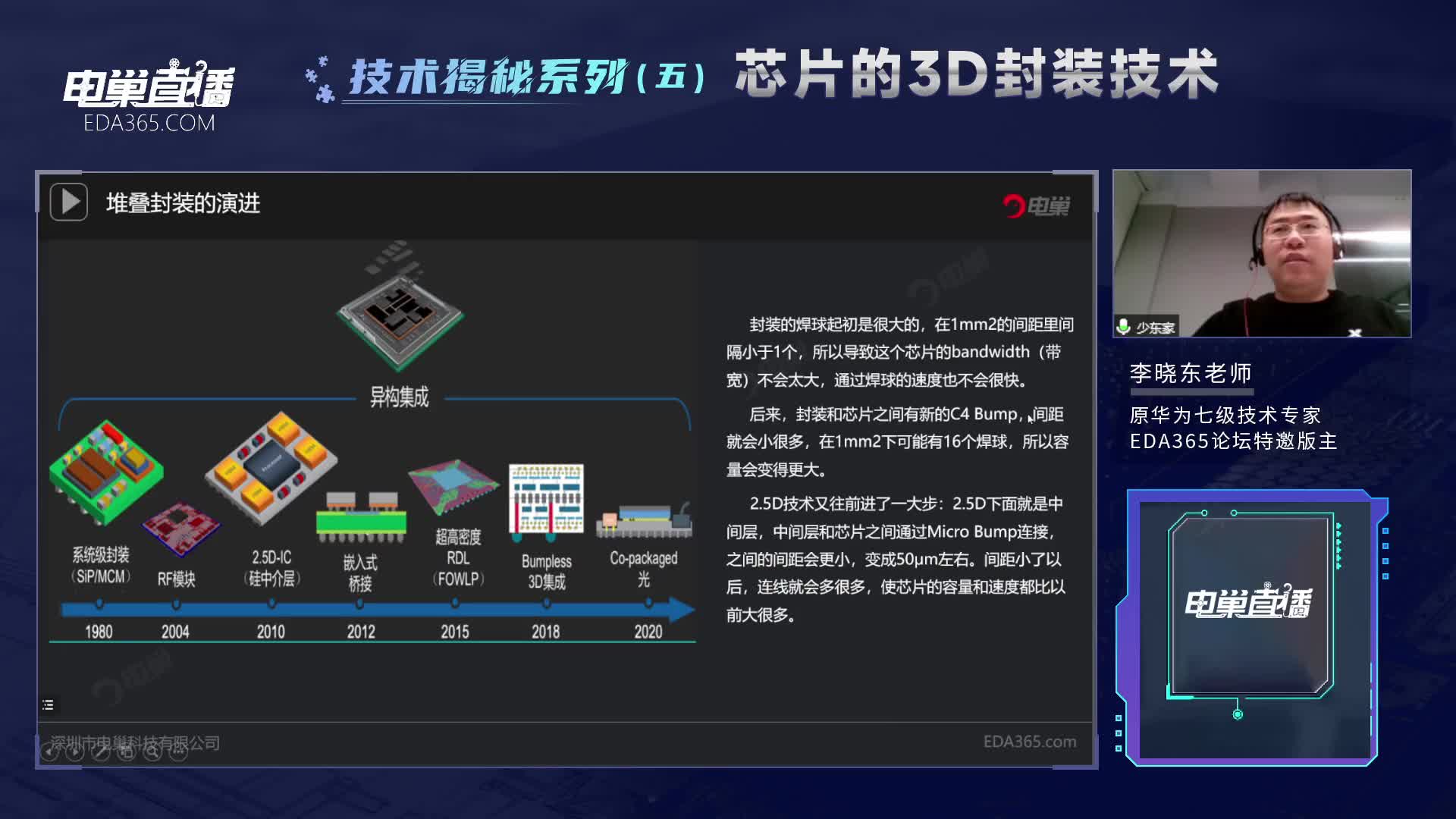

46 芯片堆疊封裝是提高存儲卡類產品存儲容量的主流技術之一,采用不同的芯片堆疊方案,可能會產生不同的堆疊效果。針對三種芯片堆疊的初始設計方案進行了分析,指出了堆疊方案失

2012-01-09 16:14:14 42

42 基于集成電路規模與設計工藝不斷發展的現狀,SI問題日益突出和嚴重。系統介紹了SOC設計SI的概念、分類及產生基理,根據電路工程設計經驗,重點闡述了在SOC設計SI的設計、優化、分

2012-04-12 14:31:05 35

35 SoC基于IP設計的特點使驗證項目中多語言VIP(Verification IP)協同驗證的需求不斷增加,給驗證工作帶來了很大的挑戰。為了解決多語言VIP在SoC驗證環境靈活重用的問題。提出了一種

2015-12-31 09:25:13 12

12 基于SOC調控的用于抑制光伏波動的電池儲能優化控制方法

2017-01-13 13:26:03 12

12 基于CMGA的SoC測試多目標優化研究_談恩民

2017-01-07 18:39:17 1

1 開關磁阻電機多目標協同優化設計_宋受俊

2017-01-08 11:28:38 0

0 關于協同空戰目標分配效能優化策略仿真_安超

2017-03-19 19:04:39 0

0 設計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協同驗證架構,討論和分析了利用FPGA軟硬件協同系統驗證SoC系統的過程和方法。利用此軟硬件協同驗證

2017-11-17 03:06:01 13138

13138

設計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協同驗證架構,討論和分析了利用FPGA軟硬件協同系統驗證SoC系統的過程和方法。利用此軟硬件協同驗證

2017-11-17 03:06:01 3769

3769

針對協同優化算法迭代次數多、易收斂于局部極值點問題,提出一種全局快速尋優的協同優化算法。在系統級一致性等式約束中采用改進后松弛因子,改進動態松弛因子使優化設計點快速收斂于極值點,靜態松弛因子使優化

2017-11-17 15:01:58 2

2 針對協同優化過程對初始點敏感以及容易陷入局部最優點的問題,提出了一種改進的協同優化算法。改進后的協同優化算法綜合考慮學科級優化設計點與系統級設計點的距離以及子學科級內部最優設計點,能較好地減弱優化

2017-11-24 14:46:02 1

1 空調作為具有熱存儲特性負荷的典型,具有被納入電力系統調度控制體系的潛能。設計了含可控空調負荷群的調度控制構架,提出了一種計及空調負荷群控制的源一荷協同優化調度模型方法。對基于多樣性保持的空調負荷

2018-01-03 10:29:45 12

12 在一個芯片上,包括核心處理器、存儲單元、硬件加速單元以及眾多的外部設備接口等,具有設計周期長、實現成本高等特點,因此其設計方法必然是自頂向下的從系統級到功能模塊的軟、硬件協同設計,達到軟、硬件的無縫結合。

2020-07-13 09:53:57 2618

2618

電子發燒友網為你提供4/5G協同優化方法的研究資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-18 08:49:37 2

2 智能駕駛越來越進入大眾生活的同時,汽車芯片的類型從之前的成熟封裝向先進封裝演進,同時對測試的要求也愈加復雜。在保證芯片功能安全性的條件下如何優化測試的方法是其中重要的挑戰。 月芯科技(ISE

2021-06-01 10:37:25 3916

3916 SoC設計流程一、SoC設計的特點二、軟硬件協同設計流程2.1 系統需求說明2.2 高級算法建模與仿真2.3 軟硬件劃分過程2.4 軟硬件同步設計三、基于標準單元的SoC芯片設計流程一、SoC

2021-11-06 16:21:01 37

37 本文分別從芯片設計技術和芯片封裝技術的維度,針對解決電子產品對芯片小型化、性能優、功能 強的要求,對 SOC 片上系統及 HIC、MCM、SIP 封裝技術的特點進行分析,并給出其相互關系,最終

2022-05-05 11:26:18 5

5 (Signal Integrity, SI)、電源完整性 (Power

Integrity, PI) 及可靠性優化。總結了目前 2.5D/3D 芯片仿真進展與挑戰,介紹了基于芯片模型的

Ansys 芯片-封裝-系統 (CPS) 多物理場協同仿真方法,闡述了如何模擬芯片在真實工況下達到優化

芯片信

2022-05-06 15:20:42 8

8 系統級封裝 (SiP) 是一種用于將多個集成電路 (IC) 和無源元件捆綁到一個封裝中的方法,它們在該封裝下協同工作。這與片上系統 (SoC) 形成對比,而這些芯片上的功能集成到同一芯片中。

2023-03-27 11:46:45 649

649 英特爾和Arm達成了一項合作協議,英特爾代工服務(Intel Foundry Services)和Arm將會進行設計技術協同優化,這意味著讓芯片設計者能夠基于英特爾18A制程打造低功耗的SoC

2023-04-19 14:31:23 914

914 芯片與封裝之間,封裝內各芯片之間,以區封裝與印制電路板(PCB)之間存在交互作用,采用芯片-封裝-PCB 協同設計可以優化芯片、封裝乃至整個系統的性能,減少設計迭代,縮短設計周期,降低設計成本。

2023-05-14 10:23:34 1488

1488

多芯片封裝技術是一種將多個芯片封裝在同一個封裝體內的集成封裝技術。在傳統的單芯片封裝中,一個封裝體內只封裝一個芯片,而多芯片封裝技術將多個芯片封裝在一個封裝體中,實現了不同功能芯片的集成和協同工作。

2023-05-24 16:22:31 672

672 CSP(Chip Scale Package)封裝芯片是一種高密度、小尺寸的封裝形式,它在集成電路行業中具有廣泛的應用。對于CSP封裝芯片的測試方法而言,主要涉及到以下幾個方面:

2023-06-03 10:58:16 1142

1142 AI芯片和SoC芯片都是常見的芯片類型,但它們之間有些區別。本文將介紹AI芯片和SoC芯片的區別。

2023-08-07 17:38:19 2103

2103 引言 在芯片設計中,IP設計(Intellectual Property design)和SOC設計(System on a Chip design)都是常用的設計方法。這兩種設計方法都旨在將多個

2023-08-24 10:10:44 1886

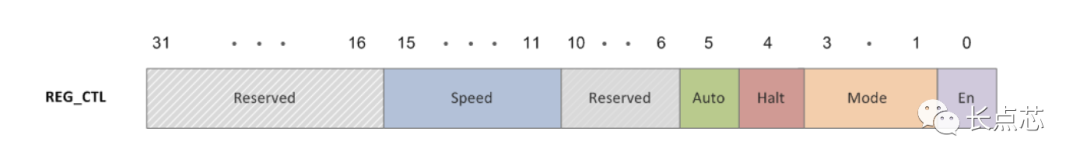

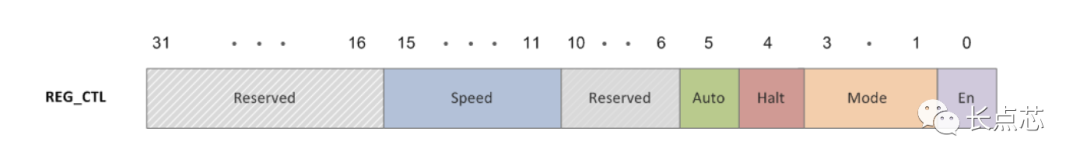

1886 就像芯片本身一樣,SoC上的CSR設計也沿用了層級設計的方法。從最底層往上,寄存器可以被分為以下幾個層級。

2023-10-20 10:39:39 394

394

SiP系統級封裝、SOC芯片和合封芯片技術都是重要的芯片封裝技術,在提高系統性能、穩定性和功耗效率方面有重要作用,但它們在集成方式、應用領域和技術特點等方面存在區別。

2023-11-24 09:06:18 288

288

電子發燒友App

電子發燒友App

評論