基于架構(gòu)和基于流的DFT方法 ASIC設(shè)計平均門數(shù)的增加迫使設(shè)計團隊花費20%到50%的ASIC開發(fā)....

無矢量測試:高速I/O的最佳選擇 大批量制造商必須解決如何經(jīng)濟高效地測試多個多線高速I的難題/O接口....

開放式架構(gòu)ATE解決測試困境 片上系統(tǒng)(SoC)測試提出了無與倫比的挑戰(zhàn),需要對IC制造商和測試人員....

在大多數(shù)鍵盤中,按一個鍵會關(guān)閉一個橋接xy矩陣中兩條線的觸點。如果使用微控制器檢測鍵閉合,則檢查(x....

邁向嵌入式系統(tǒng)的自診斷API 隨著嵌入式系統(tǒng)需求的增長和開發(fā)周期的縮小,開發(fā)人員越來越多地集成商業(yè)應(yīng)....

高密度數(shù)字CMOS工藝提供的低晶圓成本使其成為混合信號ASIC的首選,特別是對于片上系統(tǒng)設(shè)計。能夠在....

IC設(shè)計人員非常清楚“兩周到出帶模式”實際上可能持續(xù)數(shù)月,導(dǎo)致錯過里程碑和失去市場窗口。盡管使用了先....

在減少EMI問題時,大多數(shù)同軸電纜表現(xiàn)相同。它們都是普通電流的良好天線,可以輻射并通過FCC認證類型....

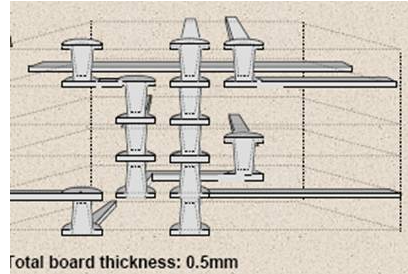

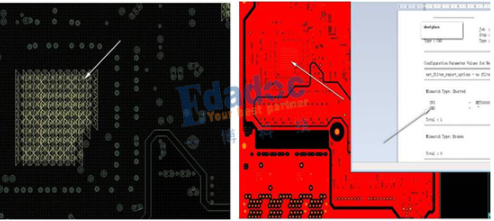

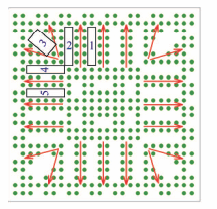

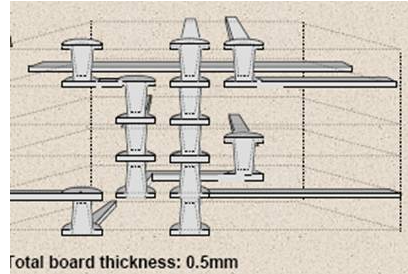

OMAP3530 CUS 封裝采用稱為 Via Channel? 陣列的新技術(shù)設(shè)計。該技術(shù)允許使用標....

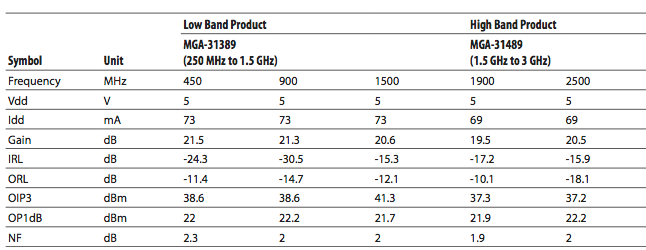

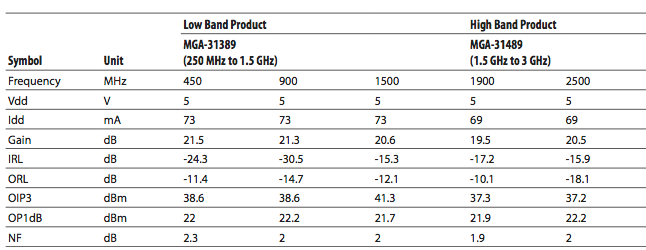

Avago Technologies 的 MGA-31389 和 MGA-31489 是 0.1 瓦....

作者:Maurizio Di Paolo Emilio 由于勞斯萊斯的要求,Trackwise 最初....

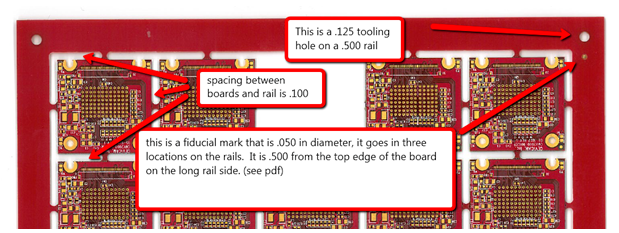

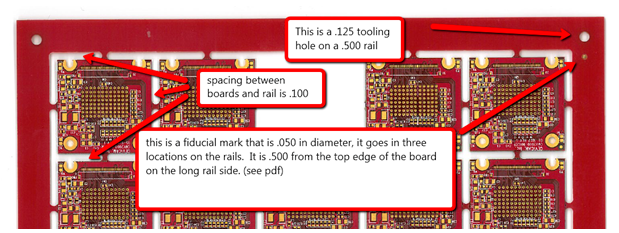

此過程稱為“逐出”單個板。它通常被稱為“逐步重復(fù)”。用于描述陣列的其他術(shù)語有:鑲板、分步、托盤化和潰....

交流電通過橋式整流器BR1整流。電感器 L1、L2 和電容器 C1、C2 形成一個 pi (π) 濾....

ASMT-Mxxx / ASMT-Axxx / ASMTJxxx是Avago的高功率LED發(fā)射器,可....

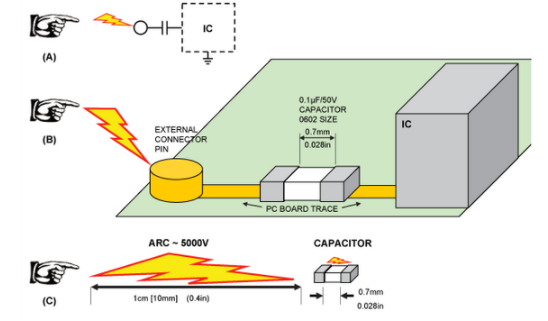

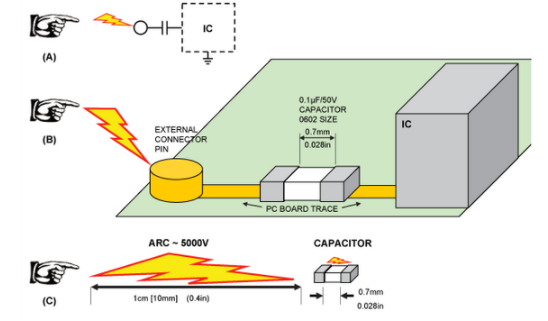

出于顯而易見的原因,EOS和ESD可能會在制造,封裝組裝和測試過程中損壞零件。但更重要的是,這些負力....

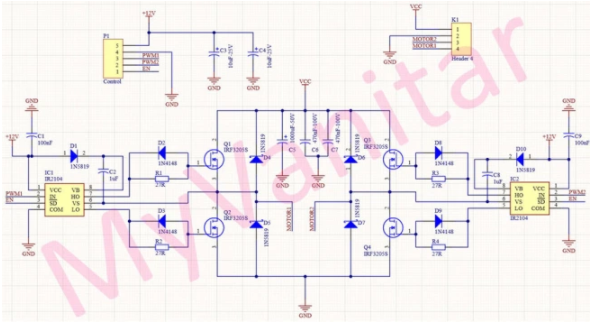

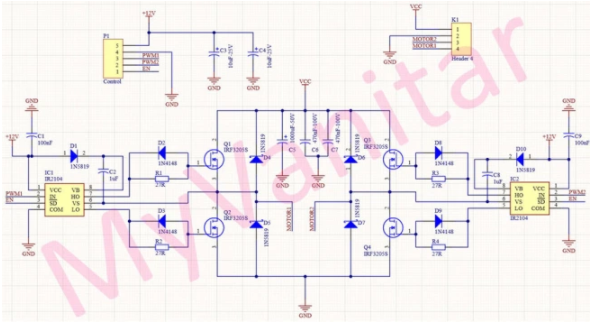

H橋(全橋)驅(qū)動器在驅(qū)動有刷直流電機等負載方面非常流行,并且已廣泛用于機器人技術(shù)和工業(yè)中。使用H橋驅(qū)....

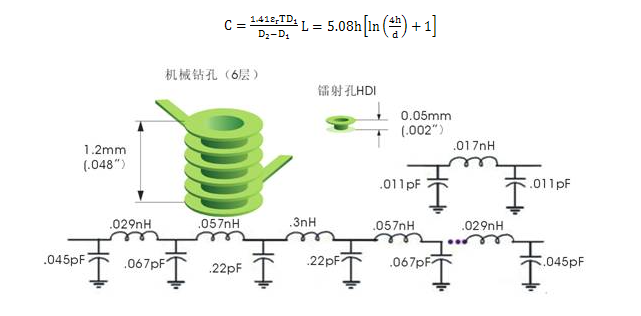

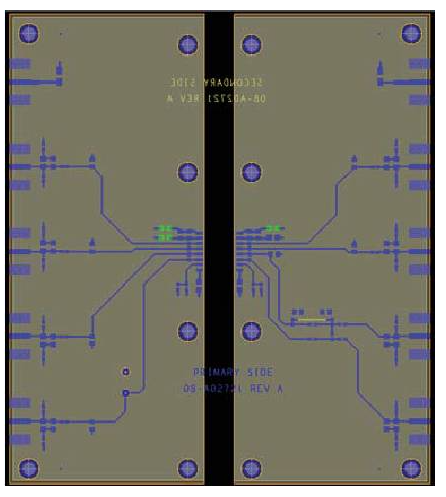

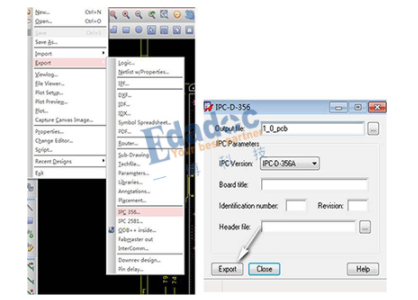

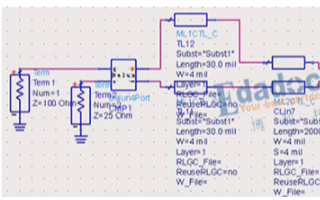

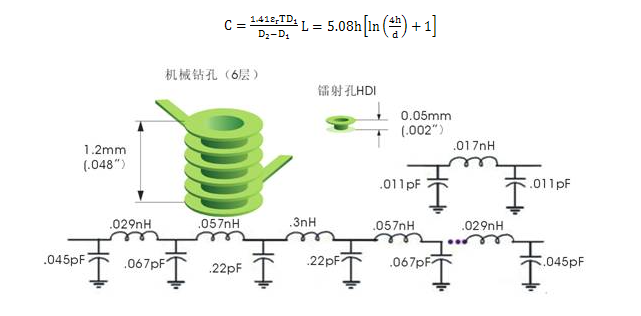

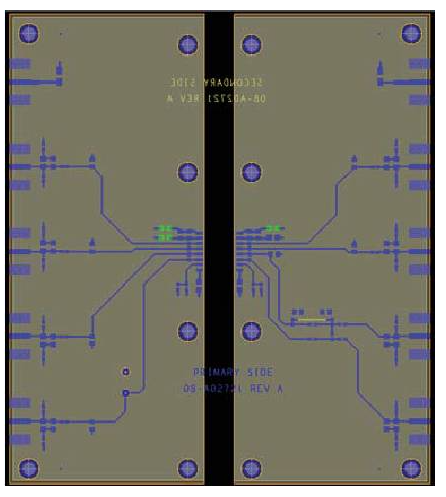

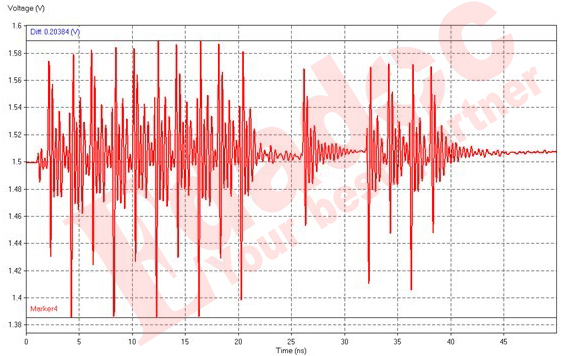

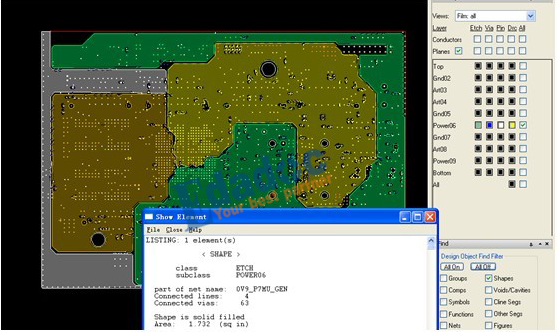

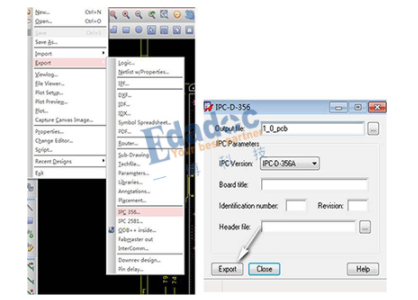

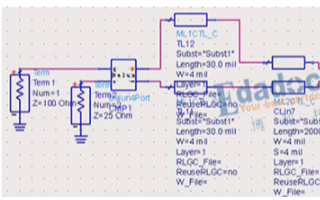

HDI設(shè)計在高速中的應(yīng)用以及仿真方法 高速串行總線技術(shù)的發(fā)展,信號傳輸速率繼續(xù)提升,過孔寄生參數(shù)帶來....

如果還是需要設(shè)置不同層的過孔,會增加管理難度。需要設(shè)計工具具備智能化打孔的能力,同時能隨意的進行組合....

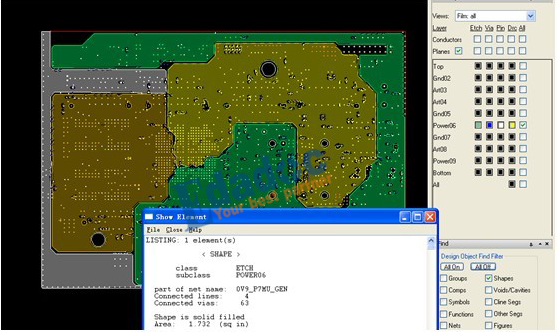

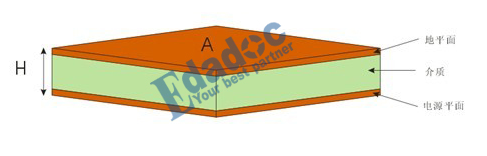

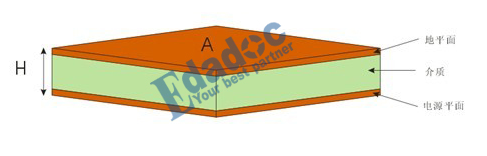

PCB設(shè)計盡量讓電源平面和地平面緊耦合,讓鄰近的兩個面之間形成耦合平面電容。

添加封裝寄生電感和Die電容的參數(shù),準確仿真整個PDN路徑的阻抗。這個方法困難的地方在于很多時候拿不....

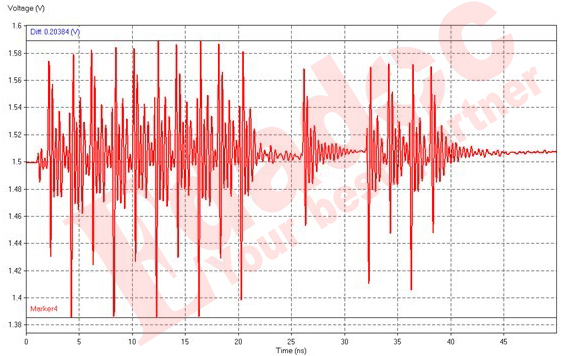

從仿真結(jié)果可以看到,隨著電源地之間的間距減小,加入埋容材料,平面諧振點向低頻偏移,同時低頻的阻抗也大....

一個良好的層疊,正常情況下已經(jīng)考慮了平板間電容,所謂埋容設(shè)計只是采用特殊的材料來加大這個平板間電容。

據(jù)說數(shù)學家很痛恨物理學家,因為數(shù)學家辛辛苦苦推導(dǎo)出來的結(jié)論居然和物理學家猜出來的結(jié)論是一樣的。當然這....

PCB電測是一種有效的印制板最終檢驗方法。 大家都知道我們成品PCB在交貨之前都要100%進行電測,....

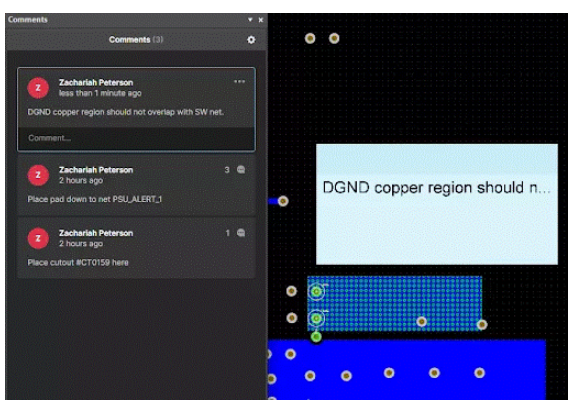

設(shè)計與制造是產(chǎn)品生命周期中最重要的兩個環(huán)節(jié),隨著電子業(yè)及PCB制造業(yè)的蓬勃發(fā)展,行業(yè)內(nèi)的競爭達到白熾....

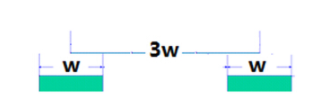

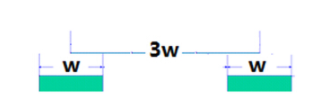

在PCB設(shè)計初期,確定差分信號線寬間距時,我們會面對這么個選擇:相同的阻抗管控,對應(yīng)著不同的線寬間距....

應(yīng)在制造后自動或手動檢查電路板。通過自動檢查可以識別的一些缺陷包括走線尺寸和間距違規(guī)、缺失或短路的焊....

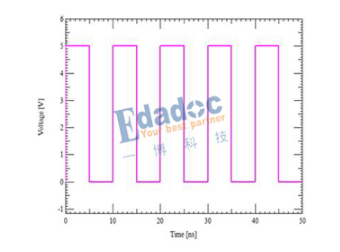

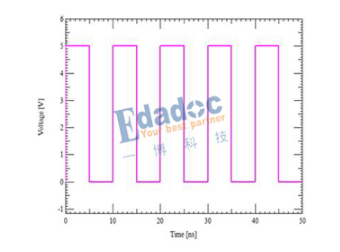

在數(shù)字電路中,芯片與芯片之間傳輸?shù)氖菙?shù)字信號,數(shù)字信號是0、1這樣的脈沖信號。完美的數(shù)字信號應(yīng)該是圖....

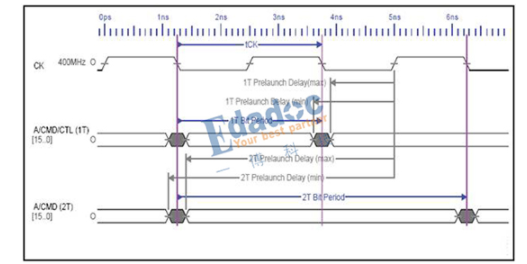

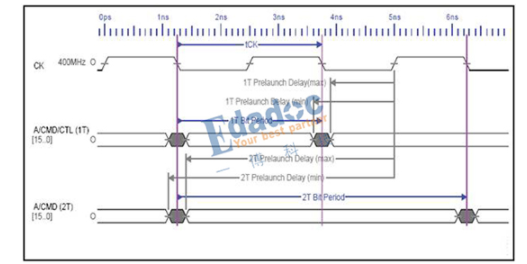

高速先生前幾期的自媒體文章里多次提到了時序,并且也寫了很多時序方面的文章,這些文章都從不同的角度對時....

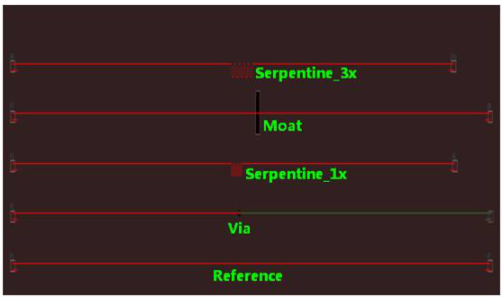

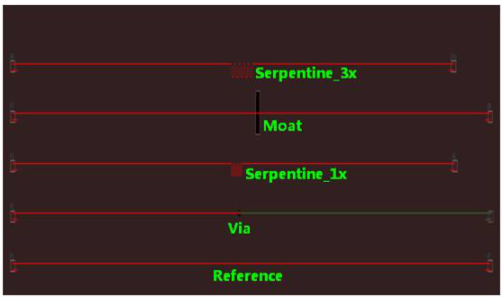

1倍線寬的蛇形繞線帶來的延時差異是-10ps,比參考線快了10ps,造成延時差異的主要原因是信號的自....