您的位置:電子發燒友網 > 電子技術應用 > 嵌入式技術 > 嵌入式設計應用 >

低功耗6管SRAM單元設計方案

2011年11月22日 14:50 來源:現代電子技術 作者:李少君,王子歐, 我要評論(0)

引言

在傳統6T-SRAM結構里,數據存儲節點通過存取管直接連接到位線上。這樣在讀過程中,由于存取管和下拉管之間的分壓作用會使存儲節點數據受到干擾,另外由于這種直接讀/寫機制會使存儲節點很容易受到外部噪聲的影響從而可能導致邏輯錯誤。

除了數據的穩定性問題之外,不斷增大的芯片漏電流也是另一個需要考慮的問題。在現代高性能微處理器,超過40%的功耗是由于泄漏電流引起的。隨著越來越多的晶體管集成到微處理器上,漏電功耗的問題將會更加突出。此外,漏電是待機模式下惟一的能耗來源,SRAM單元是漏電流的一個重要來源。

本文在分析傳統6T-SRAM基礎上,并基于以上考慮,提出了一種高可靠性低功耗的新6管SRAM單元。由于讀電流與噪聲容限的沖突,這個結構采用讀/寫分開機制,將存儲節點和讀輸出分開,從而不會使位線的波動干擾到存儲節點的值;另外,每次讀或寫過程中,只需要一個位線參與工作,因此相比較而言,降低了功耗,仿真結果顯示這種結構讀/寫速度也和普通6管SRAM相差無幾。

1 6T-SRAM存儲單元簡介

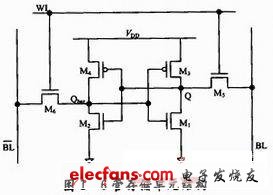

6管存儲單元結構如圖1所示。

1.1 6管單元結構及工作原理

6T-SRAM單元結構晶體管級電路如圖1所示,它由6個管子組成,整個單元具有對稱性。其中M1~M4構成雙穩態電路,用來鎖存1位數字信號。M5,M6是傳輸管,它們在對存儲器進行讀/寫操作時完成將存儲單元與外圍電路進行連接或斷開的作用。對單元的存取通過字線WL(Word Line)使能,字線WL為高電平時傳輸管導通,使存儲單元的內容傳遞到位線BL(Bit Line),單元信息的反信號傳遞到位線

,外圍電路通過BL和

讀取信息。寫操作時,SRAM單元陣列的外圍電路將電壓傳遞到BL和

上作為輸入,字線WL使能后,信息寫入存儲單元。

1.2 靜態噪聲容限SNM

靜態噪聲容限SNM是衡量存儲單元抗干擾能力的一個重要參數,其定義為存儲單元所能承受的最大直流噪聲的幅值,若超過這個值,存儲節點的狀態將發生錯誤翻轉。隨著數字電路不斷發展,電源電壓VDD逐漸變小,外部噪聲變得相對較大。如圖1所示的6T-SRAM,在讀操作中有一個從存儲節點到位線BL的路徑,當存取管開啟,BL和存儲節點直接相連。因此,外部的噪聲很容易破壞數據,噪聲容限受到前所未有的挑戰。

2 新型6T-SRAM存儲單元簡介

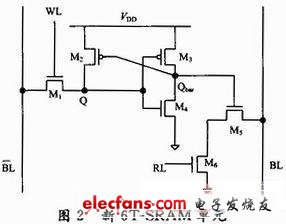

針對以上問題,提出一個新型6T-SRAM存儲單元結構,如圖2所示。NMOS管M5和M6負責讀操作,NMOS管M1,M4,PMOS管M2,M3完成寫操作,讀/寫操作的時候只有1個位線參與工作,因此整個單元功耗減小很多。

(1)空閑模式

在空閑模式下,即讀操作和寫操作都不工作的情況下,當O存在Q點時,M3打開,Qbar保持在VDD,同時M2,M4是關閉的,此時Q點的數據0可能受到漏電流IDS-M2漏電堆積,從而在Q點產生一定電壓,甚至可能導致Q點數據翻轉,產生錯誤邏輯。因此要利用M1管的漏電流,主要是M1的亞閾值電流,為了這個目的,需要在空閑模式下將位線

拉到地,同時將字線WL保持在亞閾值工作的條件下,這樣就可以無需刷新正確存儲數據0。當1存在Q點時,M4,M2打開,在Q和Qbar之間有正反饋,因此Q點被M2管拉到VDD,Qbar被M4管拉到地,但是此時M1管是處在亞閾值條件下,因此有一條路徑從VDD到

,這會導致Q點數據不穩定,甚至有可能翻轉,由于流經M2的電流遠遠大于流經M1的電流,數據相對還是比較穩定的。另一條位線BL拉到地,在空閑模式下讀路徑這端漏電流很小,可以忽略。

(2)寫循環

寫1操作開始,WL高電平打開M1管,讀控制管RL關閉,

充電使得

=1,BL=0,Q點開始充電到1(此時由于NMOS管傳遞的是弱1),從而打開M4管,使Qbar=0,同時正反饋打開M2管,將Q點保持在強1;相反,寫0操作的時候,位線

放電到

=0,打開字線WL,Q=0,同時打開M3管,Qbar=1。在結束寫操作后,單元進入空閑模式。

(3)讀循環

讀操作主要由M5,M6管負責,Qbar連接到M5管的柵極,BL充電到高電平。讀1的時候,Q=1,Qbar=0,M5關閉的,因而靈敏放大器從BL讀出的是1;當讀0操作的時候,WL字線關閉的,RL開啟,Q=0,Qbar=1,管子M5開啟,M5管和M6管共同下拉BL,讀出數據0。在結束讀操作后,單元進入空閑模式。

本文導航

- 第 1 頁:低功耗6管SRAM單元設計方案(1)

- 第 2 頁:噪聲容限