摘要:敘述了L82C37A可編程DMA控制器的主要功能、制造工藝和測試,并對其基本電路及設計方法進行了簡要介紹。

1 概述

L82C37A可編程DMA控制器是一個高性能的可編程直接存取控制器,可在沒有CPU干預的情況下進行內存與外設之間的數據直接傳輸。在微機系統中,通過使用DMA操作可大大提高系統的單個或多個I/O裝置的數據傳輸速率。

該電路采用2.0μm硅柵CMOS全離子注入工藝制造,集成度為13500管位,芯片面積為25.12mm2,采用DIP 40 PIN 陶瓷封裝。

該電路具有以下特點:

與NMOS 82C37A兼容;

具有四個可編程的獨立DMA通道,每個通道具有自動初始化能力;

能到存儲器到存儲器間的傳輸;

有四種基本工作方式和三種傳輸方式;

任意擴展DMA通道數;

每個通道有64k地址和64k字節記數空間;

數據最高傳輸速率可達4MB/秒;

低功耗靜態CMOS設計,IDDSB=10μA;

與TTL兼容;

單5V電源工作;

工作頻率8MHz;

工作溫度范圍-55℃~+125℃。

2 邏輯結構和功能

2.1 L82C37A主要功能

L82C37A主要功能有以下七點:

(1)該電路有四個獨立DMA通道;

(2)每個通道的DMA請求都可分別允許和禁止;

(3)每個通道的DMA請求優先權具有固定方式和循環方式;

(4)每個通道一次傳送的最大長度64k字節的數據,可在存儲器與外設間進行傳送,也可在存儲器的兩個區間進行傳送;

(5)有四種DMA傳輸方式:①單字節傳輸方式;②數據塊傳輸方式;③請求傳輸方式;④ 級連方式。在每種方式下,都能在接收外設的請求信號DREQ后,向外設發送響應信號DACK后就可以占用總線,進行DMA傳送。每傳送一個字節,修改一次地址指針,當規定傳送的字節數送完時,發出終端計數脈沖TC,結束傳送或重新初始化;

(6)允許外設用EOP信號結束DMA傳送或重新初始化;

(7)L82C37A可以級聯,任意擴展通道數。

2.2 L82C37A邏輯結構

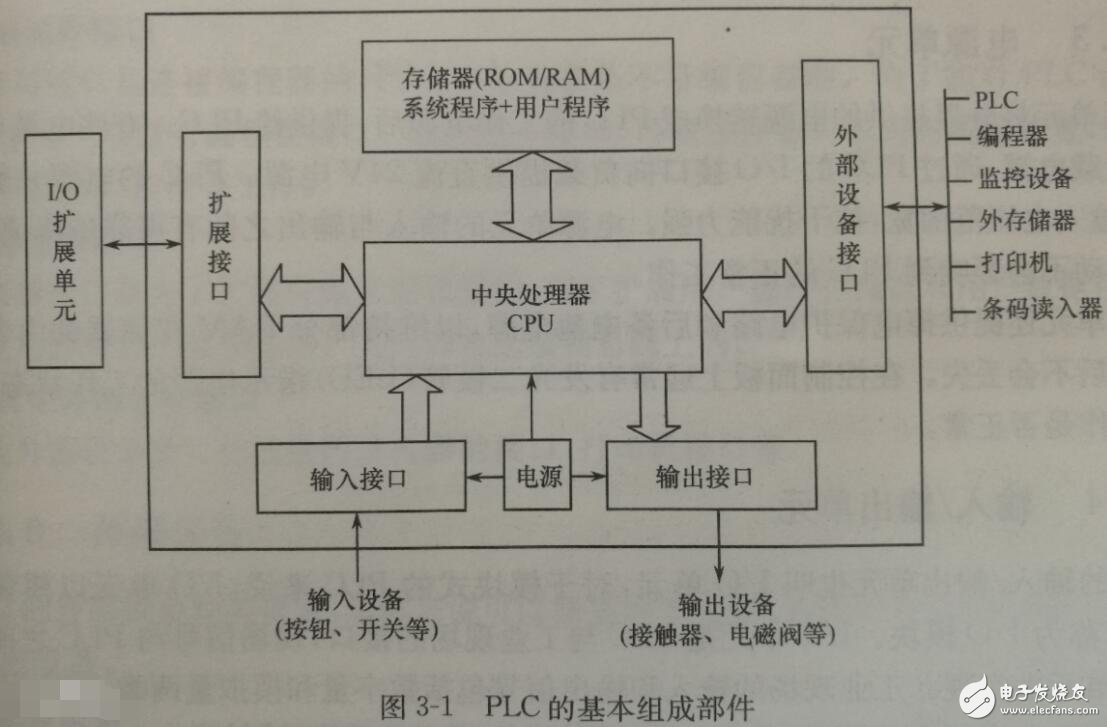

L82C37A的邏輯功能較為復雜,其邏輯框圖如圖1所示。圖中的通道部分只畫出了一個通道的情況,即每個通道都有一個基地址寄存器(16位)、基字節數計數器(16位)、現行地址寄存器(16位)和現行字節數計數器(16位),每一個通道都有一個6位的模式寄存器,用以控制不同的工作模式。

圖1 L82C37A邏輯框圖

L82C37A的結構中包含了三個基本的控制邏輯塊。

時序控制邏輯塊:根據編程規定的DMA的工作模式,產生包括DMA請求、DMA傳送及DMA結束所需要的內部時序和外部信號。

程序命令控制塊:對在DMA請求服務之前,CPU編程對給定的命令字和模式控制字進行譯碼,以確定DMA服務的類型。

優先權編碼邏輯:對同時有請求的通道進行優先權編碼,確定哪個通道的優先權最高,優先權可以是固定的,也可以是循環的。

另外,L82C37A的數據引線都有三態緩沖器,因而可以占用也可以釋放總線。

2.3 L82C37A的工作周期

L82C37A有兩種主要的工作周期,即空閑周期和有效周期,每一個周期由若干個時鐘周期組成。

(1)空閑周期

L82C37A在完成了一個DMA服務之后,若沒有新的DMA請求,或在主清零或硬件復位后,將進入空閑周期執行SI狀態。在每個時鐘周期它都要對通道的請求線DREQ進行采樣,在沒收到DREQ前,它將始終處于SI態。

在此狀態中,CPU可以查詢其狀態或對其進行編程。若 ,則CPU可以對其進行讀寫操作,可以對其基地址、基字節數、當前地址、當前字節數等寄存器進行讀/寫。此時,需通過數據總線和地址總線以及

,則CPU可以對其進行讀寫操作,可以對其基地址、基字節數、當前地址、當前字節數等寄存器進行讀/寫。此時,需通過數據總線和地址總線以及 和來選擇寄存器并改寫數據。由于這四組寄存器均為16位,而數據總線是8位的,則由內部高/低位寄存器控制,將數據分成高8位和低8位,分兩次寫。另外還有些軟件命令,不通過數據總線,僅由地址A0-A3和

和來選擇寄存器并改寫數據。由于這四組寄存器均為16位,而數據總線是8位的,則由內部高/低位寄存器控制,將數據分成高8位和低8位,分兩次寫。另外還有些軟件命令,不通過數據總線,僅由地址A0-A3和 等信號的譯碼來設置。

等信號的譯碼來設置。

(2)有效周期

當外設或CPU發出DMA請求時,將跳出SI狀態進入DMA服務的第一狀態S0。此時,雖收到SREQ并發出HRQ,但在收到CPU返回HLDA信號后,L82C37A才進入由S1-S3組成的工作狀態,若外設的工作速度較慢,DMA傳送不能在S4狀態之前完成時,則可用READY線在S2或S3與S4之間插入SW狀態,直到本次傳輸結束。SW狀態是等待周期,主要是為適應慢速外設,以延長傳輸時間。

在存儲器至存儲器傳輸時,要作存儲器讀和寫操作,所以每一次傳輸需要8個時鐘周期,其中4個周期S11-S14完成存儲器讀,另外4個周期S21-S24完成存儲器寫操作。

2.4 L82C37A的工作模式

L82C37A在DMA傳送時有四種工作模式:

(1)單字節傳送方式

一次只傳送一個字節,每次傳輸后,字節計數器減1,并修改地址,HQR變為無效,并釋放系統總線,當字節減到0時,產生一個IC脈沖結束DMA傳送或重新初始化。

在這種模式下,DACK有效前,DREQ必須始終保持有效。但是,如果DREQ的有效時間比單字節傳輸所需時間還長,那么,在傳輸完一個字節后,L82C37A首先釋放總線,然后再產生一個DREQ,完成下一個字節的傳送。

(2)塊傳送方式

一經DREQ啟動,并在其發出響應信號DACK后,便進行連續的數據傳輸,直到字節計數器減到0,產生終端計數器脈沖TC,或由外部輸入一個有效的 信號,傳輸才結束。

在這種方式下,DREQ信號僅需要維持到DACK有效,在數據傳輸完了之后,由程序決定是結束操作還是重新初始化。如果不需要自動初始化,則數據傳送完,便自動停止操作,釋放總線。

(3)請求傳送方式

在這種方式下,L82C37A可連續地傳送數據,直到產生終端計數脈沖TC,以表示要傳送的數據傳完。此時,DREQ無效,使傳輸結束。L82C37A釋放總線,傳輸結束后,字節計數器和當前地址寄存器中,仍保持該通道傳輸結束前的最后一個值。只要外設準備好要傳遞的數據,并發出DREQ信號,則可繼續傳輸。

(4)級聯方式

這是為擴展通道數而設的一種工作方式。第二級的DRQ和HLDA信號與第一級的DREQ和DACK分別相連,第二級各片子的優先權和與其相連第一級的通道相對應。此時,第一級只起優先權網絡的作用。除了由某一個二級的請求信號通過它向CPU輸出HRQ信號外,并不輸出任何其它信號。實際的傳輸操作則由二級片子完成。若需進一步擴展通道,則同樣還可以級聯三級等等。

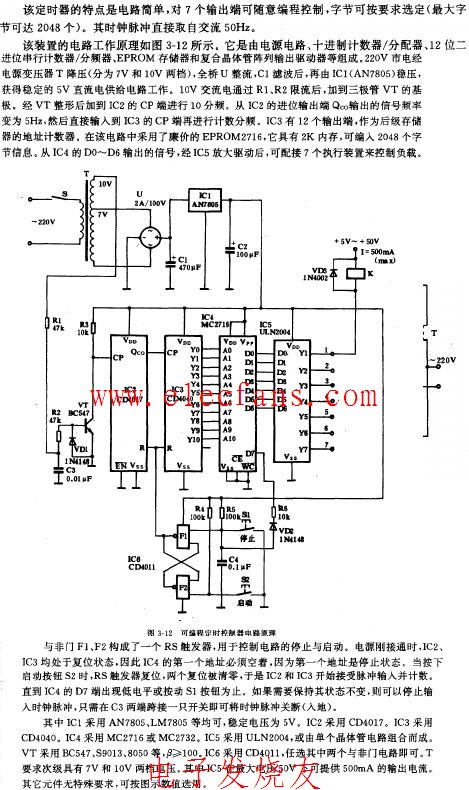

2.5 L82C37A內部基本電路

(1)基地址、字節數、當前地址、字節數寄存器組電路

在器件中,基地址、當前地址、基字節數和當前字節數寄存器的電路形式基本相同,如圖2所示。

圖2 基地址(字節數)當前地址(字節數)寄存器

在圖中,左半部分為基地址或基字節數寄存器,右半部分為當前地址或當前字節數寄存器,寄存器單元中數據的出入由IDS控制。在CPU對其進行寫時,內總線上的數據,在IW控制下進入到寄存器,并寫到寄存器中。

在圖中看出,基地址和當前地址(基字節和當前字節數)寄存器,具有相同的初始值,因為它們是在同一時刻由同一控制信號寫入的。

CPU對寄存器組的讀操作卻只限于當前地址和當前字節數寄存器。因為基地址和基字節數寄存器只寫不讀。圖中IDS是通道寄存器選擇線,由A0-A3譯碼形成,Q是復位線,由系統復位線RESET或主清零等軟件命令控制。D和V是自動初始化控制線,當其有效時,其寄存器的內容被重新寫入當前寄存器中。每完成一次傳輸地址和字節數都將被修改,由R線送到寄存器中。

(2)模式寄存器

L82C37A 內部每個通道都有一個6位的模式寄存器,其結構如圖3所示。

圖3 模式寄存器

該寄存器是確定工作模式的,這是一個D觸發器,其輸入/輸出均與數據總線相連。在輸入控制信號ME=1時,總線數據寫入寄存器。ME=0時數據鎖存。MS有效時,模式寄存器的數據送往相應控制的控制端。如果CPU查詢模式寄存器則可使EMR有效,將其內容讀到數據線上。

模式寄存器由A0-A3和D0、D1來選擇,當A0-A3為1101,D0 D1為00時,則選中通道0的模式寄存器。此時CPU可以對其進行讀/寫操作。

在DMA控制器中,還有命令寄存器、狀態寄存器、請求寄存器、屏蔽寄存器、暫存寄存器等。在此不贅述。

2.6 L82C37A版圖設計

L82C37A的版圖是采用2.0μm硅柵CMOS單層金屬布線規則進行設計的。

主要的設計規則如下(單位:μm):

(1)N/P管溝道長度 2.0/2.5

(2)多晶硅最小條寬/間距 2.0/3.0

(3)多晶硅包孔 1.25

(4)多晶硅在場區出頭 2.0

(5)有源區最小寬/間距 3.0/2.5

(6)P阱包N管有源 3.0

(7)P阱距P管有源 7.0

(8)P+包有源 2.0

(9)孔最小尺寸 2.0×2.0

(10)鋁最小寬/間距 4.0/4.0

(11)鋁線包孔 1.0

(12)鈍化窗口尺寸 100×100

L82C37A控制電路部分的版圖均由標準單元電路版圖構成,在版圖完成之后,對版圖進行了DRC、ERC、LVS檢查,以確保其正確性。

2.7 L82C37A工藝研制

L82C37A采用2.0μm硅柵CMOS全離子注入工藝制造。襯底材料為N型硅,晶向為〈100〉,電阻率為6~9Ω.cm。

(1)工藝流程

選片→一次氧化→光刻P阱→P阱注入→P阱推進→預氧化→LPCVDSi3N4→光刻有源→P管場注入→光刻→N管場注入→場氧化→預柵氧化→溝道→調整注入→柵氧化→多晶硅淀積→多晶硅摻磷→光刻多晶→光刻 P+區→P+注入→光刻N+區→N+注入→淀積二氧化硅→源漏區推進→光刻電極孔→濺射Al-Si膜→光刻→合金→鈍化→光刻→蒸金→中測→壓焊→封裝

(2)工藝參數和器件物理參數

一氧:100 nm

P阱結深:≥3.5μm

預氧:50nm

Si3N4:150nm

場氧:900nm

一柵:50nm

柵氧:450nm

多晶:400~450nm

摻磷:R□單晶≤8Ω/□ R□poly≤2.5Ω/□

LPSiO2:600 nm

Si-Al:1.4 μm

鈍化(LPSiO2/PESi3N4): 300/500 nm

VTN:0.6~0.9V

ΒVDSN≥16V

VNTL Al/Si≥16V

VTP:0.8~1.2V

ΒVDSP≥18V

2.8 測試

2.8.1 測試程序

L82C37A的工作方式比較復雜,時序要求比較繁瑣,測試脈沖的調制也比較嚴格。對于不同的輸入端,根據時序的要求,進行7種不同時序調制,并同時進行兩次分級調制。對于I/O讀和I/O寫分別采用150ns和100ns的歸零取反調制,地址線A0-A3采用雙向的歸零調制。對于數據總線D7-D0也采用歸零調制。其它輸入采用不歸零調制。

2.8.2 測試碼點

L82C37A由于功能比較復雜,時序要求又比較嚴格,測試碼點的產生比較長。根據L82C37A的功能特性要求,分成4種不同類型的測試碼點圖形,有利于進行測試分析。

2.8.3 交、直流參數測試

L82C37A電路的交、直流參數測試是按照參數手冊的交、直流參數要求進行測試的。

3 結束語

L82C37A電路在DIC-8032大型測試系統上完全按照手冊要求,進行全功能、全參數測試。測試結果表明,各項參數指標均達到國外同類產品的性能參數規范,可替換使用。L82C37A能在-55℃~+125℃全溫區、8MHz頻率條件下可靠地工作,達到了用戶要求,可批量生產.

電子發燒友App

電子發燒友App

評論