ISE12.2設計套件強化了其部分可重配置技術設計流程,并通過智能時鐘門控技術降低24% 的 BRAM 功耗。賽靈思部分可重配置技術,是目前唯一經行業驗證的可重配置FPGA

2010-07-31 12:39:03 439

439 通過FPGA的多重配置可以有效地精簡控制結構的設計,同時可以用邏輯資源較少的FPGA器件實現需要很大資源才能實現的程序。以Virtex5系列開發板和配置存儲器SPI FLASH為基礎,從硬件電路

2014-01-24 14:17:22 13670

13670

當FPGA 完成上電自動加載初始化的比特流后,可以通過觸發FPGA 內部的多重啟動事件使得FPGA 從外部配置存儲器(SPI FLASH)指定的地址自動下載一個新的比特流來重新配置。

2015-02-02 11:09:51 1096

1096

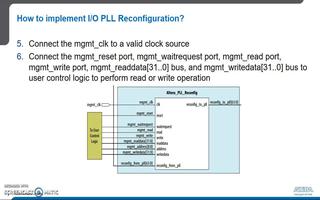

上文XILINX FPGA IP之Clocking Wizard詳解說到時鐘IP的支持動態重配的,本節介紹通過DRP進行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

AS安全模式建立完畢后,UE和gNB之間會觸發RRC重配置流程。

重配置信令流程如圖所示:

那么觸發重配置流程的目的以及重配置消息中有哪些關鍵字段呢?

1 RRC重配置流程的目的

2023-05-10 15:44:58

在編程過程中得到需要的指示信號。 以上步驟我們已經詳細講解了怎么使用PS對FPGA現場重配置。配置文件到底是什么呢?SOF?POF?都不是,配置文件為最原始的RBF二進制文件。采用Quartues文件轉換把

2012-04-26 14:27:03

SDR是使用一個簡單的終端設備通過軟件重配置來支持不同種類的無線系統和服務(包括2G、3G移動通信系統和WLAN)的新技術。它具有較強的開放性和靈活性,硬件采用標準化、模塊化結構,可以隨著器件和技術的發展而更新和擴展;軟件模塊可以進行加載和更改,根據需要不斷升級。

2019-08-21 06:54:09

,以便為Microblaze實現不同的periferal。我已經讀過Spartan3 FPGA支持部分重配置,但我不知道它是否支持動態重配置,而Microblaze仍在使用中。有幫助嗎?提前致謝缺口

2019-05-14 06:28:56

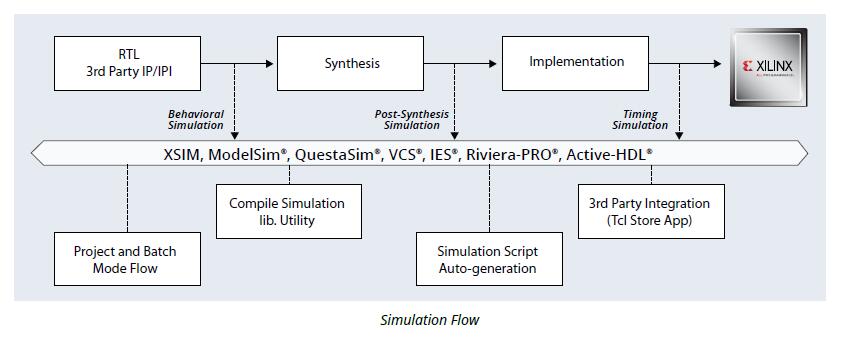

在FPGA的應用中,很多時候就是CPU+FPGA+一些常見外設(FLASH、SRAM等),FPGA的功能差別其實不大,那么它的測試文件差別應該也不是這么大,為了簡化仿真,是不是可以寫些文件,通過修改

2013-08-29 20:40:25

在FPGA的應用中,很多時候就是CPU+FPGA+一些常見外設(FLASH、SRAM等),FPGA的功能差別其實不大,那么它的測試文件差別應該也不是這么大,為了簡化仿真,是不是可以寫些文件,通過修改

2013-08-29 20:42:31

在FPGA的應用中,很多時候就是CPU+FPGA+一些常見外設(FLASH、SRAM等),FPGA的功能差別其實不大,那么它的測試文件差別應該也不是這么大,為了簡化仿真,是不是可以寫些文件,通過修改

2013-08-29 20:46:18

Altera可重配置PLL使用手冊在實際應用中,FPGA的工作時鐘頻率可能在幾個時間段內變動,對于與之相關的鎖相環(PLL),若PLL的輸入時鐘在初始設定的時鐘頻率的基礎上變化不太大時,PLL一般

2009-12-22 11:27:13

Cyclone? IV GX 收發器支持對收發器的不同部分進行動態重配置,而無需對器件的任何部分斷電。本章節提供并講解了用于動態重配置各種模式的實例。您可以使用 ALTGX_RECONFIG

2017-11-14 10:53:11

得Morph-IC-II成為必須透過 USB下載新軟件以重新動態配置硬件功能的理想應用選擇。此外,除了提高應用的靈活性,透過USB重新配置硬件也可降低BOM成本, FPGA只需為最復雜的分離功能而不是所有功能來設定大小。

2019-07-03 08:29:05

PSoC 1具有獨特的“動態重配置”能力。這意味著可以使用單個資源來執行多個功能。例如,我們可以考慮一種冷飲自動售貨機。大部分時間,它必須作為一個自動售貨機扔出罐頭和收集錢。但是在晚上,一段時間

2019-05-24 14:51:27

用于Virtex 6設計的可重配置LUT(CFGLUT)可能被封裝到FPGA的輸出邏輯OLOGICE1而不是SLICEM上的LUT。我的設計涉及使用存在于與CFGLUT相同的片中的FF(用于流水線

2018-10-22 11:04:46

`Xilinx FPGA入門連載17:PWM蜂鳴器驅動之復位與FPGA重配置功能特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1 復位

2015-10-26 12:05:15

Xilinx PlanAhead工具資料說可以用來部分動態重配置,我現在想對芯片的每一幀中每一位進行逐位翻轉的動態重配置,使用PlanAhead能夠實現么?應該怎么理解Planahead的部分重配置,如何應用?希望知道的朋友告訴下,對這個有點迷茫。

2015-06-01 10:11:33

FPGA平臺將 ARM? 雙核 Cortex?-A9 MPCore 硬處理器和具備動態部分可重配置功能的 28 nm 賽靈思 7 系列可編程邏輯器件完美結合在一起,不但可充分滿足所需要求,而且還配備有 CAN 和以太網等車載網絡常用的片上通信控制器。

2019-07-05 08:34:21

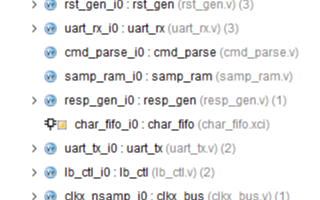

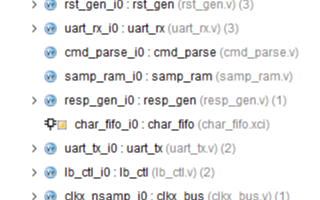

一種可擴展的嵌入式網絡平臺的解決方案

2021-05-26 07:10:20

參考了官網和各路大神寫的一些關于PLL動態重配置的資料,雖然有收獲但是還是感覺大神們寫的太高端,不夠詳細,對于我這種學渣看起來還是迷迷糊糊。所以整理了一下自己的經驗,把整個過程記錄了下來。沒有很多語言全部是截圖大家湊合看吧。附有源代碼和Word文檔。

2017-10-12 12:32:44

本文提出了一種基于嵌入式系統和Internet的FPGA動態配置方案。

2021-05-27 06:38:55

本文介紹的基于FPGA的可重配置系統可以在設計后期甚至量產階段通過重新編程以適應標準和協議的改變。

2021-05-13 06:35:49

軟件無線電(SDR)是帶有可重配置硬件平臺的無線設備。這些可重配置硬件平臺能夠被用于多種通信標準,并將在最終實現認知無線電(CR)的過程中發揮關鍵作用。與此同時,由于SDR具有更低的成本、更大

2019-07-29 07:21:01

結構,上層為配置存儲器,下層是硬件邏輯層。通過上層配置信息控制硬件層門電路的通斷,改變芯片內基本邏輯塊的布線,從而形成特定的功能。這種架構為動態重構技術實現提供了可能。一個FPGA大型數字系統總是由很多

2015-02-05 15:31:50

是否有任何教程顯示如何使用PowerPC或microblaze作為重配置控制器?我目前使用Impact工具使用部分比特流(ISE和Planahead 12.1)重新配置FPGA,但我想要一個重配置

2019-01-22 11:05:28

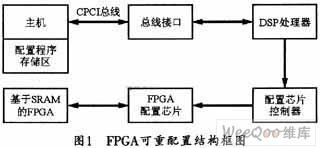

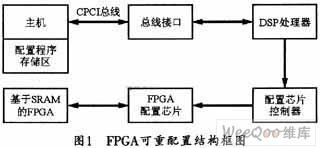

或系統重構。結合對FPGA重配置方案的軟硬件設計,本文通過PC機并通過總線(如PCI總線)將配置數據流下載到硬件功能模塊的有關配置芯片,從而完成配置FPGA的全過程。有誰知道,具體該怎么做嗎?

2019-08-07 06:17:30

我試圖找出部分重配置的配置架構。從我之前使用Virtex-5 FPGA的工作開始,幀將跨越時鐘區域的垂直切片。但是,我找不到任何類似的Virtex-7文檔。我找到的只是configuraiton指南

2020-05-29 08:54:01

隨著大規模集成電路的快速發展,系統設計已從傳統的追求大規模、高密度逐漸轉向提高資源利用率,使有限的資源可以實現更大規模的邏輯設計。利用現場可編程邏輯器件FPGA的多次可編程配置特點,通過重新下載存儲

2019-08-06 07:05:37

存儲配置數據。配置數據決定了PLD內部互連和功能,改變配置數據,也就改變了器件的邏輯功能。SRAM編程時間短,為系統動態改變PLD的邏輯功能創造了條件。但由于SRAM的數據易失的,配置數據必須保存在PLD器件以外的非易失存儲器內,才能實現在線可重配置(ICR)。

2019-08-22 06:31:02

uCLinux作為操作系統平臺,設計出可動態配置的片上系統(rSoC)。uCLinux從遠程服務器上下載FPGA程序代碼,然后利用shell腳本工具將代碼寫進FPGA芯片,實現系統功能的可動態擴展。 (2

2019-04-04 17:12:33

,上至高性能CPU,下至簡單的74電路,都可以用它來實現。FPGA在嵌入式系統中的應用越來越廣泛。John Williams和NeilBergmann用uCLinux作為操作系統平臺,設計出可動態配置

2018-10-26 09:22:17

,上至高性能CPU,下至簡單的74電路,都可以用它來實現。FPGA在嵌入式系統中的應用越來越廣泛。John Williams和NeilBergmann用uCLinux作為操作系統平臺,設計出可動態配置的片

2018-10-28 09:53:34

對于城域網絡和長途網絡來說,如果光傳送層具有遠程重新配置的能力,則可以極大地降低運營成本。運營商也已經意識到這種潛力,并在最近業務網絡的招標中加入了對于可重配置光分插復用器(ROADM)以及多維光

2019-08-08 06:31:07

本文提出的通過微處理器加FPGA結合串行菊花鏈實現可重構的方式,實現了動態可重構FPGA結構設計的一種應用。

2021-05-10 06:22:19

日前,Altium 宣布推出另一款面向桌面 NanoBoard 可重構硬件開發平臺的全新子板,進一步幫助電子設計人員輕松利用可編程硬件的優勢。這款最新插入式子板采用 780 BGA 封裝,內置

2019-07-25 06:07:43

親愛的先生: 我是xilinx產品的新手。 我有興趣購買xilinx開發板。 Isaw avideoabout是“可擴展的處理平臺”。 我想購買具有這種“可擴展處理平臺”的工具包。能否列出具有此功能

2019-01-22 10:12:53

賽靈思Zynq-7000可擴展處理平臺(EPP)將雙ARM Cortex-A9 MPCore處理器系統與可編程邏輯和硬IP外設緊密集成在一起,提供了靈活性、可配置性和性能的完美組合。圍繞其剛剛推出

2019-05-16 10:44:42

近日IEEE AutoTestCon上, Aeroflex 宣布推出適用于無線應用場合、頻率可高達6GHz的新型模塊化RF測試平臺。這個可擴展平臺具有靈活性高的特點,易于在從研發到生產等無線開發

2019-06-28 06:39:18

動態資源控制就是通過傳輸信道重配置、無線承載(RB重配置)等手段動態控制無線資源的過程,從而達到資源合理分配和有效利用。本章通過舉例方式說明動態資源控制流程

2009-05-30 17:18:10 5

5 本文提出了一種全新的總線可重配置的多處理器架構。該架構結合了多核與可重配置處理器的優勢,具有并行性高、計算能力強、結構復雜度低并且應用領域廣泛靈活的特點。對

2009-06-13 14:11:04 11

11 該文基于現有端到端可重配置系統架構,提出了一種改進的動態門限聯合負載控制方法,以適應不同負載條件下對負載均衡的要求,達到資源的有效利用。同時,結合終端的可重配

2009-11-19 16:41:25 13

13 為了應用FPGA中內嵌的數字時鐘管理(DCM)模塊建立可靠的系統時鐘。首先對DCM的工作原理進行分析,然后根據DCM的工作原理給出了一種DCM動態重配置的設計方法。DCM動態重配置設計是利

2010-07-28 17:03:52 28

28 介紹了基于ARM和FPGA的端到端重配置終端的硬件平臺設計方法。給出了系統設計的硬件結構和重要接口, 提出了由ARM微處理器通過JTAG在系統配置FPGA的方法, 以滿足重配置系統中軟件

2010-09-14 16:40:09 21

21 本文檔主要是以Altera公司的Stratix II系列的FPGA器件為例,介紹了其內嵌的增強型可重配置PLL在不同的輸入時鐘頻率之間的動態適應,其目的是通過提供PLL的重配置功能,使得不需要對

2010-11-02 15:17:24 27

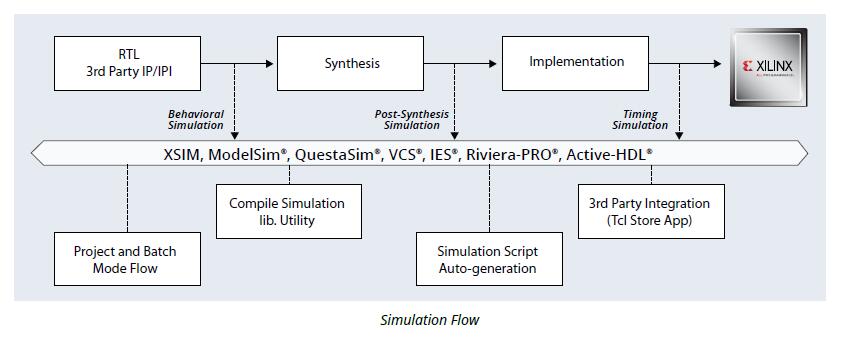

27 實現了一種用于上位機和FPGA處理板之間通信的可重配置接口,詳細介紹了該接口的包格式設計和FPGA邏輯設計。仿真結果表明,該可重配置接口能根據信令,實現準實時在線參數配置

2010-11-22 15:15:28 12

12 在當今復雜數字電路設計中,大多采用以“嵌入式微控制器+FPGA”為核心的體系結構。提出了一種對現有傳統FPGA配置方案硬件電路稍做調整并增加部分軟件功能,即可實現FPGA動態

2010-12-08 15:52:01 19

19 FPGA的全局動態可重配置技術主要是指對運行中的FPGA器件的全部邏輯資源實現在系統的功能變換,從而實現硬件的時分復用。提出了一種基于System ACE的全局動態可重配置設計方法,

2011-01-04 17:06:01 54

54 摘要: 一種基于嵌入式系統和Inlternet的FPGA動態配置方案。詳細介紹了該方案的設計思想,并給出了設計實例。與傳統的FPGA配置方案相比,該方案具有靈活

2009-06-20 10:37:59 355

355

基于SRAM的可重配置PLD(可編程邏輯器件)的出現,為系統設計者動態改變運行電路中PLD的邏輯功能創造了條件。PLD使用SRAM單元來保存字的配置數據決

2009-06-20 11:05:37 845

845

采用VC++程序的FPGA重配置設計方案利用現場可編程邏輯器件FPGA的多次可編程配置特點,通過重新下載存儲于存儲器的不同系統數據

2010-04-14 15:14:57 580

580

為了滿足對分數階 信號變換 進行實時計算的要求,提出一種基于Altera St ratix II FPGA 平臺的可重配置分數階信號變換處理器的硬件實現方案. 根據角度分解的算法,設計了一種通用的硬件框

2011-07-04 15:13:03 33

33 利用賽靈思 FPGA 的動態重配置功能,同構多線程執行模型可同時兼得軟件靈活性和硬件性能。

2011-09-01 09:27:26 584

584

基于 FPGA 的 RCS 有幾項值得注意的設計事項與優勢。其核心部分是我們連接在一起以構成單個計算系統的數個FPGA。在我們的可重配置系統中,我們使用了正交通信系統,將 FPGA 布置在矩

2011-09-20 08:57:32 27

27 WP374 Xilinx FPGA的部分重配置

2012-03-07 14:34:39 34

34 在過去,靜態決策最壞情況分配曾為嚴格的實時約束提供了解決方案,而現在靈活性也成為一項要求。法國某研究項目建議使用的解決方案是一種分布在 FPGA 資源上,對軟硬件線程進行

2012-05-09 10:40:11 1675

1675

本文介紹了XiLinx FPGA中DCM的結構和相關特性,提出了一種基于XiLinx FPGA的DCM動態重配置的原理方法,并給出了一個具體的實現系統。系統僅通過外部和......

2012-05-25 13:42:50 39

39 打造完全可重配置運動控制系統 ,NI LabVIEW。

2016-03-21 16:19:31 0

0 們快速開發和部署加速平臺。專門針對云級應用而設計的基于FPGA的賽靈思可重配置加速堆棧,包括庫、框架集成、開發板并支持OpenStack。通過賽靈思FPGA,該可重配置加速堆棧方案提供了業界最高的計算效率:比x86服務器CPU高出40倍;比競爭型FPGA方案高出6倍。

2016-11-16 16:42:23 648

648 一種基于憶阻器的可重配置邏輯電路_張波

2017-01-08 10:18:57 4

4 這里提到的局部重配置技術(Partial Reconfiguration) 是現場可編程門陣列(呵呵,就是FPGA了) 器件中的一部分。指的是在FPGA其他部分還在正常運行的情況下對其局部進行的重新配置。

2017-02-11 16:32:11 2622

2622 Suite HLx 2017.1版中廣泛納入部分重配置技術,為有線和無線網絡、測試測量、航空航天與軍用、汽車以及數據中心等豐富應用,提供動態的現場升級優勢和更高的系統集成度。

2017-04-27 18:38:08 2782

2782

工作效率。通過FPGA 的多重配置可以有效地精簡控制結構的設計,同時可以用邏輯資源較少的FPGA 器件實現需要很大資源才能實現的程序。以Virtex5系列開發板和配置存儲器SPIFLASH為基礎,從硬件電路和軟件設計兩個方面對多重配置進行分析,給出了多

2017-10-12 17:57:08 15

15 FPGA 動態局部重配置技術是近幾年才發展起來的一項新技術。這項技術可以使 FPGA運行時,通過 JTAG或 SelectMAP(ICAP)動態重配置部分區域,而不影響非重配置區域的正常工作

2017-10-18 16:38:59 4

4 視頻、影像和電信市場的標準推動了異構可重配置 DSP硬件平臺的使用。就本文而言,這些平臺包括 DSP 處理器和 FPGA,它們提供的現成硬件解決方案可以解決視頻、影像和電信設計中的重大難題,但仍不

2017-10-20 09:07:37 0

0 視頻、影像和電信市場的標準推動了異構可重配置DSP硬件平臺的使用。在本文中這些平臺包括DSP處理器和FPGA,它們提供的現成硬件解決方案可以解決視頻、影像和電信設計中的重大難題,同時又不失差異化

2017-11-06 13:59:42 2

2 的FPGA 快速動態重構方案, 實現了同一硬件平臺下多個FPGA 設計版本的在線動態配置和功能重構, 該技術已在工程中成功應用。

2017-11-22 07:55:01 937

937

:不存在時延,這種方法基本不占用資源(在FPGA上占用的查找表不足300個),而且設計人員可以優化部分重配置的時序。

2017-11-22 17:08:56 1492

1492 的應用。在主流的FPGA中,絕大多數都采用了SRAM來存放配置數據,稱為SRAM FPGA。這種FPGA的突出優點是可以進行多次配置。通過給FPGA加載不同的配置數據,即可令其實現不同的邏輯功能.FPGA這種可重配置的能力將給數字系統的設計帶來很大的方便。

2018-07-18 12:50:00 2407

2407

針對虛擬網絡映射中能耗過高、接收率偏低和負載不夠均衡等問題,提出一種基于虛擬資源整合的綜合性重配置算法-HEAR算法。該重配置算法分為兩個階段:節點重配置階段優先將映射虛擬節點最少的物理節點上的虛擬

2017-12-20 11:31:58 0

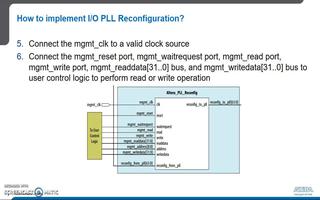

0 如何在 Arria 10 中實現 I/O 鎖相環 (PLL) 重配置

2018-06-20 00:57:00 3438

3438

賽靈思公司(Xilinx)宣布,在2016全球超算大會(SC 16)上宣布推出一套全新的技術——賽靈思可重配置加速堆棧方案,旨在幫助全球最大的云端服務供應商們快速開發和部署加速平臺。專門針對

2018-07-31 09:08:00 731

731 Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允許用戶在不掉電重啟的情況下,根據不同時刻的需求,可以從FLASH 中貯存的多個比特文件選擇加載其中的一個,實現系統功能的變換。

2018-12-04 08:37:00 4654

4654

結合對FPGA重配置方案的軟硬件設計,本文通過PC機并通過總線(如PCI總線)將配置數據流下載到硬件功能模塊的有關配置芯片,從而完成配置FPGA的全過程。該方法的軟件部分基于Visual C++的開發環境,并用C++語言開發動態連接庫,以用于軟件設計應用程序部分的調用。

2018-12-30 09:26:00 2425

2425

本視頻介紹了UltraScale +芯片的部分重配置功能,展示了Vivado Design Suite中部分重配置的新功能,并介紹了對部分重配置的更廣泛的訪問權限

2018-11-20 06:25:00 3831

3831 了解Xilinx如何在UltraScale器件中推進其突破性的部分重配置技術。

該視頻全面介紹了20nm UltraScale FPGA的新功能,擴展功能和系統要求。

2018-11-26 06:45:00 1988

1988 關鍵詞:PLD , SRAM , 可重配置電路 由于SRAM的可重配置PLD(可編程邏輯器件)的出現,為系統設計者動態改變運行電路中PLD的邏輯功能創造了條件。PLD使用SRAM單元來保存字的配置

2019-02-23 14:30:01 675

675

軟件無線電硬件平臺的一個重要和必須的特點就是硬件的可配置性。那么具體到FPGA來說能實現什么樣的配置呢?

2019-06-22 09:55:41 931

931

TD-LTE SRS帶寬重配置導致掉話率高案例說明。

2021-03-25 09:51:33 20

20 Partial Reconfiguration(部分重配置)在現在的FPGA應用中越來越常見,我們這次的教程以Project模式為例來說明部分重配置的操作過程。

2021-07-05 15:28:24 3140

3140

電子發燒友網站提供《ELF2 FPGA PLL動態配置.pdf》資料免費下載

2022-09-26 15:13:06 0

0 一般情況下,要重新配置一個FPGA需要使其處于復位狀態,并通過外部控制器重新加載一個新設計到器件中。而局部重配置技術允許在FPGA內部或外部的控制器在加載一個局部設計到一個可重配置模塊中時

2023-03-17 14:03:39 1508

1508 除通過外部多功能IO來選擇之外,易靈思通過內部重配置實現遠程更新操作也非常簡單。

2023-05-30 09:24:32 712

712

電子發燒友App

電子發燒友App

評論