ISE12.2設(shè)計(jì)套件強(qiáng)化了其部分可重配置技術(shù)設(shè)計(jì)流程,并通過(guò)智能時(shí)鐘門控技術(shù)降低24% 的 BRAM 功耗。賽靈思部分可重配置技術(shù),是目前唯一經(jīng)行業(yè)驗(yàn)證的可重配置FPGA

2010-07-31 12:39:03 439

439 通過(guò)FPGA的多重配置可以有效地精簡(jiǎn)控制結(jié)構(gòu)的設(shè)計(jì),同時(shí)可以用邏輯資源較少的FPGA器件實(shí)現(xiàn)需要很大資源才能實(shí)現(xiàn)的程序。以Virtex5系列開(kāi)發(fā)板和配置存儲(chǔ)器SPI FLASH為基礎(chǔ),從硬件電路

2014-01-24 14:17:22 13670

13670

當(dāng)FPGA 完成上電自動(dòng)加載初始化的比特流后,可以通過(guò)觸發(fā)FPGA 內(nèi)部的多重啟動(dòng)事件使得FPGA 從外部配置存儲(chǔ)器(SPI FLASH)指定的地址自動(dòng)下載一個(gè)新的比特流來(lái)重新配置。

2015-02-02 11:09:51 1096

1096

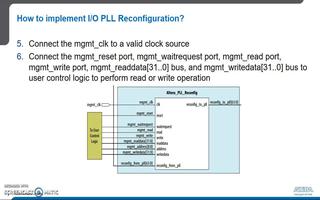

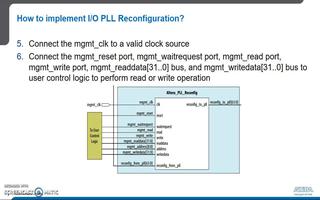

上文XILINX FPGA IP之Clocking Wizard詳解說(shuō)到時(shí)鐘IP的支持動(dòng)態(tài)重配的,本節(jié)介紹通過(guò)DRP進(jìn)行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

AS安全模式建立完畢后,UE和gNB之間會(huì)觸發(fā)RRC重配置流程。

重配置信令流程如圖所示:

那么觸發(fā)重配置流程的目的以及重配置消息中有哪些關(guān)鍵字段呢?

1 RRC重配置流程的目的

2023-05-10 15:44:58

在編程過(guò)程中得到需要的指示信號(hào)。 以上步驟我們已經(jīng)詳細(xì)講解了怎么使用PS對(duì)FPGA現(xiàn)場(chǎng)重配置。配置文件到底是什么呢?SOF?POF?都不是,配置文件為最原始的RBF二進(jìn)制文件。采用Quartues文件轉(zhuǎn)換把

2012-04-26 14:27:03

SDR是使用一個(gè)簡(jiǎn)單的終端設(shè)備通過(guò)軟件重配置來(lái)支持不同種類的無(wú)線系統(tǒng)和服務(wù)(包括2G、3G移動(dòng)通信系統(tǒng)和WLAN)的新技術(shù)。它具有較強(qiáng)的開(kāi)放性和靈活性,硬件采用標(biāo)準(zhǔn)化、模塊化結(jié)構(gòu),可以隨著器件和技術(shù)的發(fā)展而更新和擴(kuò)展;軟件模塊可以進(jìn)行加載和更改,根據(jù)需要不斷升級(jí)。

2019-08-21 06:54:09

,以便為Microblaze實(shí)現(xiàn)不同的periferal。我已經(jīng)讀過(guò)Spartan3 FPGA支持部分重配置,但我不知道它是否支持動(dòng)態(tài)重配置,而Microblaze仍在使用中。有幫助嗎?提前致謝缺口

2019-05-14 06:28:56

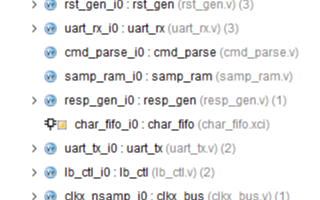

在FPGA的應(yīng)用中,很多時(shí)候就是CPU+FPGA+一些常見(jiàn)外設(shè)(FLASH、SRAM等),FPGA的功能差別其實(shí)不大,那么它的測(cè)試文件差別應(yīng)該也不是這么大,為了簡(jiǎn)化仿真,是不是可以寫(xiě)些文件,通過(guò)修改

2013-08-29 20:40:25

在FPGA的應(yīng)用中,很多時(shí)候就是CPU+FPGA+一些常見(jiàn)外設(shè)(FLASH、SRAM等),FPGA的功能差別其實(shí)不大,那么它的測(cè)試文件差別應(yīng)該也不是這么大,為了簡(jiǎn)化仿真,是不是可以寫(xiě)些文件,通過(guò)修改

2013-08-29 20:42:31

在FPGA的應(yīng)用中,很多時(shí)候就是CPU+FPGA+一些常見(jiàn)外設(shè)(FLASH、SRAM等),FPGA的功能差別其實(shí)不大,那么它的測(cè)試文件差別應(yīng)該也不是這么大,為了簡(jiǎn)化仿真,是不是可以寫(xiě)些文件,通過(guò)修改

2013-08-29 20:46:18

Altera可重配置PLL使用手冊(cè)在實(shí)際應(yīng)用中,FPGA的工作時(shí)鐘頻率可能在幾個(gè)時(shí)間段內(nèi)變動(dòng),對(duì)于與之相關(guān)的鎖相環(huán)(PLL),若PLL的輸入時(shí)鐘在初始設(shè)定的時(shí)鐘頻率的基礎(chǔ)上變化不太大時(shí),PLL一般

2009-12-22 11:27:13

Cyclone? IV GX 收發(fā)器支持對(duì)收發(fā)器的不同部分進(jìn)行動(dòng)態(tài)重配置,而無(wú)需對(duì)器件的任何部分?jǐn)嚯姟1菊鹿?jié)提供并講解了用于動(dòng)態(tài)重配置各種模式的實(shí)例。您可以使用 ALTGX_RECONFIG

2017-11-14 10:53:11

得Morph-IC-II成為必須透過(guò) USB下載新軟件以重新動(dòng)態(tài)配置硬件功能的理想應(yīng)用選擇。此外,除了提高應(yīng)用的靈活性,透過(guò)USB重新配置硬件也可降低BOM成本, FPGA只需為最復(fù)雜的分離功能而不是所有功能來(lái)設(shè)定大小。

2019-07-03 08:29:05

PSoC 1具有獨(dú)特的“動(dòng)態(tài)重配置”能力。這意味著可以使用單個(gè)資源來(lái)執(zhí)行多個(gè)功能。例如,我們可以考慮一種冷飲自動(dòng)售貨機(jī)。大部分時(shí)間,它必須作為一個(gè)自動(dòng)售貨機(jī)扔出罐頭和收集錢。但是在晚上,一段時(shí)間

2019-05-24 14:51:27

用于Virtex 6設(shè)計(jì)的可重配置LUT(CFGLUT)可能被封裝到FPGA的輸出邏輯OLOGICE1而不是SLICEM上的LUT。我的設(shè)計(jì)涉及使用存在于與CFGLUT相同的片中的FF(用于流水線

2018-10-22 11:04:46

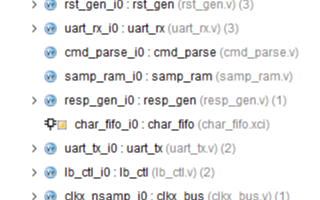

`Xilinx FPGA入門連載17:PWM蜂鳴器驅(qū)動(dòng)之復(fù)位與FPGA重配置功能特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1 復(fù)位

2015-10-26 12:05:15

Xilinx PlanAhead工具資料說(shuō)可以用來(lái)部分動(dòng)態(tài)重配置,我現(xiàn)在想對(duì)芯片的每一幀中每一位進(jìn)行逐位翻轉(zhuǎn)的動(dòng)態(tài)重配置,使用PlanAhead能夠?qū)崿F(xiàn)么?應(yīng)該怎么理解Planahead的部分重配置,如何應(yīng)用?希望知道的朋友告訴下,對(duì)這個(gè)有點(diǎn)迷茫。

2015-06-01 10:11:33

FPGA平臺(tái)將 ARM? 雙核 Cortex?-A9 MPCore 硬處理器和具備動(dòng)態(tài)部分可重配置功能的 28 nm 賽靈思 7 系列可編程邏輯器件完美結(jié)合在一起,不但可充分滿足所需要求,而且還配備有 CAN 和以太網(wǎng)等車載網(wǎng)絡(luò)常用的片上通信控制器。

2019-07-05 08:34:21

一種可擴(kuò)展的嵌入式網(wǎng)絡(luò)平臺(tái)的解決方案

2021-05-26 07:10:20

參考了官網(wǎng)和各路大神寫(xiě)的一些關(guān)于PLL動(dòng)態(tài)重配置的資料,雖然有收獲但是還是感覺(jué)大神們寫(xiě)的太高端,不夠詳細(xì),對(duì)于我這種學(xué)渣看起來(lái)還是迷迷糊糊。所以整理了一下自己的經(jīng)驗(yàn),把整個(gè)過(guò)程記錄了下來(lái)。沒(méi)有很多語(yǔ)言全部是截圖大家湊合看吧。附有源代碼和Word文檔。

2017-10-12 12:32:44

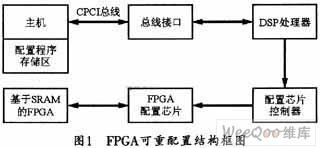

本文提出了一種基于嵌入式系統(tǒng)和Internet的FPGA動(dòng)態(tài)配置方案。

2021-05-27 06:38:55

本文介紹的基于FPGA的可重配置系統(tǒng)可以在設(shè)計(jì)后期甚至量產(chǎn)階段通過(guò)重新編程以適應(yīng)標(biāo)準(zhǔn)和協(xié)議的改變。

2021-05-13 06:35:49

軟件無(wú)線電(SDR)是帶有可重配置硬件平臺(tái)的無(wú)線設(shè)備。這些可重配置硬件平臺(tái)能夠被用于多種通信標(biāo)準(zhǔn),并將在最終實(shí)現(xiàn)認(rèn)知無(wú)線電(CR)的過(guò)程中發(fā)揮關(guān)鍵作用。與此同時(shí),由于SDR具有更低的成本、更大

2019-07-29 07:21:01

結(jié)構(gòu),上層為配置存儲(chǔ)器,下層是硬件邏輯層。通過(guò)上層配置信息控制硬件層門電路的通斷,改變芯片內(nèi)基本邏輯塊的布線,從而形成特定的功能。這種架構(gòu)為動(dòng)態(tài)重構(gòu)技術(shù)實(shí)現(xiàn)提供了可能。一個(gè)FPGA大型數(shù)字系統(tǒng)總是由很多

2015-02-05 15:31:50

是否有任何教程顯示如何使用PowerPC或microblaze作為重配置控制器?我目前使用Impact工具使用部分比特流(ISE和Planahead 12.1)重新配置FPGA,但我想要一個(gè)重配置

2019-01-22 11:05:28

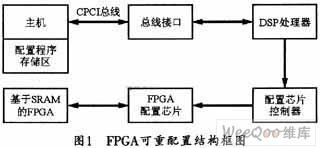

或系統(tǒng)重構(gòu)。結(jié)合對(duì)FPGA重配置方案的軟硬件設(shè)計(jì),本文通過(guò)PC機(jī)并通過(guò)總線(如PCI總線)將配置數(shù)據(jù)流下載到硬件功能模塊的有關(guān)配置芯片,從而完成配置FPGA的全過(guò)程。有誰(shuí)知道,具體該怎么做嗎?

2019-08-07 06:17:30

我試圖找出部分重配置的配置架構(gòu)。從我之前使用Virtex-5 FPGA的工作開(kāi)始,幀將跨越時(shí)鐘區(qū)域的垂直切片。但是,我找不到任何類似的Virtex-7文檔。我找到的只是configuraiton指南

2020-05-29 08:54:01

隨著大規(guī)模集成電路的快速發(fā)展,系統(tǒng)設(shè)計(jì)已從傳統(tǒng)的追求大規(guī)模、高密度逐漸轉(zhuǎn)向提高資源利用率,使有限的資源可以實(shí)現(xiàn)更大規(guī)模的邏輯設(shè)計(jì)。利用現(xiàn)場(chǎng)可編程邏輯器件FPGA的多次可編程配置特點(diǎn),通過(guò)重新下載存儲(chǔ)

2019-08-06 07:05:37

存儲(chǔ)配置數(shù)據(jù)。配置數(shù)據(jù)決定了PLD內(nèi)部互連和功能,改變配置數(shù)據(jù),也就改變了器件的邏輯功能。SRAM編程時(shí)間短,為系統(tǒng)動(dòng)態(tài)改變PLD的邏輯功能創(chuàng)造了條件。但由于SRAM的數(shù)據(jù)易失的,配置數(shù)據(jù)必須保存在PLD器件以外的非易失存儲(chǔ)器內(nèi),才能實(shí)現(xiàn)在線可重配置(ICR)。

2019-08-22 06:31:02

uCLinux作為操作系統(tǒng)平臺(tái),設(shè)計(jì)出可動(dòng)態(tài)配置的片上系統(tǒng)(rSoC)。uCLinux從遠(yuǎn)程服務(wù)器上下載FPGA程序代碼,然后利用shell腳本工具將代碼寫(xiě)進(jìn)FPGA芯片,實(shí)現(xiàn)系統(tǒng)功能的可動(dòng)態(tài)擴(kuò)展。 (2

2019-04-04 17:12:33

,上至高性能CPU,下至簡(jiǎn)單的74電路,都可以用它來(lái)實(shí)現(xiàn)。FPGA在嵌入式系統(tǒng)中的應(yīng)用越來(lái)越廣泛。John Williams和NeilBergmann用uCLinux作為操作系統(tǒng)平臺(tái),設(shè)計(jì)出可動(dòng)態(tài)配置

2018-10-26 09:22:17

,上至高性能CPU,下至簡(jiǎn)單的74電路,都可以用它來(lái)實(shí)現(xiàn)。FPGA在嵌入式系統(tǒng)中的應(yīng)用越來(lái)越廣泛。John Williams和NeilBergmann用uCLinux作為操作系統(tǒng)平臺(tái),設(shè)計(jì)出可動(dòng)態(tài)配置的片

2018-10-28 09:53:34

對(duì)于城域網(wǎng)絡(luò)和長(zhǎng)途網(wǎng)絡(luò)來(lái)說(shuō),如果光傳送層具有遠(yuǎn)程重新配置的能力,則可以極大地降低運(yùn)營(yíng)成本。運(yùn)營(yíng)商也已經(jīng)意識(shí)到這種潛力,并在最近業(yè)務(wù)網(wǎng)絡(luò)的招標(biāo)中加入了對(duì)于可重配置光分插復(fù)用器(ROADM)以及多維光

2019-08-08 06:31:07

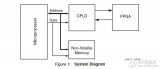

本文提出的通過(guò)微處理器加FPGA結(jié)合串行菊花鏈實(shí)現(xiàn)可重構(gòu)的方式,實(shí)現(xiàn)了動(dòng)態(tài)可重構(gòu)FPGA結(jié)構(gòu)設(shè)計(jì)的一種應(yīng)用。

2021-05-10 06:22:19

日前,Altium 宣布推出另一款面向桌面 NanoBoard 可重構(gòu)硬件開(kāi)發(fā)平臺(tái)的全新子板,進(jìn)一步幫助電子設(shè)計(jì)人員輕松利用可編程硬件的優(yōu)勢(shì)。這款最新插入式子板采用 780 BGA 封裝,內(nèi)置

2019-07-25 06:07:43

親愛(ài)的先生: 我是xilinx產(chǎn)品的新手。 我有興趣購(gòu)買xilinx開(kāi)發(fā)板。 Isaw avideoabout是“可擴(kuò)展的處理平臺(tái)”。 我想購(gòu)買具有這種“可擴(kuò)展處理平臺(tái)”的工具包。能否列出具有此功能

2019-01-22 10:12:53

賽靈思Zynq-7000可擴(kuò)展處理平臺(tái)(EPP)將雙ARM Cortex-A9 MPCore處理器系統(tǒng)與可編程邏輯和硬IP外設(shè)緊密集成在一起,提供了靈活性、可配置性和性能的完美組合。圍繞其剛剛推出

2019-05-16 10:44:42

近日IEEE AutoTestCon上, Aeroflex 宣布推出適用于無(wú)線應(yīng)用場(chǎng)合、頻率可高達(dá)6GHz的新型模塊化RF測(cè)試平臺(tái)。這個(gè)可擴(kuò)展平臺(tái)具有靈活性高的特點(diǎn),易于在從研發(fā)到生產(chǎn)等無(wú)線開(kāi)發(fā)

2019-06-28 06:39:18

動(dòng)態(tài)資源控制就是通過(guò)傳輸信道重配置、無(wú)線承載(RB重配置)等手段動(dòng)態(tài)控制無(wú)線資源的過(guò)程,從而達(dá)到資源合理分配和有效利用。本章通過(guò)舉例方式說(shuō)明動(dòng)態(tài)資源控制流程

2009-05-30 17:18:10 5

5 本文提出了一種全新的總線可重配置的多處理器架構(gòu)。該架構(gòu)結(jié)合了多核與可重配置處理器的優(yōu)勢(shì),具有并行性高、計(jì)算能力強(qiáng)、結(jié)構(gòu)復(fù)雜度低并且應(yīng)用領(lǐng)域廣泛靈活的特點(diǎn)。對(duì)

2009-06-13 14:11:04 11

11 該文基于現(xiàn)有端到端可重配置系統(tǒng)架構(gòu),提出了一種改進(jìn)的動(dòng)態(tài)門限聯(lián)合負(fù)載控制方法,以適應(yīng)不同負(fù)載條件下對(duì)負(fù)載均衡的要求,達(dá)到資源的有效利用。同時(shí),結(jié)合終端的可重配

2009-11-19 16:41:25 13

13 為了應(yīng)用FPGA中內(nèi)嵌的數(shù)字時(shí)鐘管理(DCM)模塊建立可靠的系統(tǒng)時(shí)鐘。首先對(duì)DCM的工作原理進(jìn)行分析,然后根據(jù)DCM的工作原理給出了一種DCM動(dòng)態(tài)重配置的設(shè)計(jì)方法。DCM動(dòng)態(tài)重配置設(shè)計(jì)是利

2010-07-28 17:03:52 28

28 介紹了基于ARM和FPGA的端到端重配置終端的硬件平臺(tái)設(shè)計(jì)方法。給出了系統(tǒng)設(shè)計(jì)的硬件結(jié)構(gòu)和重要接口, 提出了由ARM微處理器通過(guò)JTAG在系統(tǒng)配置FPGA的方法, 以滿足重配置系統(tǒng)中軟件

2010-09-14 16:40:09 21

21 本文檔主要是以Altera公司的Stratix II系列的FPGA器件為例,介紹了其內(nèi)嵌的增強(qiáng)型可重配置PLL在不同的輸入時(shí)鐘頻率之間的動(dòng)態(tài)適應(yīng),其目的是通過(guò)提供PLL的重配置功能,使得不需要對(duì)

2010-11-02 15:17:24 27

27 實(shí)現(xiàn)了一種用于上位機(jī)和FPGA處理板之間通信的可重配置接口,詳細(xì)介紹了該接口的包格式設(shè)計(jì)和FPGA邏輯設(shè)計(jì)。仿真結(jié)果表明,該可重配置接口能根據(jù)信令,實(shí)現(xiàn)準(zhǔn)實(shí)時(shí)在線參數(shù)配置

2010-11-22 15:15:28 12

12 在當(dāng)今復(fù)雜數(shù)字電路設(shè)計(jì)中,大多采用以“嵌入式微控制器+FPGA”為核心的體系結(jié)構(gòu)。提出了一種對(duì)現(xiàn)有傳統(tǒng)FPGA配置方案硬件電路稍做調(diào)整并增加部分軟件功能,即可實(shí)現(xiàn)FPGA動(dòng)態(tài)

2010-12-08 15:52:01 19

19 FPGA的全局動(dòng)態(tài)可重配置技術(shù)主要是指對(duì)運(yùn)行中的FPGA器件的全部邏輯資源實(shí)現(xiàn)在系統(tǒng)的功能變換,從而實(shí)現(xiàn)硬件的時(shí)分復(fù)用。提出了一種基于System ACE的全局動(dòng)態(tài)可重配置設(shè)計(jì)方法,

2011-01-04 17:06:01 54

54 摘要: 一種基于嵌入式系統(tǒng)和Inlternet的FPGA動(dòng)態(tài)配置方案。詳細(xì)介紹了該方案的設(shè)計(jì)思想,并給出了設(shè)計(jì)實(shí)例。與傳統(tǒng)的FPGA配置方案相比,該方案具有靈活

2009-06-20 10:37:59 355

355

基于SRAM的可重配置PLD(可編程邏輯器件)的出現(xiàn),為系統(tǒng)設(shè)計(jì)者動(dòng)態(tài)改變運(yùn)行電路中PLD的邏輯功能創(chuàng)造了條件。PLD使用SRAM單元來(lái)保存字的配置數(shù)據(jù)決

2009-06-20 11:05:37 845

845

采用VC++程序的FPGA重配置設(shè)計(jì)方案利用現(xiàn)場(chǎng)可編程邏輯器件FPGA的多次可編程配置特點(diǎn),通過(guò)重新下載存儲(chǔ)于存儲(chǔ)器的不同系統(tǒng)數(shù)據(jù)

2010-04-14 15:14:57 580

580

為了滿足對(duì)分?jǐn)?shù)階 信號(hào)變換 進(jìn)行實(shí)時(shí)計(jì)算的要求,提出一種基于Altera St ratix II FPGA 平臺(tái)的可重配置分?jǐn)?shù)階信號(hào)變換處理器的硬件實(shí)現(xiàn)方案. 根據(jù)角度分解的算法,設(shè)計(jì)了一種通用的硬件框

2011-07-04 15:13:03 33

33 利用賽靈思 FPGA 的動(dòng)態(tài)重配置功能,同構(gòu)多線程執(zhí)行模型可同時(shí)兼得軟件靈活性和硬件性能。

2011-09-01 09:27:26 584

584

基于 FPGA 的 RCS 有幾項(xiàng)值得注意的設(shè)計(jì)事項(xiàng)與優(yōu)勢(shì)。其核心部分是我們連接在一起以構(gòu)成單個(gè)計(jì)算系統(tǒng)的數(shù)個(gè)FPGA。在我們的可重配置系統(tǒng)中,我們使用了正交通信系統(tǒng),將 FPGA 布置在矩

2011-09-20 08:57:32 27

27 WP374 Xilinx FPGA的部分重配置

2012-03-07 14:34:39 34

34 在過(guò)去,靜態(tài)決策最壞情況分配曾為嚴(yán)格的實(shí)時(shí)約束提供了解決方案,而現(xiàn)在靈活性也成為一項(xiàng)要求。法國(guó)某研究項(xiàng)目建議使用的解決方案是一種分布在 FPGA 資源上,對(duì)軟硬件線程進(jìn)行

2012-05-09 10:40:11 1675

1675

本文介紹了XiLinx FPGA中DCM的結(jié)構(gòu)和相關(guān)特性,提出了一種基于XiLinx FPGA的DCM動(dòng)態(tài)重配置的原理方法,并給出了一個(gè)具體的實(shí)現(xiàn)系統(tǒng)。系統(tǒng)僅通過(guò)外部和......

2012-05-25 13:42:50 39

39 打造完全可重配置運(yùn)動(dòng)控制系統(tǒng) ,NI LabVIEW。

2016-03-21 16:19:31 0

0 們快速開(kāi)發(fā)和部署加速平臺(tái)。專門針對(duì)云級(jí)應(yīng)用而設(shè)計(jì)的基于FPGA的賽靈思可重配置加速堆棧,包括庫(kù)、框架集成、開(kāi)發(fā)板并支持OpenStack。通過(guò)賽靈思FPGA,該可重配置加速堆棧方案提供了業(yè)界最高的計(jì)算效率:比x86服務(wù)器CPU高出40倍;比競(jìng)爭(zhēng)型FPGA方案高出6倍。

2016-11-16 16:42:23 648

648 一種基于憶阻器的可重配置邏輯電路_張波

2017-01-08 10:18:57 4

4 這里提到的局部重配置技術(shù)(Partial Reconfiguration) 是現(xiàn)場(chǎng)可編程門陣列(呵呵,就是FPGA了) 器件中的一部分。指的是在FPGA其他部分還在正常運(yùn)行的情況下對(duì)其局部進(jìn)行的重新配置。

2017-02-11 16:32:11 2622

2622 Suite HLx 2017.1版中廣泛納入部分重配置技術(shù),為有線和無(wú)線網(wǎng)絡(luò)、測(cè)試測(cè)量、航空航天與軍用、汽車以及數(shù)據(jù)中心等豐富應(yīng)用,提供動(dòng)態(tài)的現(xiàn)場(chǎng)升級(jí)優(yōu)勢(shì)和更高的系統(tǒng)集成度。

2017-04-27 18:38:08 2782

2782

工作效率。通過(guò)FPGA 的多重配置可以有效地精簡(jiǎn)控制結(jié)構(gòu)的設(shè)計(jì),同時(shí)可以用邏輯資源較少的FPGA 器件實(shí)現(xiàn)需要很大資源才能實(shí)現(xiàn)的程序。以Virtex5系列開(kāi)發(fā)板和配置存儲(chǔ)器SPIFLASH為基礎(chǔ),從硬件電路和軟件設(shè)計(jì)兩個(gè)方面對(duì)多重配置進(jìn)行分析,給出了多

2017-10-12 17:57:08 15

15 FPGA 動(dòng)態(tài)局部重配置技術(shù)是近幾年才發(fā)展起來(lái)的一項(xiàng)新技術(shù)。這項(xiàng)技術(shù)可以使 FPGA運(yùn)行時(shí),通過(guò) JTAG或 SelectMAP(ICAP)動(dòng)態(tài)重配置部分區(qū)域,而不影響非重配置區(qū)域的正常工作

2017-10-18 16:38:59 4

4 視頻、影像和電信市場(chǎng)的標(biāo)準(zhǔn)推動(dòng)了異構(gòu)可重配置 DSP硬件平臺(tái)的使用。就本文而言,這些平臺(tái)包括 DSP 處理器和 FPGA,它們提供的現(xiàn)成硬件解決方案可以解決視頻、影像和電信設(shè)計(jì)中的重大難題,但仍不

2017-10-20 09:07:37 0

0 視頻、影像和電信市場(chǎng)的標(biāo)準(zhǔn)推動(dòng)了異構(gòu)可重配置DSP硬件平臺(tái)的使用。在本文中這些平臺(tái)包括DSP處理器和FPGA,它們提供的現(xiàn)成硬件解決方案可以解決視頻、影像和電信設(shè)計(jì)中的重大難題,同時(shí)又不失差異化

2017-11-06 13:59:42 2

2 的FPGA 快速動(dòng)態(tài)重構(gòu)方案, 實(shí)現(xiàn)了同一硬件平臺(tái)下多個(gè)FPGA 設(shè)計(jì)版本的在線動(dòng)態(tài)配置和功能重構(gòu), 該技術(shù)已在工程中成功應(yīng)用。

2017-11-22 07:55:01 937

937

:不存在時(shí)延,這種方法基本不占用資源(在FPGA上占用的查找表不足300個(gè)),而且設(shè)計(jì)人員可以優(yōu)化部分重配置的時(shí)序。

2017-11-22 17:08:56 1492

1492 的應(yīng)用。在主流的FPGA中,絕大多數(shù)都采用了SRAM來(lái)存放配置數(shù)據(jù),稱為SRAM FPGA。這種FPGA的突出優(yōu)點(diǎn)是可以進(jìn)行多次配置。通過(guò)給FPGA加載不同的配置數(shù)據(jù),即可令其實(shí)現(xiàn)不同的邏輯功能.FPGA這種可重配置的能力將給數(shù)字系統(tǒng)的設(shè)計(jì)帶來(lái)很大的方便。

2018-07-18 12:50:00 2407

2407

針對(duì)虛擬網(wǎng)絡(luò)映射中能耗過(guò)高、接收率偏低和負(fù)載不夠均衡等問(wèn)題,提出一種基于虛擬資源整合的綜合性重配置算法-HEAR算法。該重配置算法分為兩個(gè)階段:節(jié)點(diǎn)重配置階段優(yōu)先將映射虛擬節(jié)點(diǎn)最少的物理節(jié)點(diǎn)上的虛擬

2017-12-20 11:31:58 0

0 如何在 Arria 10 中實(shí)現(xiàn) I/O 鎖相環(huán) (PLL) 重配置

2018-06-20 00:57:00 3438

3438

賽靈思公司(Xilinx)宣布,在2016全球超算大會(huì)(SC 16)上宣布推出一套全新的技術(shù)——賽靈思可重配置加速堆棧方案,旨在幫助全球最大的云端服務(wù)供應(yīng)商們快速開(kāi)發(fā)和部署加速平臺(tái)。專門針對(duì)

2018-07-31 09:08:00 731

731 Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允許用戶在不掉電重啟的情況下,根據(jù)不同時(shí)刻的需求,可以從FLASH 中貯存的多個(gè)比特文件選擇加載其中的一個(gè),實(shí)現(xiàn)系統(tǒng)功能的變換。

2018-12-04 08:37:00 4654

4654

結(jié)合對(duì)FPGA重配置方案的軟硬件設(shè)計(jì),本文通過(guò)PC機(jī)并通過(guò)總線(如PCI總線)將配置數(shù)據(jù)流下載到硬件功能模塊的有關(guān)配置芯片,從而完成配置FPGA的全過(guò)程。該方法的軟件部分基于Visual C++的開(kāi)發(fā)環(huán)境,并用C++語(yǔ)言開(kāi)發(fā)動(dòng)態(tài)連接庫(kù),以用于軟件設(shè)計(jì)應(yīng)用程序部分的調(diào)用。

2018-12-30 09:26:00 2425

2425

本視頻介紹了UltraScale +芯片的部分重配置功能,展示了Vivado Design Suite中部分重配置的新功能,并介紹了對(duì)部分重配置的更廣泛的訪問(wèn)權(quán)限

2018-11-20 06:25:00 3831

3831 了解Xilinx如何在UltraScale器件中推進(jìn)其突破性的部分重配置技術(shù)。

該視頻全面介紹了20nm UltraScale FPGA的新功能,擴(kuò)展功能和系統(tǒng)要求。

2018-11-26 06:45:00 1988

1988 關(guān)鍵詞:PLD , SRAM , 可重配置電路 由于SRAM的可重配置PLD(可編程邏輯器件)的出現(xiàn),為系統(tǒng)設(shè)計(jì)者動(dòng)態(tài)改變運(yùn)行電路中PLD的邏輯功能創(chuàng)造了條件。PLD使用SRAM單元來(lái)保存字的配置

2019-02-23 14:30:01 675

675

軟件無(wú)線電硬件平臺(tái)的一個(gè)重要和必須的特點(diǎn)就是硬件的可配置性。那么具體到FPGA來(lái)說(shuō)能實(shí)現(xiàn)什么樣的配置呢?

2019-06-22 09:55:41 931

931

TD-LTE SRS帶寬重配置導(dǎo)致掉話率高案例說(shuō)明。

2021-03-25 09:51:33 20

20 Partial Reconfiguration(部分重配置)在現(xiàn)在的FPGA應(yīng)用中越來(lái)越常見(jiàn),我們這次的教程以Project模式為例來(lái)說(shuō)明部分重配置的操作過(guò)程。

2021-07-05 15:28:24 3140

3140

電子發(fā)燒友網(wǎng)站提供《ELF2 FPGA PLL動(dòng)態(tài)配置.pdf》資料免費(fèi)下載

2022-09-26 15:13:06 0

0 一般情況下,要重新配置一個(gè)FPGA需要使其處于復(fù)位狀態(tài),并通過(guò)外部控制器重新加載一個(gè)新設(shè)計(jì)到器件中。而局部重配置技術(shù)允許在FPGA內(nèi)部或外部的控制器在加載一個(gè)局部設(shè)計(jì)到一個(gè)可重配置模塊中時(shí)

2023-03-17 14:03:39 1508

1508 除通過(guò)外部多功能IO來(lái)選擇之外,易靈思通過(guò)內(nèi)部重配置實(shí)現(xiàn)遠(yuǎn)程更新操作也非常簡(jiǎn)單。

2023-05-30 09:24:32 712

712

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論