5 系統(tǒng)擴(kuò)展

本文是針對(duì)8×8點(diǎn)陣設(shè)計(jì),故每次取8個(gè)字形碼,如果是16×16點(diǎn)陣,將RONZI中存儲(chǔ)的字形碼改為16位,數(shù)據(jù)線改為16位,一個(gè)漢字需要16個(gè)16位的字形碼,數(shù)據(jù)分配模塊MUX、移位模塊YW、顯示模塊DISP,均要將輸入輸出數(shù)據(jù)中的原來的8位改成相應(yīng)的16位。掃描及取字型碼計(jì)數(shù)器CNT_SM應(yīng)改為CNT計(jì)數(shù)器的低4位。一個(gè)16×16點(diǎn)陣漢字的移進(jìn)移出共需32個(gè)狀態(tài)。由5位的計(jì)數(shù)器提供。如用CNT[16..0]中的14~10位作為該計(jì)數(shù)器,這可在時(shí)鐘計(jì)數(shù)器產(chǎn)生單元CLK_GE中應(yīng)做相應(yīng)修改,字計(jì)數(shù)器CNT WORD按照每取16個(gè)字進(jìn)行加1統(tǒng)計(jì)。顯示DISP部分的譯碼器要由3-8譯碼改為4-16譯碼。顯示的漢字信息越多,ROM的地址線位數(shù)越多,字計(jì)數(shù)器CNT_WORD應(yīng)在時(shí)鐘計(jì)數(shù)器產(chǎn)生單元GE_CLK中,將相應(yīng)的計(jì)數(shù)器位數(shù)擴(kuò)展,由CNT計(jì)數(shù)器的最高位到位15來承擔(dān)。若還是8個(gè)漢字,計(jì)數(shù)器應(yīng)為CNT[17..O],CNT[17..15]為字計(jì)數(shù)器;若為16個(gè)漢字,計(jì)數(shù)器應(yīng)為CNT[18..O],CNT[18..15]為字計(jì)數(shù)器,…,依次類推。

6 結(jié)語

本文在KH31001開發(fā)板上實(shí)現(xiàn)了基于Altera公司的Cyclone I系列FPGA器件EPlC6Q240C8硬件及VHDL硬件描述語言設(shè)計(jì)的LED點(diǎn)陣漢字滾動(dòng)顯示,能在8×8點(diǎn)陣上滾動(dòng)顯示“元旦生日開心快樂”8個(gè)漢字。文中從LED點(diǎn)陣顯示漢字的原理闡述出發(fā),給出了點(diǎn)陣漢字滾動(dòng)顯示控制器的原理圖,部分模塊的VHDL源程序及時(shí)序仿真圖,并能由按鍵選擇其滾動(dòng)方式:左移、右移、上移、下移等,給出了系統(tǒng)擴(kuò)展成16×16點(diǎn)陣漢字滾動(dòng)的改動(dòng)思路。從文中描述的系統(tǒng)擴(kuò)展方案中看出,當(dāng)系統(tǒng)顯示字符個(gè)數(shù)變化時(shí),只需對(duì)控制邏輯和連接關(guān)系做適當(dāng)?shù)男薷模賹⑿薷耐瓿傻某绦蛳螺d到器件即可,顯然,系統(tǒng)的維護(hù)和修改是極其方便和容易的,本文對(duì)同類設(shè)計(jì)也具有一定的參考價(jià)值。

四、數(shù)字控制振蕩器(NCO)的FPGA實(shí)現(xiàn)

NCO(N umerically Controlled Oscillator)是用于產(chǎn)生一個(gè)理想的、數(shù)字可控的正弦或余弦波的數(shù)字控制式振蕩器,其實(shí)現(xiàn)方法有實(shí)時(shí)計(jì)算法和查表法等多種。實(shí)時(shí)計(jì)算法的正弦波樣本以實(shí)時(shí)計(jì)算產(chǎn)生,該方法因其計(jì)算需要耗費(fèi)很多時(shí)間,因而只能產(chǎn)生較低頻率的正弦波,而且存在計(jì)算精度與計(jì)算時(shí)間的矛盾。由于在需要產(chǎn)生高速的正交信號(hào)時(shí),實(shí)時(shí)計(jì)算法將無法實(shí)現(xiàn)。因此,在實(shí)際應(yīng)用中一般采用最有效、最簡(jiǎn)單的查表法,即事先根據(jù)各個(gè)NCO正弦波的相位計(jì)算好相位的正弦值,并按相位作為地址信息存儲(chǔ)該相位的正弦值數(shù)據(jù)。

1 NCO的基本原理

在通過相位累加產(chǎn)生地址信息時(shí),通常需要輸出當(dāng)前時(shí)刻的相位值所對(duì)應(yīng)的正弦值,即以參考頻率源對(duì)相位進(jìn)行等可控間隔采樣。眾所周知,理想的正弦波信號(hào)S(t)可以表示成:

![]()

式(1)說明,信號(hào)s(t)在振幅A和初相φ確定之后,其頻率可以由相位來唯一確定。即:

![]()

NCO就是利用式(2)中φ(t)與時(shí)間t成線性關(guān)系的原理來進(jìn)行頻率合成的,也就是說,在時(shí)間t=△t間隔內(nèi),正弦信號(hào)的相位增量△φ與正弦信號(hào)的頻率f可構(gòu)成一一對(duì)應(yīng)關(guān)系,也就是說,對(duì)式(2)兩端進(jìn)行微分后有:

![]()

。

由上面的討論可知:

![]()

其中,△θ為一個(gè)采樣間隔△t之間的相位增量,采樣周期

![]()

。故式(3)可改寫為:

![]()

由式(4)可知,如果可以控制△θ,就可以控制不同的頻率輸出。由于△θ受頻率控制字FCW的控制,即:

![]()

,所以,改變FCW就可以得到不同的輸出頻率f0,然后經(jīng)代換處理可得如下方程:

式(5)和式(6)中的L為相位累加器的位數(shù)。根據(jù)Nyquist準(zhǔn)則,允許輸出的頻率最高為FCLK/2,即

![]()

。但在實(shí)際工程中,由于受到低通濾波器的限制,一般輸出的頻率

![]()

。

2 NCO的性能指標(biāo)

NCO的性能指標(biāo)包括信號(hào)頻率分辨率、信噪比(SNR)、無雜散動(dòng)態(tài)范圍(SFDR)和輸出的信號(hào)正交性。這些性能指標(biāo)取決于NCO的數(shù)據(jù)位數(shù)。NCO的數(shù)據(jù)位數(shù)包括用于表示相位數(shù)據(jù)的位數(shù)n和表示相位的正弦值數(shù)據(jù)的位數(shù)nb,二者之間存在nb取決于n的關(guān)系,且前者必須能夠表示相位變化時(shí)其相位正弦值變化的最小值和最大值。而這又分為兩種情況:

第一種情況是相位最小變化值的正弦值最小變化發(fā)生在π/2-△φ~π/2,π/2~π/2+△φ,3π/2-△φ~3π/2,3π/2~3π/2+△φ,同時(shí)其相位的取值是在0~2π間且等間隔地分為2n爪取值點(diǎn),因此,由正弦波的特性可知:只需要討論相位在π/2-△φ與π/2取值點(diǎn)的正弦值之差:

第二種情況是相位最小變化值的正弦值的最大變化發(fā)生在0~△φ,π-△φ~π,π~π+△φ,2π-△φ~2π取值點(diǎn)處。該情況可以通過類似于第一種情況的推導(dǎo)方法得到:

設(shè)計(jì)時(shí)可以根據(jù)式(9)和式(10)較好地取值n和nb,以避免相位的分辨率發(fā)生鈍化,并很好地達(dá)到設(shè)計(jì)要求。

NCO的噪聲是因?yàn)榇嬖谡抑档牧炕`差而引入的,且量化誤差由表示正弦值的位數(shù)決定,其近似關(guān)系為:

式中,B是作為尋址ROM的地址的舍位位數(shù),n是相位位數(shù)。NCO的另一個(gè)性能參數(shù)是頻率分辨率△f,該參數(shù)取決于相位位數(shù),其關(guān)系式為:

![]()

3 NCO在FPGA中的實(shí)現(xiàn)

NCO的查找表是一個(gè)正弦值表,該表的正弦值是按照相位作為存儲(chǔ)地址來進(jìn)行存儲(chǔ)的,而且一般以相位遞增的方式存儲(chǔ)。利用正弦波的奇偶對(duì)稱性,可以把2π相位分成4等份,然后利用各等份之間的對(duì)稱性來實(shí)現(xiàn)地址信息的映射,通常只存儲(chǔ)[0,π/2]象限內(nèi)的幅度碼。

相位累加器可完成相位累加,即每來1個(gè)時(shí)鐘就累加1次φ=φ+△φ,且采用流水線方式工作。本設(shè)計(jì)采用QUARTUS II中IP核自帶的一種32位累加器來實(shí)現(xiàn)相位的累加。

邏輯轉(zhuǎn)換完成后,可采用小表結(jié)構(gòu)功能塊把相位累加器產(chǎn)生的最高2位信號(hào)轉(zhuǎn)換為地址控制信號(hào)和象限轉(zhuǎn)換控制信號(hào)。其中地址控制信號(hào)是根據(jù)最高兩位信號(hào)來控制地址從0開始遞增方式產(chǎn)生還是從2L開始以遞減方式產(chǎn)生。

正弦表是每來一個(gè)時(shí)鐘輸出一個(gè)大于零的正弦值數(shù)據(jù),這些數(shù)據(jù)可作為象限變換器的輸入,由象限變換器完成數(shù)據(jù)的象限變換。其轉(zhuǎn)換原則是:象限控制信號(hào)根據(jù)正弦信號(hào)的對(duì)稱性把查表得到的數(shù)據(jù)轉(zhuǎn)換為正負(fù)數(shù)據(jù),并對(duì)于正弦信號(hào)的1、2象限數(shù)據(jù)進(jìn)行加零操作,而對(duì)3、4象限的數(shù)據(jù)進(jìn)行求補(bǔ)運(yùn)算。余弦數(shù)據(jù)也同樣,在1、4象限對(duì)數(shù)據(jù)進(jìn)行加零操作,2、3象限數(shù)據(jù)進(jìn)行求補(bǔ)運(yùn)算。

4 仿真結(jié)果

利用上述小表結(jié)構(gòu)實(shí)現(xiàn)的NCO可以輸出多種頻率信號(hào)并減少資源消耗,影響系統(tǒng)輸出頻率的因素主要是工作頻率和器件性能。

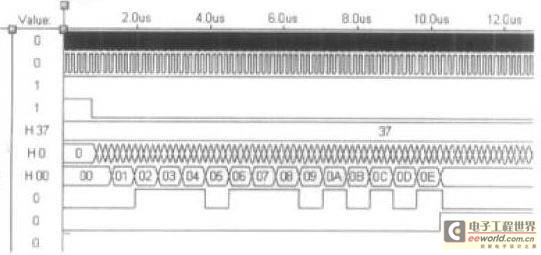

圖1所示是整個(gè)NCO在QUARTUS II中的仿真波形圖。

在圖1所示的波形圖中,CLK是時(shí)鐘輸入頻率(為65.6 MHz),CLR為系統(tǒng)復(fù)位信號(hào),相位累加器的位數(shù)L為32位,輸出信號(hào)幅度位數(shù)為12位(包括符號(hào)位),相位寬度為12位,這樣,由式(5)便可得到頻率控制字FCW為269591793,圖1中的COS_OUT與SIN_OUT是系統(tǒng)輸出信號(hào),頻率為4.08 MHz。

由式(11)、(12)、(13)可得,此系統(tǒng)的信噪比和SFDR分別為74 dB和84 dB。

圖2所示是將波形文件中的正弦余弦數(shù)據(jù)讀入MATLAB中所顯示出來的波形。

5 結(jié)束語

本文通過分析數(shù)控振蕩器的實(shí)現(xiàn)原理和性能,給出了通過FPGA來實(shí)現(xiàn)NCO的具體方法,同時(shí)通過QUARTUSⅡ中的仿真驗(yàn)證了本設(shè)計(jì)的正確性。結(jié)果證明,用該方法設(shè)計(jì)的NCO可以輸出多種頻率的信號(hào),同時(shí)也可以減少資源消耗。

?

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論