引 言

信號發生器又稱信號源或振蕩器,在生產實踐和科技領域中有著廣泛的應用。能夠產生多種波形,如三角波、鋸齒波、矩形波(含方波)、正弦波的電路被稱為函數信號發生器。函數信號發生器的實現方法通常是采用分立元件或單片專用集成芯片,但其頻率不高,穩定性較差,且不易調試,開發和使用上都受到較大限制。隨著可編程邏輯器件(FPGA)的不斷發展,直接頻率合成(DDS)技術應用的愈加成熟,利用DDS原理在FP-GA平臺上開發高性能的多種波形信號發生器與基于DDS芯片的信號發生器相比,成本更低,操作更加靈活,而且還能根據要求在線更新配置,系統開發趨于軟件化、自定義化。本文研究了基于FPGA的DDS信號發生器設計,實現了滿足預定指標的多波形輸出。

1 DDS基本原理

DDS建立在采樣定理基礎上,首先對需要產生的波形進行采樣,將采樣值數字化后存入存儲器作為查找表,然后通過查表讀取數據,再經D/A轉換器轉換為模擬量,將保存的波形重新合成出來。DDS基本原理框圖如圖1所示。

除了濾波器(LPF)之外,DDS系統都是通過數字集成電路實現的,易于集成和小型化。系統的參考時鐘源通常是一個具有高穩定性的晶體振蕩器,為各組成部分提供同步時鐘。頻率控制字(FSW)實際上是相位增量值(二進制編碼)作為相位累加器的累加值。相位累加器在每一個參考時鐘脈沖輸入時,累加一次頻率字,其輸出相應增加一個步長的相位增量。由于相位累加器的輸出連接在波形存儲器(ROM)的地址線上,因此其輸出的改變就相當于查表。這樣就可以通過查表把存儲在波形存儲器內的波形抽樣值(二進制編碼)查找出來。ROM的輸出送到D/A轉換器,經D/A轉換器轉換成模擬量輸出。

2 系統總體方案設計

該設計以FPGA開發平臺為核心,將各波形的幅值/相位量化數據存儲在ROM內,按照設定頻率,以相應頻率控制字k為步進,對相位進行累加,以累加相位值作為地址碼讀取存放在存儲器內的波形數據,經D/A轉換和幅度控制、濾波即可得到所需波形。波形發生器采取全數字化結構,用硬件描述語言Verilog設計實現其頻率可調可顯示。經開發平臺的D/A轉化和外加濾波整形處理波形數據,理論上能夠實現任意頻率的各種波形。系統總體設計方框圖如圖2所示。

系統按工作原理和控制對象的先后分為三個功能單元:波形數據產生單元、D/A轉化單元和濾波整形處理單元。波形數據產生單元除具有波形數據輸出功能外,還有頻率設置和輸出顯示功能。波形信號頻率可設置范圍為0~99 999 999 Hz,系統時鐘采用外接晶體振蕩器40 MHz時鐘脈沖,頻率穩定度優于10-4輸出采用8位LED數碼循環動態顯示。D/A轉換單元負責對從ROM表里讀取的波形數據進行D/A轉換,對D/A轉換器件的選用從建立時間、位數、轉化誤差和轉換時間等四個方面考慮。濾波整形處理單元完成對D/A轉換的模擬波進行平滑,濾除雜波和高頻干擾,補償頻帶損耗和幅度損失,最終輸出低誤差、高質量、滿足題設要求的波形。

3 系統功能單元實現

3.1 波形數據產生單元

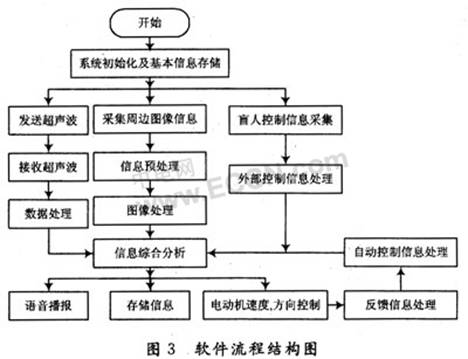

波形數據產生單元是信號發生器設計的主體。在此,采用DDS原理設計的信號發生器能完成三種波形(正弦、三角和方波)數據的產生,而且根據控制信號還可完成選定波形指定頻率的輸出。波形數據產生單元按功能實現上的相互聯系可劃分為頻率控制字生成模塊、相位累加器模塊和波形數據ROM表模塊,如圖3所示。其中,頻率控制字生成模塊可根據輸入產生指定頻率字,同時顯示輸入頻率數字。相位累加器模塊負責對所選波形的相位尋址,以頻率控制字作為步長反復進行累加運算。波形數據ROM表模塊存放三種波形的幅值/相位量化值,通過地址選擇相應波形的數據。

系統輸入控制使用4×4鍵盤.鍵盤主要按鍵功能介紹如下:

“0~9”:數字鍵,設定信號頻率;

“確定”:用于對波形信號設置的確認,波形信號的設置必須“確定”后才有效;

“←”:刪除已輸入信號頻率數字的最后一位,用于修改設置的頻率;

“清零”:將頻率數字快速全部清零;

“↑”:步進增大控制;

“↓”:步進減小控制。

設定頻率輸出范圍為1 kHz~10 MHz,頻率步進為50 Hz。系統輸出采用8個LED數碼管,以掃描方式顯示(單位為Hz)頻率數字。根據DDS原理,以步進值50Hz作為頻率控制字1,那么最大值10 MHz對應的頻率控制字為200 000,用18位二進制數值就可以表示(218》200 000)。從抽樣值恢復出原波形數據,理論上每個周期波形數據至少抽取2個點,考慮到實際應用時受頻率損耗、線間串擾等因素的限制,該設計采用22 b的頻率控制字和相位累加器,4 Kb的8位波形ROM表,取相位累加器輸出的高12 b尋址波形數據,三種波形按幅值/相位對應關系分別存儲782個數據。故各波形數據單位周期有800 768(782×210)個相位狀態,完全滿足任一波形在單位周期內取4個幅值點的要求,可保證即使輸出最大頻率的波形仍能達到較好的效果。波形選擇功能由兩位開關組合實現,共有四種狀態,其中三組用來表征不同的波型,另一組留作擴展波形用。

3.2 D/A轉換單元

數/模轉換單元是繼波形數據產生單元之后,將數字量形式的波形幅值轉換成所要求的合成頻率的模擬量形式信號。DAC輸出信號實際上是階梯模擬信號,需在數/模轉換后利用低通濾波器對波形進行平滑處理。在此,采用ADI公司生產的單片雙8位CMOS乘法數/模轉換器AD7528,線性度達到1/2,轉換時間達到納秒級,可以很準確地進行10 MHz信號的量化運算。

3.3 濾波處理單元

濾波器是一種能通過有用頻率信號而同時抑制(或衰減)無用頻率信號的電子裝置。由于運算放大器具有近似理想的特性,且可以省去電感,得到接近理論預測的頻率響應特性。構成有源濾波電路后還具有一定的電壓放大和緩沖作用,并能減小體積。綜合考慮,系統采用運算放大器SL560構成二階低通濾波器。

4 系統功能仿真和驗證分析

4.1 頻率控制字生成模塊仿真與分析

頻率控制字的生成直接影響著波形數據的尋址,該模塊負責快速記錄并實時顯示輸入的頻率數字,準確計算得到相應的頻率控制字。系統鍵盤為高速動態掃描(頻率為200Hz),采用狀態機設計,設置了按鍵去抖動功能。在FPGA開發平臺對該模塊進行功能驗證,整體無誤操作產生,幾乎沒有時滯效應,按鍵的防抖動效果也良好,達到了預期的目的。

4.2 相位累加器模塊仿真與分析

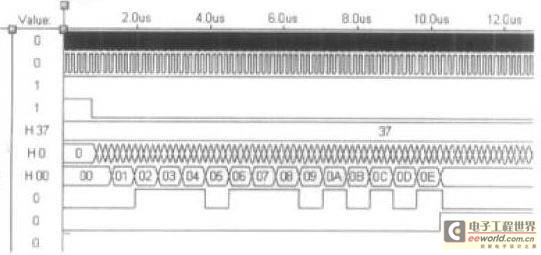

相位累加器用于實現相位累加,并存儲其累加結果。當前,相位累加器的值和時鐘周期到來后的相位累加器的值相差k(k為頻率控制字)。該模塊的仿真波形如圖4所示。

4.3 實驗波形觀測與誤差分析

信號發生器功能驗證無誤,用示波器觀測實驗波形如圖5所示。

檢測輸入頻率為0~10 MHz時,波形形狀均良好,未出現明顯失真。計算理論誤差為0.095%,在實測中發現,波形數字的誤差相對很小,不足0.1 %。由于濾波整形電路存在高頻耦合通路,產生線間串擾,對濾波效果形成了不利影響,因此濾波器設計必須滿足頻帶寬,截止特性好,抗干擾性強等特性。

5 結 語

介紹了以直接數字頻率合成技術(DDS)為基礎的波形信號發生器工作原理和設計過程,并在FPGA實驗平臺上設計實現了滿足各功能指標的信號發生器。系統硬件除需外加濾波整形電路外,其余部分均可在FPGA開發實驗系統KH-310上集成開發,系統軟件可在Quartus下編寫代碼,實現數據信息處理和控制操作等功能。整體開發環境成熟,應用工具齊全,隨著FPGA性價比的不斷提高,基于FPGA平臺開發信號發生器將逐步走向標準化、規模化和產品化。

現代電子和通信技術的發展,對信號發生器提出了更高、更嚴格的要求。除了對信號頻率范圍、帶寬和頻率分辨率的嚴格限制外,對信號的波型及調制特性等也有著苛刻的規定。研究和開發具有更高性價比的信號發生器將是當前和今后一段時間內亟需解決的課題。這里旨在建立一種基于FPGA的簡單數字信號發生器設計方法。若能充分利用FPGA強大的數據運算處理能力以及編程靈活、運行速率快等優點,合理整合IP核資源和SoPC技術,簡化設計結構,一定可以設計出功能多樣、性能更加出色的信號發生器。

二、基于FPGA的信號發生器設計

以FPGA 芯片為載體, 通過QuartusII 的LPM_ROM 模塊和VHDL 語言為核心設計一個多功能信號發生器,根據輸入信號的選擇可以輸出遞增鋸齒波、遞減鋸齒波、三角波、階梯波和方波等5 種信號,通過QuartusII 軟件進行波形仿真、定時分析,仿真正確后,利用實驗板提供的資源,下載到芯片中實現預定功能。

信號發生器又稱為波形發生器, 是一種常用的信號源,廣泛應用于電子電路、通信、控制和教學實驗等領域。它是科研及工程實踐中最重要的儀器之一, 以往多用硬件組成,系統結構比較復雜,可維護性和可操作性不佳。隨著計算機技術的發展,信號發生器的設計制作越來越多的是用計算機技術,種類繁多,價格、性能差異很大。用FPGA 或CPLD 來實現,它的優點是可以進行功能仿真,而且FPGA 和CPLD 的片內資源豐富,設計的流程簡單。用FPGA 所構成的系統來產生波形信號,這個系統既能和主機系統相連,用相應的上層軟件展示波形信號, 又方便程序的編寫, 而且還有A/D0809接口可以產生模擬信號的輸出和外面的示波器相連。

1 正弦信號發生器的LPM 定制

正弦信號發生器由計數器或地址發生器(6 位)、正弦信號數據ROM (6 位地址線,8 位數據線, 含有64 個8 位數據, 一個周期)、原理圖頂層設計和8 位D/A ( 實驗中用DAC0832 代替)。

其框圖如圖1 所示。其中信號產生模塊將產生所需的各種信號,這些信號的產生可以有多種方式,如用計數器直接產生信號輸出,或者用計數器產生存儲器的地址,在存儲器中存放信號輸出的數據。信號發生器的控制模塊可以用數據選擇器實現, 用8 選1 數據選擇器實現對5 種信號的選擇。

圖1 信號發生器結構框圖

最后將波形數據送入D/A 轉換器,將數字信號轉換為模擬信號輸出。用示波器測試D/A 轉換器的輸出,可以觀測到5 種信號的輸出。

1.1 定制初始化數據文件

QuartusII 能接受的LPM_ROM 模塊中的初始化數據文件的格式有兩種:。mif 格式文件和。hex 格式文件。實際應用中只要使用其中一種格式的文件即可。下面采用。mif 格式文件,調出產生ROM 數據文件大小的選擇窗。根據64 點8 位正弦數據的情況,可選ROM 的數據數Number 為64,數據寬Word size 取8 位。單擊OK 按鈕,將出現圖2 所示的空的。mif數據表格,表格中的數據格式可通過鼠標右鍵單擊窗口邊緣的地址數據彈出的窗口選擇。

圖2 .mif 數據表格

將波形數據填入mif 文件表中也可以使用QuartusII 以外的編輯器設計MIF 文件,其格式如下:

#include 《STdio.h》

#include “math.h”

main()

{int i;float s;

for (i=0;i《1024; i++)

{ s = sin(atan(1)*8*i/1024);

printf(“%d : %d;\n”,i,(int)((s+1)*1023/2)); }}

把上述程序編譯成程序后, 可在DOS 命令行下執行命令:

romgen 》 sin_ rom. mif;

1.2 定制LPM 元件

打開Mega Wizard Plug_In Manager 初始對話框, 選擇Create a new custom… 項。單擊Next 按鈕后,選擇Storage 項下的LPM_ROM, 再選擇ACEX1K 器件和VHDL 語言方式;最后輸入ROM 文件存放的路徑和文件名:F:\sing_gnt\data_rom (定制的ROM 元件文件名),單擊Next 按鈕,選擇ROM 控制線、地址線和數據線。這里選擇地址線位寬和ROM 中數據數分別為6 和64; 選擇地址鎖存控制信號inclock。

對于地址信號發生器的設計。方法一:用VHDL 語言設計6 位計數器,產生其元件符號;方法二:仍采用LPM 定制的方法。

1.3 完成頂層設計

按圖3 畫出頂層原理圖,然后進行編譯,波形仿真如圖4所示。

圖3 簡易正弦信號發生器頂層電路設計

圖4 當前工程仿真波形輸出

對當前設計通過執行Quartus II 的命令Create ∠ Update/ Create Symbol Files for Current File,可以為設計電路建立一個元件符號,以便被頂層設計多功能信號發生器所調用。

2 其他信號部分原程序

其他各信號發生器可參照正弦信號發生器的設計方法設計或直接采用VHDL 硬件描述語言進行設計。

LIBRARY IEEE;--遞增鋸齒波的設計

USE IEEE.STD LOGIC 1164.ALL;

USE IEEE.STD LOGIC UNSIGNED.ALL;

ENTITY signal2 IS --遞增鋸齒波signal1

PORT(clk,reset:IN std_logic;--復位信號reset, 時鐘信號clk

q:OUT std_logic_vector (7 DOWNTO 0));--輸出信號q

END signal2;

ARCHITECTURE b OF signal2 IS

BEGIN

PROCESS(clk,reset)

VARIABLE tmp:std_logic_vector(7 DOWNTO 0);

BEGIN

IF reset=‘0’ THEN

tmp:=“00000000”;

ELSIT rising_ege(clk)THEN

IF tmp=“11111111”THEN

tmp:=“00000000”;

ELSE

tmp:=tmp+1; --遞增信號的變化

END IF;

END IF;

q《=tmp:

END PROCESS;

END b;

LIBRARY IEEE;--方波的設計

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity signal5 is --方波signal5

PORT(clk,reset:in std_logic; --復位信號reset,時鐘信號clk

q:out std_logic_vector (7 DOWNTO 0)); --輸出信號q,8 位數字信號

END signal5;

ARCHITEECTURE a OF signal5 IS

SIGNAL; a:std_logic;

BEGIN

PROCESS(clk,reset)

YARIABLE tmp:std_logic_vector(7 downto 0);

BEQIN

IF reset=‘0’ then

a《=‘0’;

elsif rising_edge(clk)THEN

IF tmp=“11111111” THEN

tmp:=“00000000”;

ELSE

tmp:=tmp+1;

END IF;

if tmp《=“10000000” then

a《=‘1’;

else

a《=‘0’;

END IF;

END IF;

END PROCESS;

PROCESS(clk,a)

BEGIN

IF rising_edge(clk)THEN

IF a=‘1’ THEN

q《=“11111111”;

ELSE

q《=“00000000”;

END IF;

END IF;

END PROCESS;

END a;

3 頂層電路的設計

將上述6 個模塊生成符號,供頂層電路調用。這些模塊分別是:遞減鋸齒波信號產生模塊signall、遞增鋸齒波信號產生模塊signal2、三角波信號產生模塊signal3、階梯波信號產生模塊signal4、方波信號產生模塊signal5 和數據選擇器mux51。頂層電路的連接如圖5 所示。

圖5 信號發生器頂層電路

4 D/A 轉換器的連接

選擇一個D/A 轉換器,將數據選擇器的輸出與D/A 轉換器的輸入端連接。D/A 轉換器的可選范圍很寬,這里以常用的DAC0832 為例。DAC0832 的連接電路如圖6 所示。

圖6 DAC0832 的連接電路

5 實現與測試

信號發生器頂層電路的仿真波形如圖7 所示,這里只就輸入選擇信號等于5 時的情況進行仿真,此時輸出波形是方波,輸出的數字信號為周期性的全0 或全1。

圖7 信號發生器頂層電路的仿真波形

信號發生器的底層電路模塊也可以分別進行仿真,例如對階梯波信號產生模塊signal4 進行仿真,仿真波形如圖8 所示,輸出的數字信號為階梯狀變化。

圖8 階梯波信號產生模塊signal4 的仿真波形

6 結束語

硬件電路設計主要是設計相關模塊的設計思想的可視化,是相關模塊的電路圖的匯總和其相關仿真波形的集錦,該部分條理清晰,思路明確,從中我們可以清晰地看到該設計方案的具體模塊和整個設計的原理結構實圖;程序設計這一部分主要闡述該設計的設計方法與設計思想,進一步從軟件設計上揭示設計構思,主要包含了整個設計所用到的模塊的硬件描述語言的設計, 本文設計思路清晰,通過QuartusII 軟件進行波形仿真成功,特別是正弦信號發生器的LPM 定制對于編程不是特別強的人員提供另一種途徑來實現,加深理解EDA 的層次設計思想,很好的把握住了教學的改革方向,更好的鍛煉了學生理論聯系實踐的能力。

三、基于FPGA及VHDL的LED點陣漢字滾動顯示設計方案

漢字滾動顯示器的傳統設計方法是用單片機來控制的,雖然單片機方案具有價格低廉,程序編程靈活等特點,但由于單片機硬件資源的限制,未來對設計的變更和升級,總是要付出較多研發經費和較長投放市場周期的代價,甚至有可能需要重新設計。況且,在以顯示為主的系統中,單片機的運算和控制等主要功能的利用率很低,單片機的優勢得不到發揮,相當于很大的資源浪費。

采用EDA技術的自頂向下的模塊化設計方法,借助相關開發軟件,例如QualtusⅡ軟件,將硬件描述語言——VHDL程序固化于具有豐富I/O口、內部邏輯和連線資源的FPGA(現場可編程門陣列)中。該技術具有系統設計效率高、集成度好、保密性強、易于修改、易于實現等優點,成為當今數字系統設計主流技術。此方式所制作的LED點陣控制器,由于是純硬件行為,具有速度快、可靠性高、抗干擾能力強、開發周期短等顯著優點。

1 EDA點陣顯示漢字原理

以8×8的LED點陣為例,8×8的LED點陣是由64個發光二極管按矩陣形式排列而成,每一行上的發光管有一個公共的陽極(或陰極),每一列上的發光管有一個公共的陰極(或陽極),一般按動態掃描方式顯示漢字或圖形。掃描分為點掃描、行掃描和列掃描三種方式。行掃描需要按行抽取字型碼,列掃描則需要按列抽取字型碼。為滿足視覺暫留要求,若使用點掃描方式,其掃描頻率必須大于16×64=1 024Hz,周期小于1ms。若使用行或列掃描,則頻率必須大于16×8=128Hz,周期小于7.8ms。由于所用實驗板上提供有1 kHz的時鐘,本例設計中利用該時鐘進行掃描,使每行掃描時間為1 ms,實驗結果顯示亮度合適。現以行掃描為例簡單說明動態掃描顯示的原理。圖1給出漢字“熱”在點陣為列共陽時的行字模。工作時先將要掃描行的點陣字模從各列上輸出,再讓譯碼器選中(掃描)該行,使本行得以顯示,接著再送下一行數據,再使下一行有效,直到8行全被掃描一遍。至此,一幅完整的文字信息就顯現出來,然后再反復掃描這8行直至顯示新的信息。以下設計采用行掃描方式實現滾動顯示。

2 硬件原理圖

整個電路由五大部分組成:時鐘計數模塊GEL_CLK,存儲漢字字模的ROM模塊ROMZI,數據分配器模塊MUX,移位模塊YW及顯示模塊XIANSH-I。時鐘計數模塊用于產生整個電路所需要的時鐘及其對時鐘的計數值,例如:移位時鐘CLK YW,移位計數器CNT YW,字計數器CNT WORD,顯示掃描計數器CNT SM。ROMZI模塊是由QualtusⅡ中的LPM 1PORT ROM定制成,用來存儲8個待顯示的漢字。MUX模塊用于在掃描時鐘及掃描計數器的作用下,從ROM中讀出一個漢字的8個行字模信息,送給移位模塊YW,YW模塊在移位時鐘及移位計數器作用下,根據SELECT信號選擇對讀出的字模信息,進行相應的移位(左移、右移、上移、下移)后,最后送顯示模塊DISP驅動LED點陣顯示漢字。原理圖如圖2所示。

3 模塊設計及時序仿真

3.1 時鐘計數產生模塊

時鐘計數產生模塊由1 kHz的輸人時鐘為基準,進行17位的循環計數CNT[16..O]。該時鐘,既是動態掃描顯示的時鐘,也是從ROM中取一個字8個字模的時鐘,對之進行的3位循環計數作為掃描顯示計數器和取一個字的字型碼計數器。CNT[16..O]中的CNT[9]是對該時鐘的1 024分頻,將其作為移位時鐘CNT_YW,周期約為l s。CNT[13…lO]作為4位的移位計數器,是對移位時鐘CLK_YW的計數,也是對移位位數的統計。16個狀態使一個漢字逐列移進點陣,又逐列移出。每經過16個移位時鐘,將會顯示完一個漢字。CNT[16..14]作為3位的取字計數器。

CNT[16…14]&CNT[2..O]作為ROM地址發生器。

3.2 ROMZI模塊

利用LPM參數化模塊庫中單口ROM,利用QualtusⅡ中的MegaWizard Plug-In Manager定制而成,定制前首先要制作LPM ROM初始化文件,其中存儲待顯示漢字的字模數據,然后按照LPM MegaWizardPlug-In Manager的向導提示,結合設計要求進行定制。

圖3為所定制ROM中的初始化漢字“元旦生日開心快樂”的字型碼。數據分配模塊MUX要求能在8個時鐘作用下,從ROM中讀出一行(一個漢字的8個字型碼)分別送到數據分配器中的WLl~WL8輸出端。圖4為數據分配模塊在掃描時鐘作用下讀取的字模數據,比較圖3和圖4可知,仿真結果正確,能滿足題目要求。

3.3 移位模塊YW

移位模塊YW是整個設計的核心,行掃描實現左移,是通過每來一個移位時鐘,將每一行的字模按位左移一位,掃描時鐘到來時送出移位后的新字模。通過8次移位,可將一個漢字移出點陣平面,按類似的道理,也可以將一個漢字經8次移位后移進點陣平面。本例(圖2)中,CNT YW為移位時鐘的計數值,以WLl~WL8為欲顯示漢字的原始字模,L10~L80為移位后從列上送出的8行顯示字模信息,LLl~LL8為8個原始字模信息未送出位的暫存信號。設計中需要16個移位時鐘,通過前8個時鐘將WLl~WL8字模移進LED點陣平面,再經后8個時鐘,將漢字又一位一位地移出。 移位設計參考文獻中有關移位寄存器的設計,分計數值為“0000“和非”0000“兩部分處理,對第一行字模的處理為:

其他行可按相同方法處理,具體參見如下的程序:

右移處理方法與上面左移相反,如對第一行可按如下方法處理:

上移時的部分程序按以下思路編制:L10~L70在CNT_YW為初態“0000”時,各信號均賦值X“00”,非初態時,均進行上移一位。即:L10《=L20;L20《=L30;…;L60《=L70;L70《=L80;對于L80,在漢字移進LED過程中即前8個狀態各移進一個新行,在移出LED即后8個狀態時,都補進X“00”。程序如下:

下移程序可按相反思路去編。

3.4 顯示模塊DISP設計

顯示模塊DISP是以CNT_SM為掃描計數器,是對1kHz進行三位循環計數,由前述的時鐘計數產生模塊產生,WLl~WL8為待送出顯示的8個8位字型碼,由前述的移位模塊YW提供;SW[7..O]為行掃描輸出信號,連接至點陣的8個行;DATA[7..0]為行掃描時對應的列輸出字型碼,對外連至點陣的8列。該模塊參考文獻中數碼管動態顯示程序進行設計如下:

4 硬件實現

上述各模塊分別在QualtusⅡ中通過了仿真驗證,最后對整體設計進行了硬件驗證。將設計載入KH31001開發板的Cyclone工系列EPlC6Q-240C8FPGA器件中,實驗證明漢字滾動顯示掃描情況均正常,能夠按照預想進行移位顯示,這說明。FPGA的內核硬件工作良好,可以正確地實現所要求的設計功能。

5 系統擴展

本文是針對8×8點陣設計,故每次取8個字形碼,如果是16×16點陣,將RONZI中存儲的字形碼改為16位,數據線改為16位,一個漢字需要16個16位的字形碼,數據分配模塊MUX、移位模塊YW、顯示模塊DISP,均要將輸入輸出數據中的原來的8位改成相應的16位。掃描及取字型碼計數器CNT_SM應改為CNT計數器的低4位。一個16×16點陣漢字的移進移出共需32個狀態。由5位的計數器提供。如用CNT[16..0]中的14~10位作為該計數器,這可在時鐘計數器產生單元CLK_GE中應做相應修改,字計數器CNT WORD按照每取16個字進行加1統計。顯示DISP部分的譯碼器要由3-8譯碼改為4-16譯碼。顯示的漢字信息越多,ROM的地址線位數越多,字計數器CNT_WORD應在時鐘計數器產生單元GE_CLK中,將相應的計數器位數擴展,由CNT計數器的最高位到位15來承擔。若還是8個漢字,計數器應為CNT[17..O],CNT[17..15]為字計數器;若為16個漢字,計數器應為CNT[18..O],CNT[18..15]為字計數器,…,依次類推。

6 結語

本文在KH31001開發板上實現了基于Altera公司的Cyclone I系列FPGA器件EPlC6Q240C8硬件及VHDL硬件描述語言設計的LED點陣漢字滾動顯示,能在8×8點陣上滾動顯示“元旦生日開心快樂”8個漢字。文中從LED點陣顯示漢字的原理闡述出發,給出了點陣漢字滾動顯示控制器的原理圖,部分模塊的VHDL源程序及時序仿真圖,并能由按鍵選擇其滾動方式:左移、右移、上移、下移等,給出了系統擴展成16×16點陣漢字滾動的改動思路。從文中描述的系統擴展方案中看出,當系統顯示字符個數變化時,只需對控制邏輯和連接關系做適當的修改,再將修改完成的程序下載到器件即可,顯然,系統的維護和修改是極其方便和容易的,本文對同類設計也具有一定的參考價值。

四、數字控制振蕩器(NCO)的FPGA實現

NCO(N umerically Controlled Oscillator)是用于產生一個理想的、數字可控的正弦或余弦波的數字控制式振蕩器,其實現方法有實時計算法和查表法等多種。實時計算法的正弦波樣本以實時計算產生,該方法因其計算需要耗費很多時間,因而只能產生較低頻率的正弦波,而且存在計算精度與計算時間的矛盾。由于在需要產生高速的正交信號時,實時計算法將無法實現。因此,在實際應用中一般采用最有效、最簡單的查表法,即事先根據各個NCO正弦波的相位計算好相位的正弦值,并按相位作為地址信息存儲該相位的正弦值數據。

1 NCO的基本原理

在通過相位累加產生地址信息時,通常需要輸出當前時刻的相位值所對應的正弦值,即以參考頻率源對相位進行等可控間隔采樣。眾所周知,理想的正弦波信號S(t)可以表示成:

![]()

式(1)說明,信號s(t)在振幅A和初相φ確定之后,其頻率可以由相位來唯一確定。即:

![]()

NCO就是利用式(2)中φ(t)與時間t成線性關系的原理來進行頻率合成的,也就是說,在時間t=△t間隔內,正弦信號的相位增量△φ與正弦信號的頻率f可構成一一對應關系,也就是說,對式(2)兩端進行微分后有:

![]()

。

由上面的討論可知:

![]()

其中,△θ為一個采樣間隔△t之間的相位增量,采樣周期

![]()

。故式(3)可改寫為:

![]()

由式(4)可知,如果可以控制△θ,就可以控制不同的頻率輸出。由于△θ受頻率控制字FCW的控制,即:

![]()

,所以,改變FCW就可以得到不同的輸出頻率f0,然后經代換處理可得如下方程:

式(5)和式(6)中的L為相位累加器的位數。根據Nyquist準則,允許輸出的頻率最高為FCLK/2,即

![]()

。但在實際工程中,由于受到低通濾波器的限制,一般輸出的頻率

![]()

。

2 NCO的性能指標

NCO的性能指標包括信號頻率分辨率、信噪比(SNR)、無雜散動態范圍(SFDR)和輸出的信號正交性。這些性能指標取決于NCO的數據位數。NCO的數據位數包括用于表示相位數據的位數n和表示相位的正弦值數據的位數nb,二者之間存在nb取決于n的關系,且前者必須能夠表示相位變化時其相位正弦值變化的最小值和最大值。而這又分為兩種情況:

第一種情況是相位最小變化值的正弦值最小變化發生在π/2-△φ~π/2,π/2~π/2+△φ,3π/2-△φ~3π/2,3π/2~3π/2+△φ,同時其相位的取值是在0~2π間且等間隔地分為2n爪取值點,因此,由正弦波的特性可知:只需要討論相位在π/2-△φ與π/2取值點的正弦值之差:

第二種情況是相位最小變化值的正弦值的最大變化發生在0~△φ,π-△φ~π,π~π+△φ,2π-△φ~2π取值點處。該情況可以通過類似于第一種情況的推導方法得到:

設計時可以根據式(9)和式(10)較好地取值n和nb,以避免相位的分辨率發生鈍化,并很好地達到設計要求。

NCO的噪聲是因為存在正弦值的量化誤差而引入的,且量化誤差由表示正弦值的位數決定,其近似關系為:

式中,B是作為尋址ROM的地址的舍位位數,n是相位位數。NCO的另一個性能參數是頻率分辨率△f,該參數取決于相位位數,其關系式為:

![]()

3 NCO在FPGA中的實現

NCO的查找表是一個正弦值表,該表的正弦值是按照相位作為存儲地址來進行存儲的,而且一般以相位遞增的方式存儲。利用正弦波的奇偶對稱性,可以把2π相位分成4等份,然后利用各等份之間的對稱性來實現地址信息的映射,通常只存儲[0,π/2]象限內的幅度碼。

相位累加器可完成相位累加,即每來1個時鐘就累加1次φ=φ+△φ,且采用流水線方式工作。本設計采用QUARTUS II中IP核自帶的一種32位累加器來實現相位的累加。

邏輯轉換完成后,可采用小表結構功能塊把相位累加器產生的最高2位信號轉換為地址控制信號和象限轉換控制信號。其中地址控制信號是根據最高兩位信號來控制地址從0開始遞增方式產生還是從2L開始以遞減方式產生。

正弦表是每來一個時鐘輸出一個大于零的正弦值數據,這些數據可作為象限變換器的輸入,由象限變換器完成數據的象限變換。其轉換原則是:象限控制信號根據正弦信號的對稱性把查表得到的數據轉換為正負數據,并對于正弦信號的1、2象限數據進行加零操作,而對3、4象限的數據進行求補運算。余弦數據也同樣,在1、4象限對數據進行加零操作,2、3象限數據進行求補運算。

4 仿真結果

利用上述小表結構實現的NCO可以輸出多種頻率信號并減少資源消耗,影響系統輸出頻率的因素主要是工作頻率和器件性能。

圖1所示是整個NCO在QUARTUS II中的仿真波形圖。

在圖1所示的波形圖中,CLK是時鐘輸入頻率(為65.6 MHz),CLR為系統復位信號,相位累加器的位數L為32位,輸出信號幅度位數為12位(包括符號位),相位寬度為12位,這樣,由式(5)便可得到頻率控制字FCW為269591793,圖1中的COS_OUT與SIN_OUT是系統輸出信號,頻率為4.08 MHz。

由式(11)、(12)、(13)可得,此系統的信噪比和SFDR分別為74 dB和84 dB。

圖2所示是將波形文件中的正弦余弦數據讀入MATLAB中所顯示出來的波形。

5 結束語

本文通過分析數控振蕩器的實現原理和性能,給出了通過FPGA來實現NCO的具體方法,同時通過QUARTUSⅡ中的仿真驗證了本設計的正確性。結果證明,用該方法設計的NCO可以輸出多種頻率的信號,同時也可以減少資源消耗。

?

?

電子發燒友App

電子發燒友App

評論