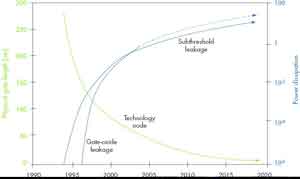

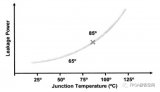

電子發燒友網核心提示:隨著工藝尺寸的減小,數字邏輯電路的漏電流成為當前FPGA面臨的主要挑戰。靜態功耗增大的主要原因是各種漏電流源的增加。圖1所示為隨著更小邏輯門長度的技術實現,這些漏電流源是怎樣隨之增加的。此外,如果不采取專門的功耗措施,較大的邏輯電容和較高的開關頻率也會導致動態功耗增大。

功耗由靜態和動態功耗組成。靜態功耗是采用可編程目標文件(.pof)對FPGA進行設置,但時鐘還沒有工作時消耗的功率。數字和模擬邏輯都存在靜態功耗。在模擬系統中,靜態功耗主要來自模擬電路不同接口配置帶來的靜態電流。

圖1 在更小的工藝尺寸上,靜態功耗顯著增大

動態功耗是器件工作時由于信號觸發和容性負載充放電所帶來的功耗,影響動態功耗的主要因素是電容充電、供電電壓和時鐘頻率等。按照摩爾定律,小工藝尺寸降低了電容和電壓,從而降低了動態功耗。而難點在于小工藝尺寸上實現了更多的電路,提高了最大時鐘頻率。隨著工藝節點的減小,相同電路的功耗在降低,但是FPGA容量在不斷加倍,最大時鐘頻率不斷提高。

體系結構和工藝技術的功耗創新

FPGA可以采用創新的內核、I/O和收發器體系結構以及最新的工藝技術和電路技術來解決這些功耗難題。

1 可編程功耗技術

FPGA內核主要包括邏輯、存儲器和數字信號處理(DSP)模塊。在Virtex-5 FPGA等標準FPGA中,所有邏輯模塊都設計運行在一個速率上——最大速率,導致非常大的功耗。

Altera公司的工程師分析了71個設計的基準測試結果,估算一個設計一般需要多少高速邏輯。他們對設計進行編譯,在FPGA架構上實現所能達到的最佳性能。在這些設計中,所需要的高速邏輯大概平均占20%。

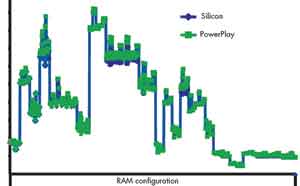

圖2所示為一個典型的余度直方圖,大部分通路(左側)都有一定的余度,只有少量關鍵通路(右側)需要性能最好的邏輯以達到時序要求。

圖2 余度直方圖顯示少量電路沒有或者很少有余度

利用這一事實——設計中的大部分電路都有一定的余度,不需要將所有邏輯置于高性能狀態。以Stratix IV FPGA為例,它由邏輯陣列模塊(LAB)、TriMatrix存儲器和DSP模塊構成,利用可編程功耗技術將少量的關鍵時序邏輯模塊設置為高速模式。時序不重要的邏輯模塊設置為低功耗模式,能夠大大降低低功耗邏輯的泄漏功耗。而且,可編程功耗技術將沒有使用的邏輯、TriMatrix存儲器以及DSP模塊設置為低功耗模式,進一步降低了功耗。

在任何設計中,Quartus II軟件能夠自動確定設計中每一通路的余量,通過調整晶體管反向偏置電壓,把晶體管,同時把邏輯模塊設置為合適的模式——高性能或者低功耗。例如,將Stratix IV FPGA內核的n-MOS晶體管設置為這兩種模式。

● 低功耗模式,Quartus II軟件減小反向偏置電壓,使得晶體管很難接通。這降低了時序不重要電路的亞閾值漏電流和不需要的靜態功耗。

● 高性能模式,Quartus II軟件增大反向偏置電壓,在幾個關鍵時序通路上的晶體管更容易接通,以滿足設計中規定的時序約束要求,提高性能。

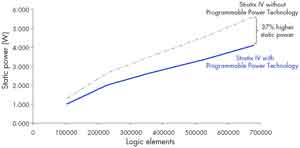

采用同樣的方法也能將p-MOS晶體管設置為合適的模式,從而設置LAB、TriMatrix存儲器和DSP模塊為高性能或者低功耗模式。這樣,通過改變晶體管的電氣特性,Stratix IV FPGA可編程功耗技術以高速邏輯和低功耗邏輯的最佳組合,實現了最好的性能和最低的功耗。例如,圖3所示的Stratix IV EP4SE680 FPGA在85℃時的典型設計,和沒有采用可編程功耗技術時相比,靜態功耗降低了37%。

圖3 可編程功耗技術降低了靜態功耗

我們可以精確地控制一個設計達到其性能要求而需要的高速邏輯數量。在每一個邏輯塊基礎上控制高速和低功耗邏輯的設置(每個邏輯塊包括兩個LAB,或者一個LAB和DSP模塊,或者一個TriMatrix存儲器,都含有相關的走線)。例如,在Stratix IV FPGA中,可以分別對5000多個邏輯塊進行控制,設置為高速或者低功耗模式,把設計功耗降到最低。Quartus II開發軟件能夠將邏輯塊設置為高速或者低功耗模式,自動對設計進行優化,無須用戶的干預。

Quartus II軟件每次針對Stratix III FPGA進行設計編譯時,自動對設計進行優化,達到規定的時序約束,同時實現最低功耗。得到的編程文件被裝入FPGA,包括將每個邏輯塊設置為高速或者低功耗配置的信息。在Quartus II軟件中完全可以看到邏輯塊高速或者低功耗模式的最終設置。

2 MultiTrack互連

Stratix系列器件還采用了MultiTrack互聯來提高性能,降低擁塞和功耗。MultiTrack互聯提供不同LAB之間的連接,可以采用一個LAB到另一個LAB之間的“跳轉”數量來對其性能進行衡量。由于增加互連跳轉數量會增大電容,因此,跳轉數量越少,就可以采用越少的高速邏輯來達到性能要求。

ALM和MultiTrack體系結構相結合后,能夠以更少的布線連接更多的邏輯,從而提高了性能,降低了功耗。

3 分級時鐘

分級時鐘可以在LAB層面上來控制每一時鐘網絡的傳播。作為Quartus II軟件中邏輯優化的一部分,通用時鐘邏輯被劃入LAB中。只有在邏輯使用時鐘時,才啟用該時鐘。關斷所有其他時鐘信號,以降低功耗。

4 DDR3和動態片內匹配

以Stratix IV FPGA為例,其I/O創新技術包括I/O中直接內置讀/寫調平功能,更迅速方便地與1067Mb/s533MHz) DDR3 DIMM進行接口。從1.8V工作的DDR2過渡到1.5V工作的DDR3,使I/O靜態功耗降低了30%。

為進一步降低I/O靜態功耗,可在數據傳送期間動態接通和關斷串聯匹配(RS)及并聯匹配(RT),這一功能被稱為動態片內匹配(DOCT)。在寫周期,RS接通,RT關斷,以匹配線路阻抗,而在讀周期,RS關斷,RT接通,實現與總線的遠端匹配。在一個典型72位DIMM上,和使用DDR2但不具有DOCT的標準FPGA相比,Stratix IV FPGA在1067Mb/s時I/O靜態功耗降低了65% (1.9W)。

5 內置硬核IP和收發器技術

以Stratix IV FPGA為例,它為各種×1、×4、×8 PCI Express Gen1和Gen2應用提供一系列完整的PCI-SIG兼容FPGA解決方案。Stratix IV FPGA新增特性提供4個PCI Express硬核知識產權(IP)模塊,嵌有完整的PCI Express協議堆棧(端點和根端口)。這包括收發器模塊、PHY MAC、數據鏈路層和協議層。

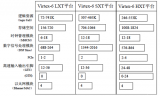

和軟核IP相比,Stratix IV FGPA中的硬核IP不但節省了邏輯和嵌入式存儲器資源,縮短了設計和編譯時間,而且大大降低了功耗。表1為Stratix IV FPGA中PCI Express硬核IP內核Gen2的功耗。

40nm工藝的電路技術

40nm工藝要比以前包括65nm節點和最近的45nm節點在內的工藝技術有明顯優勢。最引人注目的優勢之一是其更高的集成度,半導體生產商可以在更小的物理空間中實現更強的功能。和65nm工藝相比,45nm工藝密度提高了1倍,而40nm工藝密度達到了2.35倍。

半導體行業一直在不斷邁向更小的工藝節點,在設備、工藝技術、設計工具和電路技術上進行大量投入,以解決出現的各種問題。整個行業普遍面臨的挑戰是小工藝尺寸上越來越大的泄漏功率問題,40nm工藝節點(以及以前的節點)采用了很多技術手段來管理泄漏功率,進一步提高性能,或者保持性能不變。

1 全銅布線

銅替代鋁之后,減小了電氣損耗和功率損耗,從而提升了性能。以Altera為例,該公司在150nm工藝節點開始采用全銅金屬進行片內布線,在所有130nm、90nm、65nm和40nm產品中都采用了全銅布線。

2 低k絕緣

絕緣材料實現了金屬層之間的隔離,支持多布線層。采用低k絕緣后,降低了布線層之間的電容,顯著提高了性能,降低了功耗。

3 多閾值晶體管

晶體管電壓閾值影響晶體管的性能和泄漏功率。Altera對性能要求高的高速晶體管采用低閾值電壓,對性能要求不高的慢速低泄漏晶體管采用高閾值電壓。

4 可變門長度晶體管

晶體管的邏輯門長度影響其速率和亞閾值泄漏。當晶體管的長度接近45nm工藝的最小門長度時,亞閾值漏電流會顯著增加。在性能要求不高的電路中,可使用長度較長的邏輯門以降低漏電流。對于性能非常關鍵的電路,Altera使用長度較短的邏輯門來提高性能。Altera在90nm、65nm和40nm Stratix系列器件中采用了可變門長度晶體管來降低功耗。

5 三重氧化

邏輯門氧化層的厚度會影響晶體管的性能和漏電流。Stratix IV FPGA在I/O電路和核心邏輯中使用了三個分立的氧化層(三重氧化)。這些核心氧化層中的兩個被用于在低性能晶體管中實現最小泄漏,在高性能晶體管中被用于實現最佳性能。

6 超薄門氧化

三重氧化技術還包括針對高性能晶體管的超薄門氧化技術。這些晶體管即使使用長度較長的邏輯門也可以達到最佳性能,適當的提高柵極導致的漏極泄漏以及柵極直接溝道泄漏,能夠大大降低亞閾值泄漏。

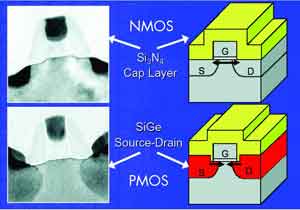

圖4 40nm應變硅技術實現了性能更好的晶體管

7 應變硅

應變硅技術增大了晶體管溝道跨導,從而提高了晶體管的性能,如圖4所示。Stratix III和Stratix IV FPGA的所有晶體管中使用了應變硅技術,以提高FPGA的性能。

Quartus II功耗優化

詳細的設計實施可以提高性能,減小面積,降低功耗。以前,通過布局布線設計流程,寄存器傳送級(RTL)自動在性能和面積上達到均衡。Quartus II PowerPlay優化工具自動在Stratix IV FPGA上繼承了這些節省功耗的特性,進一步降低功耗。

Quartus II軟件的許多自動功耗優化功能對設計人員而言都是透明的,而且還提供Stratix體系結構詳細的優化措施以降低功耗,這些措施如下。

1 分析和綜合優化

● 主要功能模塊變換映射用戶RAM,降低功耗。

● 重新規劃邏輯以降低動態功耗,正確的選擇邏輯輸入,降低高頻觸發網絡的電容。

2 適配器優化

● 降低核心邏輯的面積和連線要求,以降低布線的動態功耗。

● 修改布局以降低時鐘功耗。

● 在對時序不重要的數據信號進行布線時,降低速率以減小功耗。

● 將關鍵通路上的邏輯塊設置為高速模式,所有其他邏輯塊設置為低功耗模式(Stratix III和Stratix IV FPGA)。

功耗估算

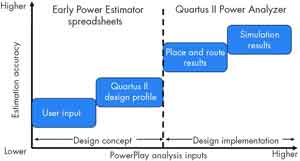

在設計概念構思直到實施的整個過程中,PowerPlay都支持功耗估算,如圖5所示。在設計構思階段,設計人員使用PowerPlay EPE,而在設計實施階段使用PowerPlay功耗分析器。這些工具是精確的FPGA功耗分析工具。

圖5 PowerPlay分析工具——精度和實現

PowerPlay EPE是一種基于表格的分析工具,可以根據器件和封裝選擇、工作條件以及器件使用情況來進行早期功耗估算。EPE具有FPGA內部精確的功能元件模型,但是,由于在RTL設計之前采用EPE,因此,它缺乏很多關鍵信息,如邏輯配置、布局布線等,限制了其精度范圍。然而,用戶還是依靠EPE作為主要的功耗估算工具,在設計早期階段進行功耗估算。

PowerPlay功耗分析器是更精細的功耗分析工具,它使用實際的設計布局布線和邏輯配置,以及仿真波形精確地估算動態功耗。總體上,功耗分析器結合精確的設計信息,其準確度在±15%以內。

圖6 全RAM配置的PowerPlay功耗估算和芯片測量

Quartus II PowerPlay功耗模型與實際的芯片測量結果密切相關。Altera公司使用了8500多個不同的測試配置來測量Stratix系列器件每一組成的功耗。每一配置專門針對FPGA特定配置下的某一電路組成,例如9×9模式下的DSP、×16模式下的M9k存儲器模塊,以及特定邏輯配置下的ALM等。

所采用的測試方法簡單、精確。對特定配置下FPGA中單個模塊進行精確的功耗測量,最好的方法是采用待分析配置狀態測量的模塊實例來配置FPGA。所有其他邏輯和功能模塊配置為低功耗工作模式不被激勵。然后,在所有被測模塊中運行設計好的、能夠重復激勵的模式,產生清晰的功耗參數。得到的芯片功耗主要來自于大量被測模塊,可以從總功耗中提取出多余功耗。得到的功耗除以配置模塊數后,得出該模塊在該模式下的精確功耗,如圖6所示。

結論

雖然邁向尺寸更小的工藝節點實現了摩爾定律預言的密度和性能優勢,但是要在提高性能的同時降低功耗,不但要進行工藝創新,而且也需要在FPGA體系結構上進行創新。可編程功耗技術和支持DOCT的DDR3等獨特的技術使Stratix IV FPGA等高端FPGA盡可能將功耗降到最低,同時不會犧牲新一代設計的性能。

電子發燒友App

電子發燒友App

評論