在今年11月中旬舉辦的“2016年超算大會(huì)上”,FPGA大廠(chǎng)Xilinx發(fā)布了可重配置加速棧(ReconfigurableAcceleration Stack)。配合可重構(gòu)的FPGA,這個(gè)架構(gòu)能解決可重構(gòu)計(jì)算中的編程困難問(wèn)題,并加速可重構(gòu)計(jì)算生態(tài)的建設(shè)。

日前,Amazon云服務(wù)AWS更是基于Xilinx高端Ultrascale+ FPGA推出了使用在云端的FPGA解決方案。眾多巨頭的參與,讓誕生幾十年的可重構(gòu)計(jì)算再度成為業(yè)界關(guān)注的焦點(diǎn)。但是你真的懂得可重構(gòu)計(jì)算嗎?

可重構(gòu)計(jì)算的起源

自從計(jì)算機(jī)誕生以來(lái),科學(xué)家們就意識(shí)到計(jì)算機(jī)架構(gòu)對(duì)于其處理能力有著至關(guān)重要的影響。事實(shí)上,從來(lái)不存在一種對(duì)所有運(yùn)算任務(wù)都是最優(yōu)解的計(jì)算機(jī)架構(gòu)。這是因?yàn)橛?jì)算機(jī)的運(yùn)算單元由芯片構(gòu)成,而在芯片的面積固定的情況下計(jì)算機(jī)架構(gòu)就決定了如何分配芯片的資源。

舉例來(lái)說(shuō),機(jī)器學(xué)習(xí)應(yīng)用(尤其是CNN)會(huì)比較注重并行運(yùn)算,因此最適合的架構(gòu)是能處理并行運(yùn)算的多核架構(gòu),而每個(gè)核的運(yùn)算能力并不需要特別強(qiáng)。另一方面,在一些科學(xué)及工業(yè)運(yùn)算上,計(jì)算是無(wú)法并行執(zhí)行的,于是最適合的架構(gòu)是單核架構(gòu)并把這個(gè)核做到非常強(qiáng)。

根據(jù)數(shù)據(jù)和指令的執(zhí)行方式,60年代著名的計(jì)算機(jī)科學(xué)家Flynn提出了架構(gòu)的分類(lèi)方法,一共有單指令流單數(shù)據(jù)流(SISD),單指令流多數(shù)據(jù)流(SIMD),多指令流單數(shù)據(jù)流(MISD)以及多指令流多數(shù)據(jù)流(MIMD)四種。

?

正是由于對(duì)于不同的任務(wù)有最合適的架構(gòu),計(jì)算機(jī)科學(xué)家們開(kāi)始構(gòu)思如何使用一種靈活的架構(gòu)解決這個(gè)問(wèn)題。可重構(gòu)運(yùn)算(reconfigurable computing)從上世紀(jì)60年代由Gerald Estrin提出,到現(xiàn)在已經(jīng)經(jīng)歷了半個(gè)世紀(jì)。

在Estrin最初的設(shè)想中,可重構(gòu)運(yùn)算包括一個(gè)作為中央控制單元的標(biāo)準(zhǔn)CPU,以及眾多可重構(gòu)的運(yùn)算單元,這些可重構(gòu)運(yùn)算單元由中央CPU控制,在執(zhí)行相應(yīng)任務(wù)(如圖像處理,模式識(shí)別,科學(xué)運(yùn)算等等)時(shí)配置成對(duì)應(yīng)的最優(yōu)架構(gòu)(即硬件編程)。

在理論上這個(gè)構(gòu)想非常成功:2001年,Reiner Hartenstein的論文中提到,即使可重構(gòu)運(yùn)算使用的運(yùn)算單元(FPGA)時(shí)鐘頻率遠(yuǎn)低于當(dāng)時(shí)的CPU,但是可重構(gòu)計(jì)算的綜合運(yùn)算能力卻可以超越CPU數(shù)倍,而功耗也遠(yuǎn)小于CPU。

?

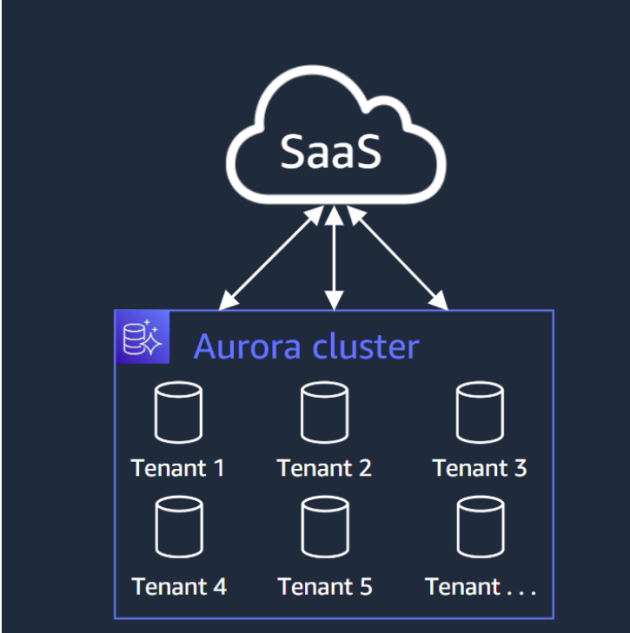

可重構(gòu)計(jì)算的例子(使用FPGA作為可重構(gòu)計(jì)算單元)

然而,可重構(gòu)運(yùn)算在當(dāng)時(shí)并沒(méi)有普及。從可重構(gòu)運(yùn)算提出直到二十一世紀(jì)初的40年正是摩爾定律的黃金時(shí)期,工藝一年半就更新一次,因此架構(gòu)上更新帶來(lái)的性能增強(qiáng)可能還不如工藝更新來(lái)得強(qiáng)。

當(dāng)時(shí)最流行的就是靠摩爾定律狂飆突進(jìn)來(lái)實(shí)現(xiàn)處理器運(yùn)算能力的進(jìn)化,因此與舊架構(gòu)相差很大的可重構(gòu)運(yùn)算并未得到重視:花五年時(shí)間研發(fā)的可重構(gòu)計(jì)算芯片很可能性能還不及依靠摩爾定律提升性能的傳統(tǒng)架構(gòu)CPU。

同時(shí),由摩爾定律帶來(lái)的CPU性能增長(zhǎng)完全可以滿(mǎn)足當(dāng)時(shí)運(yùn)算的需求。因此當(dāng)時(shí)可重構(gòu)運(yùn)算還只是停留在學(xué)術(shù)圈子里的精致理論,業(yè)界推廣的動(dòng)力并不大。

另一個(gè)可重構(gòu)運(yùn)算普及的障礙是使用難度。傳統(tǒng)CPU上編程使用抽象的高級(jí)語(yǔ)言(如C++,Java等等)描述,已經(jīng)有成熟的體系。然而可重構(gòu)計(jì)算需要的硬件編程通常使用硬件描述語(yǔ)言(Verilog,VHDL等等),對(duì)于程序員來(lái)說(shuō)需要大量的時(shí)間才能掌握。

這樣的話(huà)可重構(gòu)計(jì)算的生態(tài)就無(wú)法發(fā)展:門(mén)檻高意味著做的人少,做的人少意味著知名度低,相關(guān)項(xiàng)目數(shù)量少,這又導(dǎo)致了無(wú)法吸引到開(kāi)發(fā)者參與項(xiàng)目。

異構(gòu)計(jì)算與可重構(gòu)計(jì)算

在今天,摩爾定律遇到了瓶頸,因此可重構(gòu)計(jì)算普及的第一個(gè)障礙正在慢慢消失。摩爾定律的瓶頸第一來(lái)自于經(jīng)濟(jì)學(xué),第二來(lái)自于物理定律。從經(jīng)濟(jì)學(xué)的角度,本來(lái)摩爾定律的目標(biāo)就是通過(guò)工藝制程進(jìn)步縮小特征尺寸讓相同功能的芯片需要的晶圓面積更小。工藝制程進(jìn)步所需的研發(fā)成本和mask制作的NRE成本上升,而每塊芯片的制造成本下降

。在之前的幾十年里,工藝制程研發(fā)成本和mask制作的NRE成本上升平攤到每塊芯片中不會(huì)抵消太多芯片制造成本的下降,從而使用新工藝的芯片的總成本相對(duì)于舊工藝會(huì)下降。然而,在最新的工藝中,由于新工藝的mask NRE成本非常高,生產(chǎn)的芯片必須出貨量非常大才能保證攤薄NRE成本上升,這對(duì)于很多芯片設(shè)計(jì)公司來(lái)說(shuō)風(fēng)險(xiǎn)很大。因此經(jīng)濟(jì)學(xué)角度對(duì)于摩爾定律的驅(qū)動(dòng)力大大下降了。

從物理學(xué)角度來(lái)說(shuō),障礙主要來(lái)源于量子效應(yīng)和光刻精度。當(dāng)特征尺寸縮小到10nm的時(shí)候,柵氧化層的厚度僅僅只有十個(gè)原子那么厚,在那個(gè)時(shí)候會(huì)產(chǎn)生諸多量子效應(yīng),導(dǎo)致晶體管的特性難以控制。

另一方面,隨著大數(shù)據(jù)時(shí)代的來(lái)臨,整個(gè)社會(huì)產(chǎn)生的運(yùn)算需求迅猛增加。這一點(diǎn)與摩爾定律遇到的瓶頸此消彼長(zhǎng),導(dǎo)致計(jì)算機(jī)以及半導(dǎo)體行業(yè)不得不停下來(lái)仔細(xì)思考在除了繼續(xù)無(wú)腦改進(jìn)CPU制造工藝之外,還有沒(méi)有其他滿(mǎn)足運(yùn)算需求的辦法。

很自然地,大家想到了計(jì)算機(jī)架構(gòu)這件事。目前在云端的計(jì)算五花八門(mén),包括機(jī)器學(xué)習(xí),數(shù)據(jù)庫(kù),圖像處理,金融運(yùn)算等等。為什么運(yùn)算能力不足?因?yàn)榇蠹叶枷胍獔D方便,只用通用的CPU來(lái)處理所有的任務(wù)。

前面已經(jīng)提到,CPU的架構(gòu)并不適合所有任務(wù),只是因?yàn)樵诖髷?shù)據(jù)時(shí)代來(lái)臨前CPU性能夠強(qiáng)而且編程夠方便所以大家也沒(méi)有想要試試其他的架構(gòu)(當(dāng)然在圖形加速方面用的是GPU,不過(guò)類(lèi)似的例子并不普遍)。今天,顯然光CPU已經(jīng)不足以滿(mǎn)足所有運(yùn)算的需求了,所以可以根據(jù)相應(yīng)的任務(wù)來(lái)設(shè)計(jì)專(zhuān)用加速器,計(jì)算機(jī)由CPU控制并在執(zhí)行該任務(wù)時(shí)把相應(yīng)的運(yùn)算丟給加速器來(lái)完成。

?

大數(shù)據(jù)時(shí)代的數(shù)據(jù)量以指數(shù)上升(上圖),而摩爾定律卻遇到了瓶頸(下圖),晶體管性能增長(zhǎng)有限

這樣的架構(gòu)叫做異構(gòu)計(jì)算,即用各種不同的的運(yùn)算單元去完成相應(yīng)的任務(wù),區(qū)別于傳統(tǒng)的用同一個(gè)運(yùn)算單元(CPU)去完成所有運(yùn)算。

異構(gòu)計(jì)算比起可重構(gòu)計(jì)算來(lái)說(shuō),由于加速器的結(jié)構(gòu)是實(shí)現(xiàn)定義好的,因此無(wú)需使用者(程序員)再次用硬件語(yǔ)言去配置它,所以普及起來(lái)比起可重構(gòu)計(jì)算要容易不少。然而,異構(gòu)計(jì)算也存在一個(gè)問(wèn)題:如果使用者需要臨時(shí)換一個(gè)應(yīng)用,怎么辦?臨時(shí)安裝對(duì)應(yīng)的加速卡很難滿(mǎn)足需求,因?yàn)榧铀倏◤挠嗁?gòu),安裝調(diào)試到最后能用需要很長(zhǎng)的時(shí)間,換句話(huà)說(shuō),異構(gòu)計(jì)算的靈活性是受到限制的。

從另一個(gè)角度來(lái)說(shuō),如果可重構(gòu)計(jì)算能夠突破編程困難這個(gè)瓶頸,那么在大數(shù)據(jù)時(shí)代一定會(huì)成為計(jì)算機(jī)的重要部分。為了解決編程困難問(wèn)題,目前業(yè)界和學(xué)界都在開(kāi)發(fā)能把高級(jí)語(yǔ)言(如C語(yǔ)言)直接轉(zhuǎn)化為硬件的高級(jí)綜合(high-level synthesis tool)工具。除此以外,OpenCL框架也是讓程序員直接編程硬件的可行道路。但是,直到最近,可重構(gòu)計(jì)算的生態(tài)還沒(méi)有起來(lái)。

?

異構(gòu)計(jì)算架構(gòu)示例

大數(shù)據(jù)時(shí)代可重構(gòu)計(jì)算開(kāi)始發(fā)力

近日,可重構(gòu)計(jì)算進(jìn)入了超級(jí)計(jì)算機(jī)業(yè)界的焦點(diǎn),Intel收購(gòu)FPGA制造商Altera,并且預(yù)期到2020 年將會(huì)有三分之一的云端處理器使用CPU-FPGA的混合結(jié)構(gòu)。FPGA巨頭Xilinx也不甘落后,于11月中旬在2016年超算大會(huì)上發(fā)布了可重配置加速棧(Reconfigurable Acceleration Stack)。配合可重構(gòu)的FPGA,該架構(gòu)旨在解決可重構(gòu)計(jì)算中的編程困難問(wèn)題,并加速可重構(gòu)計(jì)算生態(tài)的建設(shè)。

在可重配置加速棧中,Xilinx提供了幾款流行應(yīng)用框架的整合,包括Caffe(深度學(xué)習(xí)應(yīng)用),F(xiàn)FMPEG(視頻處理)以及SQL(數(shù)據(jù)庫(kù))。通過(guò)這樣的整合,云端服務(wù)器的程序員無(wú)需使用Verilog/VHDL硬件描述語(yǔ)言就可以在可重配置加速棧中使用FPGA資源加速這些框架中的應(yīng)用。除此之外,Xilinx還提供了各種庫(kù),通過(guò)在程序中調(diào)用這些庫(kù)也可以實(shí)現(xiàn)更靈活地用FPGA硬件加速程序。

?

Xilinx推出的Reconfigurable Acceleration Stack

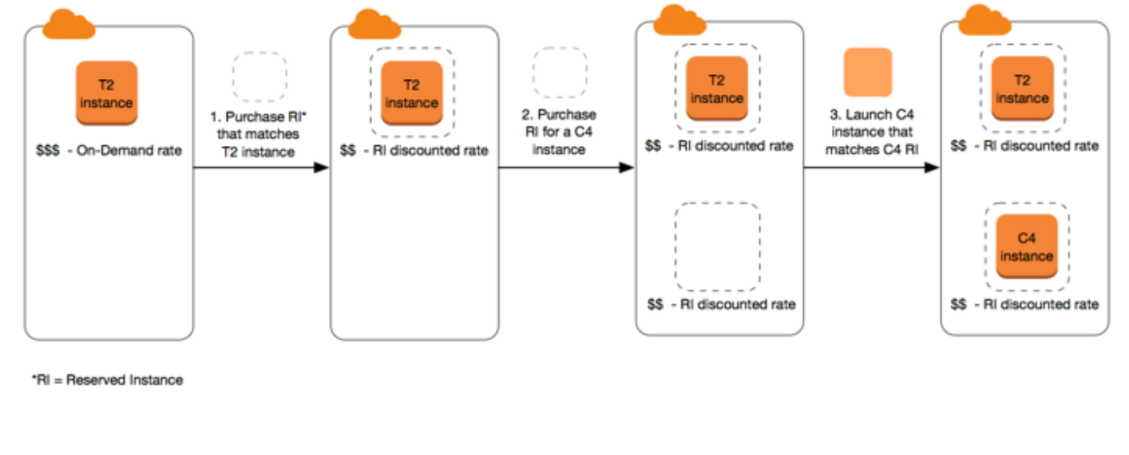

這些用于云端的FPGA將會(huì)使用部分重配置方案。通常FPGA配置過(guò)程包括硬件描述語(yǔ)言的綜合,布局布線(xiàn),最后產(chǎn)生比特流文件并寫(xiě)入以完成配置。在這個(gè)過(guò)程中,綜合以及布局布線(xiàn)花費(fèi)的時(shí)間非常長(zhǎng),可達(dá)數(shù)小時(shí),而最后比特流文件寫(xiě)入以及配置可以在一秒內(nèi)完成。

用于云端的FPGA方案為了實(shí)現(xiàn)快速應(yīng)用切換,預(yù)計(jì)將會(huì)使用硬IP(即針對(duì)某應(yīng)用硬件加速的比特流),并在需要使用該應(yīng)用時(shí)快速寫(xiě)入該比特流。在未來(lái),云端FPGA的生態(tài)預(yù)計(jì)將不止包括Xilinx,還會(huì)包括許多第三方IP提供商,最后形成類(lèi)似App Store的形式讓使用者方便地選購(gòu)對(duì)應(yīng)的硬件加速方案并實(shí)時(shí)加載/切換。

Xilinx FPGA硬件也很強(qiáng),可以非常高效地實(shí)現(xiàn)各種計(jì)算。例如,實(shí)現(xiàn)相同的性能,使用FPGA加速器僅需要CPU服務(wù)器所占空間的1/12, 功耗為CPU服務(wù)器的1/12,而成本也僅為CPU服務(wù)器的1/10。

?

在云服務(wù)商這邊,Amazon云服務(wù)也于近日推出了使用在云端的FPGA解決方案:EC2 F1。該解決方案使用Xilinx的高端Ultrascale+ FPGA(包含250萬(wàn)邏輯單元以及6800個(gè)DSP核),并為每塊FPGA芯片配備64GB的DDR4內(nèi)存,以及與CPU進(jìn)行接口的專(zhuān)用PCIe x16界面。該FPGA將會(huì)接入服務(wù)器,并為相應(yīng)應(yīng)用做加速。另外,F(xiàn)PGA可以通過(guò)高速PCIe接口組成陣列,同一陣列中的FPGA可以以400Gbps的帶寬訪(fǎng)問(wèn)同一個(gè)內(nèi)存空間。在未來(lái),Amazon可望使用FPGA-as-a-Service模式,把FPGA加速(包括硬件以及相關(guān)加速I(mǎi)P)作為產(chǎn)品推出。

?

亞馬遜推出EC2:F1架構(gòu),使用FPGA實(shí)現(xiàn)可重構(gòu)計(jì)算

除了亞馬遜之外,微軟和Intel也在積極布局云端FPGA加速。微軟于兩年前開(kāi)始的Catapult計(jì)劃,使用FPGA為Bing搜索服務(wù)加速,并且將在Azure云服務(wù)商也使用FPGA加速。可望在不久的將來(lái),我們能看到可重構(gòu)計(jì)算生態(tài)的一次快速成長(zhǎng),從而改變云計(jì)算的格局。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論