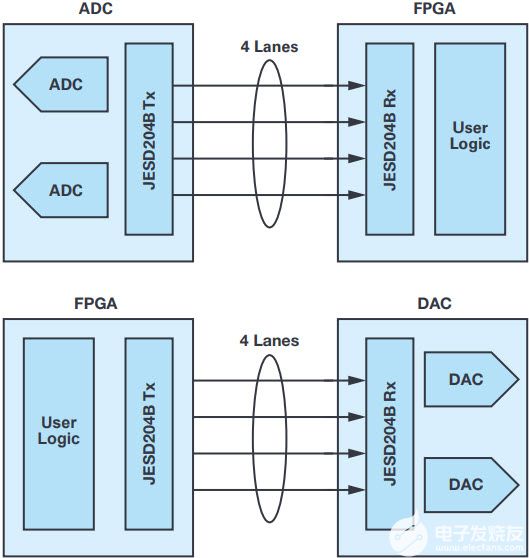

JESD204B是最新的12.5 Gb/s高速、高分辨率數據轉換器串行接口標準。轉換器制造商的相關產品已進入市場,并且支持JESD204B標準的產品預計會在不久的將來大量面世。JESD204B接口的主要價值在于,它能夠可靠地增加轉換器和邏輯器件(比如FPGA或ASIC)之間的數據傳輸帶寬。

與任何新接口一樣,JESD204B同樣帶來了新的挑戰。對于系統開發人員而言,他們面臨的挑戰是如何從PCB設計的角度實現JESD204B最佳部署,以及出現問題后如何進行系統調試。對于元件制造商而言,他們面臨的挑戰包括測試全新的JESD204B器件。測試不僅可以保證器件在相對理想的環境下符合規范,還能確保JESD204B器件在最終系統環境下的正常工作。

本文討論JESD204B規范,回顧驗證JESD204B器件所需的測試,并羅列重現最終系統環境的方法。

JESD204B—數據轉換器的自然演進

從音頻和音樂到測試儀器儀表,很多應用都要用到數據轉換器(數模轉換器和模數轉換器)。數據轉換器的產品處于不斷演進中。隨著位深和采樣速率的增加,數據輸入與輸出也變得越來越困難。十年或二十年前,高速轉換器的采樣速率不超過100 MSPS,因此使用TTL或CMOS并行數據總線就足夠了。例如,可將集成12個數據專用引腳的12位轉換器設置為相對于時鐘而言具有適當的建立與保持時間。

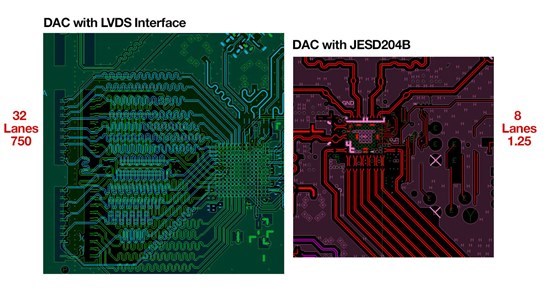

隨著速度突破100 MSPS,便不再能夠維持這種單端信號建立與保持時間。為了提升速度,高速轉換器轉而采用差分信號,但代價是引腳數更多了。例如,12位轉換器此后便需要針對數據提供24個專用引腳。為了解決引腳數量的問題,引入了串行數據接口。轉換器的6×串行數據接口現只需兩個差分I/O(僅4個引腳)便可實現同一個12位轉換器的數據傳輸。飛速發展到今天,數據轉換器的數據接口現已采用JESD204B規范來進行開發。

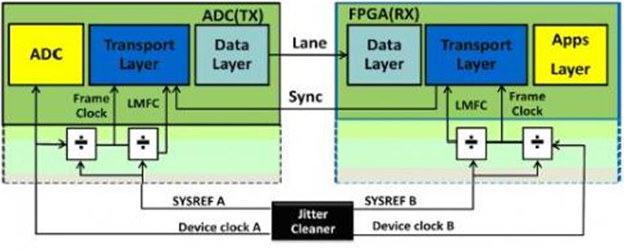

JEDEC標準組織發布了兩種版本的JESD204高速串行數字接口規范。JESD204 2006規范是第一個版本,該版本為數據轉換器帶來了SerDes高速串行接口的優勢,最高額定速度為3.125 Gbps。該版本于2008年發布了修訂版(JESD204A 2008規范),并加入了重要的增強特性,包括支持多條數據通道和通道同步。JESD204B是該規范的第二個版本,由國際JEDEC JC-16任務組(項目:150.01)開發,該任務組由25家公司的約65名成員組成。它提供一系列重大增強特性,包括更高的最大通道速率、支持通過接口的確定性延遲,以及支持諧波幀時鐘。

缺少官方兼容性測試規范

與其他很多高速串行接口標準不同,JESD204B標準不含官方兼容性測試規范。測試規范的價值極高,因為它列出了確保兼容性所必須執行的測試,以及測試步驟。讓不同制造商使用統一的步驟有助于確保對規范取得共識,并消除假設性差異。但缺少官方的兼容性測試規范并不意味著缺少一切。開發一組測試與步驟所需的一切信息均已包含在JESD204B規范,以及相應規范中。各芯片制造商和系統開發商需收集這些信息。

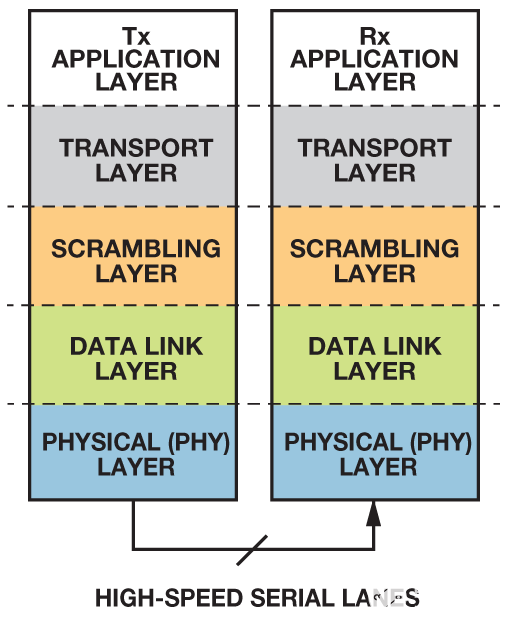

物理層測試

物理層(或稱PHY)測試與各數據通道驅動器和接收器電路有關:換言之,它是鏈路的模擬測試。它們不包括數字功能性測試或程序性測試。開發完整的PHY測試列表時,可從OIF-CEI-02.0規范第1.7節中獲取SerDes PHY測試的推薦列表。JESD204B規范嚴格遵循這些建議,但作了部分修改。例如,JESD204B未將隨機抖動指定為獨立測試項目,而是將其包含在總抖動中。另外,JESD204B指定JSPAT、JTSPAT和經過修改的RPAT作為建議測試圖案,而OIF-CEI-02.0規范則采用PRBS31圖案。

除了所需的PHY測試外,還可執行額外的PHY測試——一些OIF-CEI-02.0規范或者JESD204B規范的PHY部分未列出的測試。比如,可以參考其他SerDes兼容性測試規范,并采用諸如對內偏斜(針對Tx)和對內偏斜容差(針對Rx)等測試。提到這些并不是為了建議將這些測試納入JESD204B規范中,因為確保JESD204B兼容性不需額外的PHY測試;提到這些內容的目的是為了提醒人們:如果某個PHY測試失敗,可以使用其他PHY測試來幫助了解失敗的原因。

確定測試列表后,可從JESD204B規范獲得關于這些測試的限制。只需記住存在三類限制:LV-OIF-11G-SR、LV-OIF-6G-SR和LV-OIF-SxI5。某個特定的JESD204B器件可支持多種限制。這種情況下,應測試元件支持的全部限制。

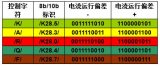

JESD204B PHY測試可能產生的一種混淆與抖動術語有關。JESD204B和OIFCEI-02.0規范使用不同的術語,因而不同測試設備供應商使用的術語也有所不同。典型抖動圖如圖1所示。測試設備生產商的術語依據工業標準雙Dirac抖動模型。這種術語上的不同可能會影響測試步驟,而抖動又是非常棘手的問題。表1顯示的是我們翻譯的抖動術語(JESD204B規范使用的抖動術語和測試設備供應商有所不同)。

?

圖1. 典型抖動圖,包括識別有界不相關抖動(BUJ)

JESD204B PHY測試的另一處可能混淆的地方是數據速率超過11.1 Gbps的眼罩。JESD204B規格中,對于高于11.1 Gbps的數據速率,應使用11.1 Gbps歸一化位時間。因此,如果工作速率為12.5 Gbps(位周期為80 ps),則應使用11.1 Gbps(90.9 ps)位周期。這里的問題是,眼罩可以始于UI的邊緣,也可以始于UI中心,而JESD204B并未明確定義其起始參照點。如果參照點是UI中心,則在12.5 Gbps時眼罩比一般情況下要大,因而Tx更不容易通過,但便于Rx工作。如果參照點是UI邊緣,則在12.5 Gbps時眼罩比一般情況下要小,因而Tx更容易通過,但不利于Rx工作。在這個問題得到解決以前,建議對兩個眼罩選項分別進行測試,以保證兼容性。

時序測試

列出JESD204B的完整時序測試列表是非常困難的。在整個規范中,至少定義了十幾種時序圖,而且無法很快確定Tx、通道或Rx各自對應的時序。此外,某些時序僅適用于特定的子類(0、1或2)。如果只是簡單地將時序規格整合到一張表格內,那么官方兼容性測試規范將起到非常大的作用。只要花一些時間系統地了解這些時序規范,就不會產生混淆。

對于系統開發人員來說,有關時序的一個好消息是,為JESD204B元件設定時序比從規格中直接獲取相關信息更容易了。對于子類0和2來說,只需指定器件的時鐘到SYNC~時序。對于子類1而言,只需指定器件的時鐘到SYSREF時序。

協議測試

對于PHY測試,沒有官方的JESD204B協議測試列表。因此,用戶需自行瀏覽規范內容,并編寫待測功能列表。本節羅列了大量推薦協議測試,并給出簡要說明。

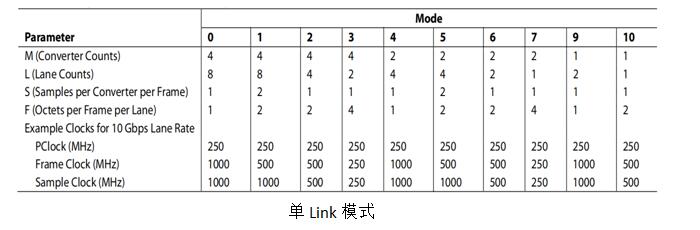

有一類協議測試專門測試序列。對于PHY測試,JESD204B發送器必須要能夠輸出JSPAT并修改RPAT圖案。從協議角度來看,需驗證這些圖案的正確性。JESD204B接收器以及JTSPAT圖案同樣如此。或者,如果支持PRBS圖案,那么也需對其進行驗證。下一步是短傳輸層和長傳輸層圖案。這些內容可以證明鏈路通過傳輸層后工作正常,以幫助系統開發人員進行系統調試。就元件制造商而言,需針對器件支持的每一種工作模式驗證這些傳輸層圖案;考慮到鏈路配置變量的數目,這將會產生大量的不同情況。

有關協議測試帶來的一個問題是如何在12.5 Gbps下完成。一種建議的解決方案是使用帶串行數據解碼器的高速示波器。現在很多高端示波器都配備了專用觸發芯片,觸發8b/10b數據,以支持JESD204B。圖3顯示JESD204B數據通道在6 Gb/s下的串行解碼,位置是初始通道對齊序列(ILAS)的起點。

圖2. 在6 Gbps下對JESD204B數據通道進行串行解碼,并顯示ILAS序列的起始

另一組協議測試可圍繞ILAS構建。ILAS作為整體而言非常復雜,因此將其分配到各獨立的元件能讓協議測試更有意義。下列測試示例可用于發送器的測量,驗證其工作情況。多幀長度正確嗎?是不是每個多幀都以/R/控制碼開頭,以/A/控制碼結尾?/Q/控制碼是否位于正確的位置?鏈路配置數據及其位置是否正確? ILAS含有數據,是真的嗎?ILAS持續幾個多幀?是否所有通道上的ILAS都相同?顯然,圍繞ILAS序列展開的協議測試具有很大的潛力。

JESD204B沒有太多握手,但如果有的話就能被測試。取決于子類,可執行一系列測試。由于SYNC~信號可用作初始握手、錯誤報告以及鏈路再初始化,Tx和Rx元件是否正確執行相應的功能? Rx置位SYNC~是否始于正確的時間,且持續正確的時間? Tx是否根據SYNC~置位的持續時間而作出正確的反應? 由于通過鏈路發送的數據同樣參與了握手(比如ILAS),其內容是否正確,并對應于SYNC~時序?

其次,有一系列較小的數字功能需作為協議的一部分進行測試,包括加擾、8b/10b編碼/解碼、偏斜和偏斜容差、控制位、結束位、SYNC~信號結合、幀對齊監控與校正。所有這些功能都需驗證。

最后,有一類協議測試稱為錯誤處理。規格定義了一組基本錯誤,必須檢測并匯報:偏差錯誤、表外錯誤、意外控制字符錯誤以及代碼組同步錯誤。但除此之外還能檢測并匯報很多潛在錯誤。對于JESD204B元件可以檢測的每一種類型,都應有一個協議測試。測試并驗證這類協議時可能

會遇到一些挑戰,因為正常工作的鏈路永遠不會運用它們。通常它們需要用到專門測試設備。BERT圖案發生器能夠產生含有錯誤的圖案,可在很多測試中使用。FPGA以及修改過的代碼可專門用來產生那些錯誤。

加重和均衡測試

JESD204B規范很少涉及加重和均衡。有一些說明可讓人確信規范允許他們這么做,比如“可能需要預加重”以及“可能需要部署均衡”,但規范也并未給出任何額外的指南。使用集成加重和均衡功能的JESD204B轉換器時,人們如何確定是否需開啟這些功能,以及應在多大程度上使用它們呢?為了回答這個問題,最好先理解抖動的一種類型,稱為符號間干擾(ISI)。ISI這個名稱表示邊沿時序的變化,由傳輸線上的濾波效應所導致。數學上,它能簡單地建模為低通濾波器。通過傳輸線發送高速串行數據時,該濾波效應會使信號失真。加重和均衡可以抵消ISI的濾波效應,其目的是將通道終端的高頻響應帶回到頻率范圍內盡可能接近平坦的程度,從而使信號不為ISI的失真所影響。

對加重和均衡以及ISI有了基本了解之后,下一步便是設置。很多人首先會問的第一個問題是,采用與不采用加重/均衡的情況下,走線分別能被驅動至多遠處。現實中,PCB設計時存在太多的變量會影響ISI,進而影響通道的走線長度。這些變量有:走線寬度、走線長度、是否有過孔、電介質材料、有無連接器、走線材料、轉折頻率、無源器件,以及與接地層之間的距離等都會影響通道性能。那么,通道特性又是如何與加重/均衡相關的呢?答案在于通道的插入損耗。在JESD204B規范中,插入損耗定義為信號在頻率范圍內的功率損耗。加重、均衡和PCB通道都會受到

插入損耗(和增益)的影響。采用相關頻率(JESD204B規范中羅列了?波特率)和插入損耗限值(JESD204B羅列了?6 dB),可選擇加重和/或均衡提供的增益,將特定頻率下的頻率響應提升至損耗限值以上。例如,在+9 GHz時損耗為?12 dB的PCB通道需要+6 dB加重/均衡增益,才能使總響應回升至?6 dB。

另外,轉換器制造商可以提供一張表格,列出加重/均衡設置與PCB插入損耗的關系。這種方法可以催生出更好的解決方案,因為它沒有太多的假設。如需為發送器構建這樣的表格(并仿真最終系統設計),可搭建一組具有不同走線長度的測試評估板。

可直接測量PCB走線末尾處的眼圖,并與JESD204B Rx眼罩相比較。嘗試各種PCB走線長度,然后找出使眼圖恰好通過眼罩的長度。由于可測量該特定走線的插入損耗,因此特定加重設置的驅動能力是已知的。將圖3中ISI PCB末尾處的眼圖與圖4進行對比,可以看到,眼圖進入了ISI PCB。此時,數據速率為5 Gb/s,ISI PCB在4 GHz處的插入損耗為8 dB,加重處于關斷狀態。

采用不同的加重設置重復該過程,則可得到加重設置與插入損耗的關系表。可在接收器上采用均衡執行類似的操作。一開始可以采用輸出總抖動為最大允許值的BERT發生器(ISI抖動除外)。使用走線長度不同的同一組ISI測試板,并在測試中不斷增加走線長度,直到接收器開始出現超過目標誤碼率的錯誤(1E-15)。測量PCB走線插入損耗。針對每一個均衡器設置重復此過程。總而言之,如果JESD204B器件制造商僅提供加重/均衡增益,則可以采用第一種方法來拾取設置。而最佳方法則是制造商提供設置與通道插入損耗的關系表。

圖3. 長ISI PCB末尾的眼圖

圖4. 眼圖進入長ISI PCB

是否需要使用加重或均衡?從頻率響應校正的角度來說,并沒有很充分的理由使用它們。然而,大多數情況下,加重可以產生一定量的增益,且功耗更低。若系統功耗很重要,那么這將是采用加重而非均衡的一個理由。選擇加重而不選擇均衡的另一個優勢,是它對信號的影響可以直接通過示波器進行衡量。

JESD204B Tx具備加重且Rx具備均衡也是很常見的。如何確定是否同時開啟兩種功能?簡單而言,如果通道的插入損耗無法只采用加重或者只采用均衡而克服,那么就應當同時使用這兩者。至于兩者的增益如何設置,則以插入損耗(和增益)來指定響應的一個優勢便是,它是可以相加的。(例如,在目標頻率處: 若PCB走線損耗為?20 dB,Tx加重為+6 dB,Rx均衡為+8 dB,則它們的總和可以表示為:?20 dB +6 dB +8 dB = ?6 dB)。

系統環境仿真——噪聲和抖動

沒有哪一種最終系統設計是不存在噪聲或抖動的。JESD204B規范完整定義了系統抖動的仿真,但未定義電壓噪聲。若要在最終系統設計中仿真電壓噪聲,則元件制造商可以執行噪聲容差測試。電源噪聲容差就屬于這類測試。執行該測試時,將噪聲引入元件的各種電源域內。增加噪聲幅

度,直到第一次兼容性測試失敗(通常情況下,抖動會導致第一次測試在SerDes處失敗)。在那些通常存在PCB噪聲的頻率范圍內重復該測試(數Hz到100 MHz左右)。由此可產生最大電源噪聲容差與頻率的關系曲線。可在其他所有引腳上執行同樣的測試。所有這些測試的最終結果通常會給出一組實用的PCB設計建議,比如“隔離某個特定的電源域”或者“在此引腳上使用一個旁路電容”,又或者“不要在此引腳附近路由任何信號”。

測量時保持信號完整性

與任何高速串行測試應用相同,可通過一系列的最佳實踐來確保具有精確的測量結果;另外,您必須確認您的儀器儀表提供足夠的性能與信號完整性,以便得到準確的測試結果。下面是一些考慮因素:

動態范圍:一般而言,最好使用示波器的整個模數動態范圍,避免放大器被削波。考察時鐘信號時削波或許是可以接受的,但這樣做會隱藏評估數據信號時的ISI問題,并且還會影響到儀器儀表的邊沿插值算法。

采樣速率:將示波器設為最高采樣速率可提供最佳時序解決方案,可獲得最精確的信號和抖動測量結果。但有一種情況例外,即以較低的時序精度觀察較長的時間窗口。

捕獲窗口:在時間較長的窗口范圍內分析信號可讓您觀察到低頻調制效果,比如電源耦合和擴頻時鐘。不幸的是,擴寬捕獲窗口同時也會增加分析處理時間。通常在SerDes系統中,并沒有必要去查看CDR環路帶寬(即跟蹤并抑制的帶寬)以下的調制效果。

測試點訪問和去嵌入:確保采用適當機制,將探針保持在盡量靠近Tx測試點以及Rx測試點的位置。執行高速采樣測試時,如果測量過程中引入了長走線和/或實際Tx/Rx測試點夾具所產生的干擾信號,則針對時序和幅度的測量會嚴重影響裕量測試結果。

某些情況下,探針訪問點的位置可能會造成信號衰減;這是由傳輸線長度所導致。這種情況下,您可能需要去嵌入傳輸線才能看到真正的信號。去嵌入包括重建儀器儀表與目標測試點之間的測量通道模型(使用S參數線性法)。可將該模型用在示波器獲取到的波形數據上,補償傳輸線衰減(見圖5)。

圖5. 表示測試夾具、通道終端以及后置均衡測量的眼圖

在測量技術中實現良好的信號完整性可讓您更好地評估并特性化高速技術,比如JESD2024B。

小結

最新發布的JESD204B接口能夠可靠地提升轉換器和邏輯器件之間的傳輸帶寬;目前市場上已出現很多使用這種接口的新器件。與其他很多高速串行接口標準不同,JESD204B標準不含官方兼容性測試規范,這給必須徹底測試并調試設計的系統設計人員帶來了極大的挑戰。幸運的是,規范包含了足夠的信息來幫助開發測試程序,包括PHY、時序和協議測試。

除了驗證性能以及兼容性是否符合規范外,測試還有助于確定系統設計是否需要加重或均衡,并協助識別干擾噪聲源和干擾抖動源。與任何高速串行測試相同,應當遵循儀器儀表選擇、設置以及探測等的最佳實踐,以便確保結果的一致性和精確性。

作者簡介

Frank Farrelly是ADI公司的產品工程經理。他已在ADI公司工作19年,目前負責高速SerDes產品的特征化與驗證。他擁有田納西州諾克斯維爾大學電氣工程學士學位(BSEE)以及北卡羅來納州格林斯博羅大學工商管理碩士學位(MBA)。Chris Loberg是Tektronix?公司的高級技術營銷經理,負責美洲地區的示波器業務。Chris已在Tektronix公司工作了13年以上,曾擔任各種職務,包括Tektronix光產品業務部門營銷經理。Chris擁有豐富的技術營銷經驗,曾在Grass Valley Group和IBM任職。他擁有圣何塞州立大學市場營銷MBA學位。

電子發燒友App

電子發燒友App

評論