作者:Paul Zorati,賽靈思公司汽車電子部駕駛員輔助高級系統架構師

過去五年來,汽車產業在駕駛員輔助 (DA) 系統方面取得了顯著進步,在切實豐富駕駛體驗的同時,為駕駛員提供了寶貴的周邊路況信息。本文著眼于如何運用 FPGA 迅速將最新駕駛員輔助創新技術推向市場。

駕駛員輔助技術介紹

自上個世紀 90 年代早期以來,高級 DA 系統開發人員一直在為實現更安全、更舒適的駕駛體驗而努力。過去二十年里,超聲停車輔助、自適應巡航控制、車道偏離警告系統等 DA 功能已在高端汽車中得到部署和采用。

近來,汽車制造商新增了后視攝像頭、盲點檢測和環視系統等選項。除超聲停車輔助功能外,DA 系統的應用量仍然有限。但據市場調研公司 Strategy Analytics 預測 DA 系統的應用將在未來十年出現顯著增長。

除了政府立法因素和消費者對安全功能的強烈關注,遠程傳感器和用于提取和解讀關鍵信息的相關處理算法的創新,也在促進 DA 系統應用的增長。隨著時間的推移,這些 DA 系統將變得更加復雜,并且從高端車輛進入主流車輛,而 FPGA 處理功能將扮演主要角色。

駕駛員輔助傳感技術發展趨勢

傳感器研發人員借毗鄰市場(如手機攝像頭)的他山之玉,開發出了不僅能用于汽車環境,還能滿足嚴格成本控制的器件。無獨有偶,開發人員使用基于 PC 的工具對復雜處理算法進行了優化,并將其移植到嵌入式平臺上。

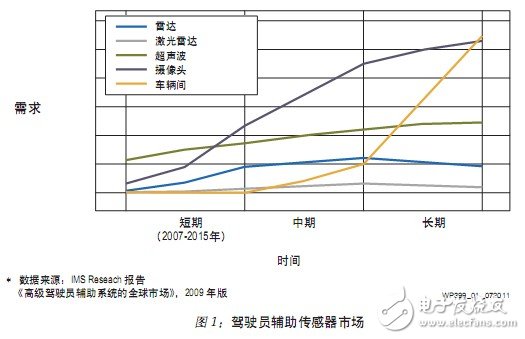

雖然超聲傳感技術一直主導市場,IMS Research 研究機構(圖 1)認為未來幾年將是攝像頭傳感器的天下。

攝像頭傳感器的獨特之處就是能夠同時提供原始輸出和經過處理的輸出。來自攝像頭的原始視頻可直接顯示給駕駛員,用于確認和評估危險狀態,這是其它類型的遠程傳感器無法企及的(比如雷達) 。

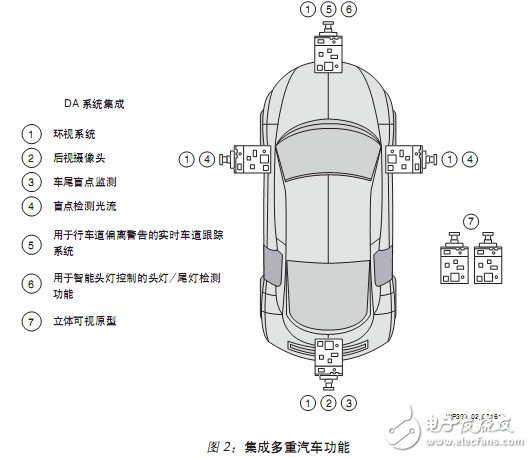

另外(或者說同時) ,視頻輸出可使用圖像分析功能進行處理,提取關鍵信息,比如行人的位置和運動。開發人員還可在一組攝像頭的基礎上集成多種消費功能,擴大這種攝像頭傳感器數據的 “雙重用途” ,如圖 2 所示。

從這些應用,我們可以總結出一些關于適用于基于攝像頭的 DA 系統的處理平臺的要求:

? 它們必須同時支持視頻處理和圖像處理。

? 其中視頻處理指的是正確處理原始攝像頭數據,并顯示給駕駛員;圖像處理指運用分析功能從視頻流中提取信息(例如運動) 。

? 它們必須為并發功能相關的算法提供并行數據路徑。

? 鑒于眾多新功能要求百萬像素級圖像分辨率,連接功能和存儲器帶寬與原始處理能力同等重要。

滿足 DA 處理平臺要求

FPGA 能夠很好地滿足 DA 處理平臺的要求。例如,在集成有車尾盲點警告功能的寬視野單攝像頭系統中,DA 系統旨在校正車后區域的圖像畸變,提供正確的圖像。另外,目標檢測算法和動作估算算法可以在目標從側面進入預計的車輛路徑時生成音頻警告。

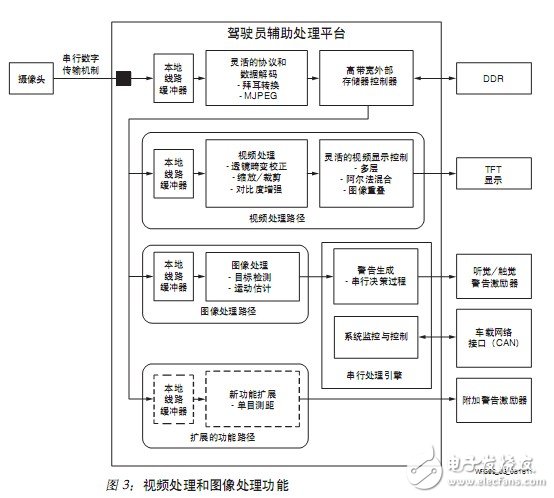

圖3 顯示了攝像頭信號如何在視頻處理功能和圖像處理功能之間分配。執行這些功能的原始處理能力會很快超過串行數字信號處理器 (DSP) 所具備的能力。并行處理配合硬件加速是一款可行的解決方案。

FPGA 為解決各種處理策略提供高度靈活的架構。在 FPGA 邏輯中,將攝像頭信號分別饋給到彼此獨立的視頻處理和圖像處理 IP 模塊是一件簡單的事情。與必須在各項功能之間時分復用資源的串行處理實現方案不同,FPGA 能夠獨立運行處理模塊以及為處理模塊提供時鐘。

另外,如果有必要修改處理架構,FPGA 能夠重新編程硬件模塊。這是采用專用標準產品 (ASSP) 以及專用集成電路 (ASIC) 的解決方案所無法企及的,因此 , 在可預期的未來,基于 FPGA 的方案向高級算法發展時具有明顯優勢。對于計算密集型處理,FPGA 器件(諸如最新推出的 XA Spartan?-6 FPGA 汽車系列)可提供多達 180 個帶預加法器的乘法累加器 (MACC)。

FPGA 實現方案的另一大優勢就是器件可擴展性。由于 OEM 廠商期望集成更多功能,處理需求會增加。例如,后視攝像頭可能需要采用單目測距算法,為駕駛員提供目標距離信息。這項新增功能要求另一條并行處理路徑。在專用 ASIC 或 ASSP 中實現上述擴展即便不是不可能,但也會帶來麻煩,除非設計人員提前為這種擴展采取預防措施。

如果試圖在串行DSP上實現此項功能,就需要對軟件設計進行徹底的重新架構,即便是移植到功能更強大的DSP系列器件之后也是如此(如果可以)。

相比之下,基于 FPGA 的實現方案可以添加新的功能模塊,充分利用此前尚未使用的 FPGA 邏輯,同時基本不影響現有模塊。即便新功能要求的資源多于原始器件上所能提供的,部件/封裝組合也一般能支持移植到密度更大的器件(即擁有更多處理資源的器件),無需重新設計電路板或現有的 IP 模塊。

最后,FPGA 的可重編程性能夠讓相互排斥的 DA 功能重復使用同一芯片。以后視攝像頭為例,當車輛倒車時,其功能非常有用,不過采用基于FPGA 的系統在車輛向前行駛時也可以使用同一傳感器和處理電子設備,比如盲點探測功能。

在該應用中,系統通過分析攝像頭圖像來判斷被探測目標的位置和相對運動。由于這項功能及其相關處理功能與倒車時需要的功能不同,不需要同時處理,系統可以根據車輛的狀態,在數百微秒時間內重新配置 FPGA 邏輯。這樣就可以用很少的費用完全重用FPGA,以提供完全不同的功能。

滿足 DA 外部存儲器帶寬要求

除了原始處理性能,采用攝像頭的 DA 應用要求較高的外部存儲器訪問帶寬。支持集中處理的多攝像頭系統(如四攝像頭環視系統)對此要求最為嚴苛。假定圖像大小為 4 百萬像素(1,280x960),色彩處理為 24 位,性能為每秒30幀 (FPS),將圖像存儲在外部緩沖區中則要求 3.6Gb/s 的內存訪問帶寬。如果需要同時讀取和寫入圖像,則要求內存訪問帶寬翻倍到 7.2Gb/s。在 80% 讀/寫突發效率下,則要求內存訪問帶寬提高到 8.5電路Gb/s。該估算還不包括其它暫時存儲或代碼訪問需求。有這樣的要求,很明顯基于攝像頭的 DA 應用屬于內存超帶寬應用。

這些系統也通常需要存儲器控制器;但要低成本地添加一個存儲器控制器,要求高效率的系統級設計。開發人員再度可以借助 FPGA 的靈活性來滿足這一要求。XA Spartan-6 提供兩種硬化的存儲器控制器模塊 (MCB) 供設計人員配置 4 位、8位或 16 位 DDR、DDR2、DDR3 或 LPDDR 存儲器接口。設計人員可為 MCB 配備高達 400MHz 的時鐘,為 16 位寬度存儲器器件提供 12.8Gb/s 的內存訪問帶寬。另外,如果采用兩個 MCB,原始帶寬就倍增至 25.6Gb/s。兩個 MCB 既可獨立工作,也可通過 FPGA 邏輯協同工作,提供 32 位虛擬數據帶寬。

總而言之,FPGA 存儲器控制器可提供定制的外部存儲器接口設計選項,以滿足 DA 帶寬需求并優化各個成本組成部分(存儲器器件類型、PCB 層數等)。

DA 圖像處理對片上存儲器資源的需求

除了外部存儲器需求,基于攝像頭的 DA 處理還能受益于片上存儲器。片上存儲器可用作線路緩沖器,來處理流視頻或分析圖像數據模塊。拜耳轉換、透鏡畸變校正、光學流運動分析均為要求視頻線路緩沖器的功能示例。出于簡單的定量分析目的,已檢驗使用 12 位像素拜耳圖形強度信息生成 24 位顏色數據的拜耳轉換功能。原始流視頻處理采用雙三次插值處理,要求緩沖四線路圖像數據。將 12 位密度數據打包到 16 位的單元上,需要每線提供約 20.5kb 的存儲容量,或者為四線路數據供提供 82kb 的存儲空間。

FPGA 以 Block RAM 的形式提供片上存儲器資源。XA Spartan-6 系列提高了 Block RAM 邏輯比,用以支持圖像處理需求。XA Spartan-6 能夠提供容量介于 216kb 到 4.7Mb 之間的 Block RAM 存儲器。該存儲器采用時鐘速率為 320MHz 、容量為 18kb 的雙端口模塊構建而成。

通過高速串行接口傳輸視頻數據

另一個 DA 處理平臺問題與遠程安裝的攝像頭和中央處理模塊或顯示模塊之間的視頻數據傳輸息息相關。當今大部分攝像頭裝置主要依賴模擬復合視頻傳輸(例如NTSC) 。但這種方法給高級 DA 系統帶來了幾大問題。場交錯會降低目標識別和運動估算算法的效果;模擬信號易于受電氣噪聲的影響,從而劣化圖像質量;隨著數字成像器的出現,復合視頻 (CVBS) 格式的轉換還會造成不必要的系統成本。

首選方法是使用數字傳輸機制。并行傳輸 12 位數據會造成線纜和接頭成本不菲,因此考慮采用低壓差分信號 (LVDS) 或以太網技術的串行方案。串行化像素數據要求使用帶高速接口的器件。12 位像素深度的 30FPS 百萬像素成像器每秒可以生成 500Mb 以上的數據。

XA Spartan-6 器件提供的差分 I/O 能夠以超過 1Gb/s 的速率運行。該系列的幾個產品還提供時鐘速率高于 3Gb/s 的串行收發器。可以將這些高速 I/O 功能與 FPGA 邏輯相結合,用于在 FPGA 器件自身內部實現新興的 LVDS SerDes 信號協議,從而減少外部組件,降低系統成本。

并行和串行 DA 處理的功能分區

以支持車尾盲點警告功能的單攝像頭系統為例,很明顯,雖然車尾盲點警告是一個串行決策流程,但視頻和圖像處理功能均受益于并行處理和硬件加速技術。故一個能夠同時支持兩種類型的處理的平臺具有明顯優勢。

賽靈思的 FPGA 支持如 XA Spartan-6 器件中提供的 MicroBlazeTM 32 位 RISC 嵌入式處理器這樣的軟處理器的實例化。將全功能處理器與 FPGA 邏輯相結合,可以實現理想的功能分區,即將受益于并行處理或硬件加速的功能實現在 FPGA 邏輯中,而將更適合串行處理的功能實現在軟件中,由 MicroBlaze 處理器負責執行。雖然 MicroBlaze處理器能夠支持片上系統 (SoC) 架構,但賽靈思 7 系列器件中的可擴展處理平臺仍采用了硬化的 ARM? 雙核 CortexTM-A9 處理器以及一組硬化的外設。賽靈思 7 系列器件針對的是最為復雜的 DA 系統。

結論

從事 DA 處理平臺設計的系統設計人員必須考慮架構的靈活性、平臺的可擴展性、外部存儲器帶寬、片上存儲器資源、高速串行接口和并行 / 串行處理分區。最大的難題在于要在滿足這些要求和保持有競爭力優勢的產品成本結構之間實現最佳平衡。要實現此目的,FPGA 技術是標準 ASSP 和 ASIC 方法可行的替代方案。尤其是 XA Spartan-6 系列的資源屬性為滿足 DA 處理平臺的要求提供了獨特的選項和功能。隨著當今的 FPGA 普遍采用 40nm 工藝節點以及 7 系列器件升級到 28nm 工藝,其作為DA 處理平臺的競爭優勢必定在不久的將來大放異彩。如欲了解有關XA Spartan-6系列及其優勢,敬請問:www.xilinx.com/cn/xas6。

電子發燒友App

電子發燒友App

評論