3.1. ZEDBOARD的控制輸入IP

該IP設計主要完成對5個按鍵以及2個開關狀態的檢測及編碼,使產生8位編碼數據,用以傳送給XPS構建的子系統的8位GPIO,以axi_lite相關協議映射編碼數據,從而將編碼輸入傳送到了PS (Processing System: ARM處理器)部分,用以軟件編程檢測和處理。

該設計的實現原理如圖6所示,通過計數模塊Count實現按鍵狀態的去抖檢測,兩個按鍵用于縮放算法選擇,并用三個Led的二進制實時顯示,另兩個按鍵用于選擇縮放倍數,一個按鍵用于錄入狀態與完成錄入狀態間的切換;兩個開關則分別控制放大/縮小、顯示使能。

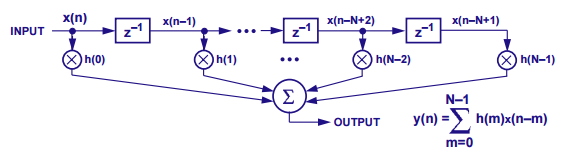

3.2. WLI算法IP

3.2.1. Axi4接口

Axi4 [8] 是由Xilinx和ARM合作提出的便于全可編程器件內部ARM和FPGA之間數據的高速通信的總線標準。Zedboard內部使用Axi4,可細分為Axi_lite、Axi4、Axi_stream三大類,包含地址、數據和反饋通道。能實現ARM和FPGA內部的高速并行數據通信,并支持DMA (direct memory access)通信。

3.2.2. 符合Axi4接口的WLI算法IP

Vivado HLS是Xilinx針對其全可編程器件而推出的高級綜合組件,該軟件可以實現對C語言編寫的程序的直接硬件化,并能很好的綜合出符合Axi標準的IP [9] - [12] 。本文的設計采用這種設計方法,借助OpenCV的MAT的相關內容、要求,編寫可綜合算法程序,圖7是WLI算法的實現流程。

映射策略確定新圖中的一行在原圖的行位置,通過每次縮放一行新圖數據的基本策略,用四個數組(Bram存儲)緩存與映射行相關的四行原圖點值,從而實現算法的二維縮放。WLI子模塊實現對一維4個相關點的算法縮放,通過先行后列的策略實現個相關點的圖像縮放目的。

圖5. 縮放算法硬件系統架構

圖6. 控制輸入IP結構框圖

圖7. WLI算法流程

3.3. 硬件系統搭建

HLS綜合出算法的硬件IP后,通過Planahead環境完成整個硬件系統的搭建。圖8為系統結構示意圖,該系統包括PS子系統、內存間以HP通道(DDR內存和FPGA間的高寬帶、高速數據通道)直接進行數據通信的VDMA、GPIO等IP,以及自主設計的WLI算法IP和VGA顯示IP [13] 。

4. 軟硬協同驗證實驗

4.1. 軟件原理

在硬件系統搭建完成以后,借助于Xilinx的SDK集成環境進行軟件設計。圖9是整個軟件設計運行的流程圖,主要分為初始化、原始圖片選擇接收存儲、GPIO初始化、縮放倍數檢測統計、按鍵狀態檢測判斷和相應算法處理及對比顯示等。

軟件設計中,通過接收PC的選擇信號,選擇使用預定義的圖片,或接收從PC傳來的新圖片。然后進入循環檢測和縮放處理過程,便于演示。同時,通過顯示使能控制端,可以再次更新PC的顯示數據。而縮放顯示模式不僅決定縮放的算法選擇(軟件或硬件),還決定顯示模式(單一還是對比顯示)。

當檢測到GPIO為倍數錄入狀態時,應當進入倍數的檢測和相應操作模式,由此可實現0.1精度的任意倍數圖像縮放效果,并能夠對基于不同縮放算法得到的圖片進行對比顯示。

4.2. 軟硬件協同驗證

通過SDK將編譯好的bootloader程序、FPGA配置bit文件和裸機程序封裝成boot.bin文件,以SD卡實現Zedboard的脫機演示系統。其驗證實驗的系統如圖10所示,右圖是雙三次插值算法軟件縮放結果,而左圖則是WLI算法硬件縮放圖。

各縮放算法在ARM裸機上縮放圖片所耗用時間 [14] 的對比結果如圖11所示。其中最近鄰(Near)、雙線性(Biline)、雙三次(Bcubic)和CCI等為軟件縮放算法,WLI算法為硬件實現算法。

盡管軟件縮放算法在約667 MHz的Cortex A9處理器上運行,而通過FPGA硬件化的WLI算法的運行時鐘僅為100 MHz,但圖11的結果表明,其縮放耗時仍同最近鄰算法相當(Near幾乎被WLI覆蓋了),可見在相同時鐘條件下,其計算效率將會大幅提高,體現硬件實現的并行特征。

圖8. 硬件系統結構

圖9. 軟件處理流程圖

圖10. 圖像縮放對比顯示演示系統

圖11. 各縮放算法不同倍數耗時對比

5. 結論

本文主要研究了時域圖像縮放算法中比較常用的幾種縮放算法,并基于一種稱為WLI的圖像縮放算法,在Xilinx的全可編程器件開發板Zedboard上實現了算法的硬件化,并構建了軟硬協同驗證系統,實現了脫機演示。

本文設計的IP實現了硬件圖像縮放,并與基于軟件實現的圖像縮放具有相同效果,而計算效率提高了至少一個數量級,充分體現了硬件實現圖像縮放的優異性和可行性。

參考文獻 (References)

1. Choi, B.-D. and Yoo, H. (2009) Design of piecewise weighted linear interpolation based on even-odd decomposition and its application to image resizing. IEEE Transactions on Consumer Electronics, 55, 2280-2286.

2. 劉婧 (2009) 圖像縮放算法的研究與FPGA設計. 碩士論文, 上海大學, 上海.

3. 李秀英, 袁紅 (2012) 幾種圖像縮放算法的研究. 現代電子技術, 35, 48-51.

4. Wang, J. (2011) MATLAB三種程序耗時算法.

5. 心海 (2013) PSNR定義與計算.

6. Li, X. (2002) Blind image quality assessment. IEEE ICIP, 1, 449-452.

7. Xilinx (2014) Zynq-7000 all programmable SoC. Xilinx數據手冊.

8. Xilinx (2011) Xilinx, AXI reference guide UG761 (v13.1) March 7. Xilinx數據手冊.

9. 馬建國, 孟憲元 (2011) FPGA現代數字系統設計. 清華大學出版社, 北京.

10. 仆居 (2013) AXI-Stream接口開發詳細流程.

11. 何賓 (2011) 基于AX14的可編程SOC系統設計. 清華大學出版社, 北京.

12. 何賓 (2011) Xilinx all programmable Zynq-7000 SOC設計指南. 清華大學出版社, 北京.

13. 開源硬件社區 (2009) VGA驅動及實現.

14. Cuter (2013) 如何在SDK中計算某段程序的執行時間.

電子發燒友App

電子發燒友App

評論