角度傳感器在與FPGA 正確配合下能夠幫助工程師打造出無與倫比的機械。

自從人類發明了轉輪,我們就希望了解如何通過改變精度提高轉輪轉動效率。在過去幾個世紀,科學家和工程師已經研發了許多方法來實現此目標,期間輪- 軸系統的基本原理得到了廣泛應用,從汽車、音量旋鈕、各種機械形式的齒輪到簡陋的手推車,幾乎每種機械系統均采用了這一原理[1]。

經過多個時代的探索,人們發現讓轉輪高效運轉的最重要因素并非轉輪本身(為何不徹底改造它呢?),而是轉輪的軸角。目前測量和優化軸角的最有效方法是采用角度傳感器。現有許多種角度傳感器都能夠通過輪軸監控和改進促進輪周效率優化;但如果配合使用FPGA,您就能夠取得非常顯著的效果,同時能夠提高眾多應用中的輪軸/ 輪周效率。

在詳細介紹工程師們如何最佳利用賽靈思FPGA 達到上述目的之前,先讓我們簡單回顧一下角度傳感器的部分基本原理。目前得到廣泛應用就是編碼器和分解器這兩類角度傳感器。

編碼器和分解器的類型

編碼器分為增量和絕對兩個基本類別。增量編碼器可以監控輪軸上的兩個位置,并且可以在輪軸每次經過這兩個位置時產生A 或B 脈沖。獨立的外部電動計數器然后從這些脈沖解讀出轉速和旋轉方向。雖然適用于眾多應用,但是增量式計數器確實存在某些不足。例如,在輪軸停轉情況下,增量編碼器在開始運行之前必須首先通過調回到某個指定校準點來實現自身校準。另外,增量式計數器易受到電氣干擾的影響,導致發送到系統的脈沖不準確,進而造成旋轉計數錯誤。不僅如此,許多增量編碼器屬于光電器件 – 如果對目標應用有影響,則無法用于輻射危險區域。

絕對編碼器是監控輪軸旋轉計數和方向的傳感器系統。在基于絕對編碼器的系統中,用戶一般把轉輪連接到具有電觸頭或光電基準的輪軸。在輪軸運行時,基于絕對編碼器的系統會記錄旋轉和運行方向,同時產生易于轉換成代碼(最常見的是二進制碼或格雷碼)的并行數字輸出。絕對編碼器的優勢在于只需要校準一次(一般是在工廠中校準),而無需每次使用前都校準。此外,絕對編碼器一般比其它編碼器更可靠。不過,絕對編碼器一般很昂貴,而且它們不利于進行并行數據傳輸,尤其是在測量其讀數的電子系統距離編碼器較遠情況下。

分解器就其本身而言是一種旋轉變壓器—— 一種輸出電壓與其所監控的輸入軸角唯一關聯的模擬器件。它是一款具有0o~360o 旋轉角度的絕對位置傳感器,其直接連接到輪軸并報告轉速和位置。分解器與編碼器相比有諸多優勢。分解器非常穩健可靠,能夠經受帶有灰塵、油污、極端溫度、振動和輻射的嚴酷環境。作為一種變壓器,分解器可以提供信號隔離以及對電氣干擾的自然共模抑制。除了這些特性之外,分解器只需要四根線就可進行角數據傳輸,這使其能夠適用于從重工業、微型系統到航空航天工業等各種應用。

無刷分解器得到了進一步改進,其無需與轉子的滑環連接。因此,這種分解器更可靠,而且使用壽命更長。

分解器采用兩種方式獲取與軸角相關的輸出電壓。在第一種方式中,如圖1 所示的轉子繞組由交變信號激勵,而輸出來自兩個定子繞組。由于定子是以機械方式定位到正確角度,因此輸出信號幅度是通過軸角的三角正弦和余弦關聯。正弦與余弦信號均具有與原始激勵信號相同的相位;僅其幅度隨輪軸的旋轉通過正弦與余弦進行調制。

圖1 – 分解器轉子激勵

在第二種方式中,定子繞組由相位正交的交變信號激勵。然后在轉子繞組中感應電壓。繞組的幅度和頻率固定,但其相移隨軸角變化。

分解器可以放置到需要測量角度的位置[2]。而電子裝置一般指的是分解器數字轉換器(RDC),可以放置到需要測量數字輸出的位置。分解器的模擬輸出(含有輪軸角位置信息)然后經RDC 轉換成數字形式。

典型RDC 的功能

一般而言,分解器的兩個輸出會應用到RDC 的正弦與余弦乘法器[3]。這些乘法器結合正弦和余弦查找表以及函數構成乘法數模轉換器。圖2 顯示了其功能。

圖2 – 分解器數字轉換器(RDC)方框圖

暫且假設開始時遞增/ 遞減計數器的當前狀態是一個代表試驗角度(trial angle)ψ 的數值。轉換器設法調整數字角度ψ,使其一直等于并跟蹤所測量的模擬角度θ。

分解器的定子輸出電壓為:

V1= V sinωt sinθ

方程 1

V2= V sinωt cosθ

方程 2

其中θ 是分解器轉子的角度。數字角度ψ 應用到余弦乘法器,其余弦乘以V1 得出下式:

V sinωt sinθ cosψ.

方程 3

數字角度ψ 另外還應用到正弦乘法器,乘以V2 得出下式:

V sinωt cosθ sinψ.

方程 4

這兩個信號由誤差放大器相減求得出波形的誤差信號:

(V sinωt sinθcosψ – V sinωt cosθ sinψ)

方 程 5

V sinωt (sinθ cosψ- cosθ sinψ)

方程 6

根據三角恒等式,其簡化為:

V sinωt [sin (θ -ψ)]

方程 7

檢測器采用分解器的轉子電壓作為基準同步解調此AC 誤差信號。這會產生與sin (θ-ψ) 成正比的DC 誤差信號。

DC 誤差信號饋送到積分器,其輸出驅動一個由電壓控制的振蕩器。而VCO 會導致遞增/ 遞減計數器按正確方向計數,從而在一次計數中產生:

sin (θ-ψ)→0.

方程 8

當取得此結果,則:

θ -ψ→0,

方程 9

因此,

θ = ψ

方程 10

因此,計數器的數字輸出ψ 代表著角度θ。鎖存器可以在不中斷回路跟蹤情況下實現此數據向外部的傳輸。

此電路等效于2 型伺服回路,因為它實際上有兩個積分器。一個是累計脈沖的計數器;另一個是位于檢測器輸出端的積分器。在具有恒定旋轉速度輸入的2 型伺服回路中,輸出數字字連續跟隨或跟蹤該輸入,而無需外部導出轉換。

RDC 典型實例:SD-14621

SD-14621 是數據設備公司(DDC)生產的小型低成本RDC。它有兩條具備可編程分辨率控制功能的信道。分辨率編程功能允許選擇10、12、14 或16 位模式[4]。此功能允許低分辨率高速跟蹤或者更高分辨率支持更高精度。由于其大小、成本、精度與多功能性,此轉換器適用于高

性能軍用、商用及位置控制系統。

器件的運行需要一個+5V 電壓。轉換器有兩個對模擬地為±4V 電壓范圍的速度輸出(VEL A、VEL B),可用于替代轉速計。為兩條信道(/BIT A 與/BIT B)提供兩個內置測試輸出,以指示信號丟失(LOS)。

此轉換器由三大部分組成:輸入前端、誤差處理器和數字接口。前端對于同步器、分解器和直接輸入端有所不同。電子Scott-T 用于同步器輸入,分解器調節器用于分解器輸入,而正弦與余弦電壓跟隨器用于直接輸入端。這些放大器可以饋送高精度控制變壓器(CT)。CT 的另一個輸入是16 位數字角度ψ,其輸出是兩個輸入之間的模擬誤差角度或差分角度。CT 采用放大器、交換機、邏輯電路與電容器以查準率執行SINθ COSψ - COSθ SINψ =Sin(θ-ψ) 的三角函數計算。

與常規精密電阻器相比,這些電容器按查準率使用,以獲得更高精度。另外,這些電容器(與運算放大器一起用作計算元件)進行高速采樣,以消除偏移和運算放大器偏差。

DC 誤差處理進行積分運算,然后得到驅動電壓控制振蕩器的速度電壓。此VCO 與速度積分器結合在一起構成遞增積分器:一種2 型伺服反饋回路。

基準振蕩器

我們設計中采用的OSC-15802 功耗振蕩器也是DDC 公司提供。此器件適用于RDC、同步器、LVDT 和感應式傳感器應用[5]。頻率與振幅輸出可以分別由電容器和電阻器編程。輸出頻率范圍介于400Hz~10kHz 之間,輸出電壓為7Vrms。圖4 顯示了器件的方框圖。

圖3 – SD-14620方框圖(單信道)

圖4 – OSC-15802基準振蕩器方框圖

饋送到分解器和RDC 的振蕩器輸出用作基準信號。

FPGA的I/O電壓為3.3V,而RDC的電壓為5V。我們采用電壓收發器實現兩個器件之間的電壓兼容。

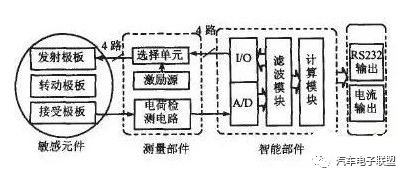

VIRTEX-5 FX30T FPGA 與RDC 接口

我們在設計中采用賽靈思Virtex?-5 FX30T FPGA [6]。FPGA 的I/O 電壓為3.3V,而RDC 的電壓為5V。因此我們采用電壓收發器來實現這兩個器件之間的電壓兼容。通過賽靈思提供的GPIO IP 核與FPGA 建立內部連接,如圖5 所示。

圖5 – RDC與Virtex-5 FPGA的接口(單信道)

為了簡單起見,圖5 僅顯示一條具有一個分解器接口的信道。 您可以在本文件隨附的賽靈思開發板描述(XBD)文件找到RDC 的引腳詳情以及FPGA 對應的專用引腳。 詳情見該文件第一部分。

器件驅動程序詳細說明

在本例中,F P G A 采用2 0 M H z 的外部輸入時鐘。此FPGA 具有一個運行頻率為200MHz 的PowerPC 440 硬核。RDC 的時序圖見圖6 與圖7。

圖6 – INHIBIT時序

圖7 – ENABLE時序

根據RDC 的時序圖,我們開發、測試并驗證了實際硬件的功能是否正確 [4]。器件驅動程序的實際編碼包含在單獨的XBD 文件中。根據時序圖,我們生成了用于回路的所需延遲。在200MHz 運行速率下進行處理時,每個計數都對應5 納秒的延遲。

器件驅動程序有三部分編碼:RDC 初始化、控制信號的生成及從RDC 信道A 的讀取、以及控制信號的生成及從RDC 信道B 的讀取。RDC 初始化是設置信號方向和缺省值的階段。例如,利用以下語句,信號方向將設置為從FPGA“輸出”到RDC。

下一個語句通過寫入“0x3”來設置16 位分辨率(即:拉高):

圖8 為編碼截屏。注:為了簡化,我們僅提供一條信道的編碼。

seXGpio_WriteReg(XPAR_INHIBIT_CH_A_

BASEADDR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=5;i++); //gives delay of 25 ns

XGpio_WriteReg(XPAR_ENABLE_LSB_

CH_A_BIT_BASEADDR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=5;i++);

XGpio_WriteReg(XPAR_INHIBIT_CH_A_

BASEADDR,XGPIO_DATA_OFFSET,0x00);

for(i=0;i<=2;i++);

XGpio_WriteReg(XPAR_ENABLE_LSB_CH_A_BIT_

BASEADDR,XGPIO_DATA_OFFSET,0x00);

for(i=0;i<=2;i++);

lsb_val=XGpio_ReadReg(XPAR_RDC_DATA_15_

TO_0_PINS_BASEADDR,XGPIO_DATA_OFFSET);

XGpio_WriteReg(XPAR_INHIBIT_CH_A_

BASEADDR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=5;i++);

XGpio_WriteReg(XPAR_ENABLE_LSB_CH_A_BIT_

BASEADDR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=25;i++);

XGpio_WriteReg(XPAR_INHIBIT_CH_A_

BASEADDR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=5;i++);

XGpio_WriteReg(XPAR_ENABLE_MSB_CH_A_BIT_

BASEADDR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=5;i++);

XGpio_WriteReg(XPAR_INHIBIT_CH_A_

BASEADDR,XGPIO_DATA_OFFSET,0x00);

for(i=0;i<=2;i++);

XGpio_WriteReg(XPAR_ENABLE_MSB_CH_A_BIT_

BASEADDR,XGPIO_DATA_OFFSET,0x00);

for(i=0;i<=2;i++);

msb_val=XGpio_ReadReg(XPAR_RDC_DATA_15_

TO_0_PINS_BASEADDR,XGPIO_DATA_OFFSET);

lsb_val=lsb_val & 0x00ff;

msb_val=msb_val & 0xff00;

rdccount_cha = msb_val | lsb_val;

XGpio_WriteReg(XPAR_INHIBIT_CH_A_

BASEADDR,XGPIO_DATA_OFFSET,0X01);

for(i=0;i<=5;i++);

XGpio_WriteReg(XPAR_ENABLE_MSB_CH_A_

BIT_BASEADDR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=20;i++);

圖8- RDC器件驅動程序編碼截屏

我們已經看到,角度傳感器可以幫助工程師創造更好的轉輪,進而設計出眾多更高效的機械裝置。分解器是一種尤為有用的角度傳感器,只要能夠與FPGA 正確配合和控制,其就能夠幫助工程師打造出無與倫比的機械裝置。

參考資料

1. 數據設備公司“同步器/ 分解器轉換手冊”。

2. John Gasking,“ 分解器數字轉換器:光電軸角編碼器簡單低成本替代方案” AN-263, 美國模擬器件公司

3. Walt Kester,“ 分解器數字轉換器” MT-030, 美國模擬器件公司

4. 數據設備公司SD-14620 系列數據手冊。

5. 數據設備公司OSC-15802 數據手冊。

6. 賽靈思Virtex-5 系列簡介

電子發燒友App

電子發燒友App

評論